#### SCHOOL OF ENGINEERING

## THE UNIVERSITY OF BIRMINGHAM

# SIMULATION COMBINED MODEL-BASED TESTING METHOD FOR TRAIN CONTROL SYSTEMS

By

#### YUEMIAO WANG

A thesis submitted to the University of Birmingham

for the degree of

DOCTOR OF PHILOSOPHY

12<sup>th</sup> March 2018

### UNIVERSITY<sup>OF</sup> BIRMINGHAM

#### **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

#### Abstract

A Train Control System (TCS) is utilised to guard the operational safety of the trains in railway systems. With rapid developments in modern railway systems, more and more modern TCSs have been developed to protect system operation. Consequently, guaranteeing that the functions of a TCS satisfy the designed specification requirements is essential to affirm that a developed TCS can be adopted. Functional testing is applied to test the System Under Test (SUT) in order to verify consistency between the SUT and specification requirements. Traditional functional testing in TCSs is mainly based on manually designed test cases, which are derived from experienced experts who are familiar with system functional design and testing. For newly built or updated TCSs, the test case generation process can take a long time. Manually-written test cases may miss some scenarios that should have been tested, even when prepared by an experienced test designer. Model-Based Testing (MBT) methods have been introduced into TCS functional testing to improve the efficiency and coverage of TCS testing. However, existing MBT methods cannot independently test complex SUTs because the model complexity generated by the SUT can exceed the computational limit of the computer due to state explosion.

To overcome the difficulties of applying MBT methods to test TCSs, the author introduces simulation combined MBT which combines an MBT method with simulation. To explain the MBT method introduced, related background knowledge is reviewed. Due to the limitations of the current functional testing and MBT methods, the author describes the research problem, and proposes methodology and development of the simulation combined MBT method, and

the validation and verification of the testing platform.

To prove the feasibility and effectiveness of the proposed MBT method and developed MBT platform, two case studies were undertaken. The test results indicate that the SUT Vehicle On-Board Controller (VOBC) complies with the specification requirements so that it passed the test. The two case studies prove that the developed MBT platform can be utilised to implement the functional testing of TCSs.

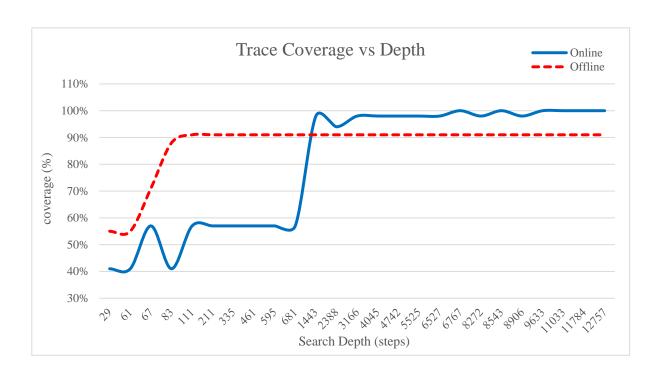

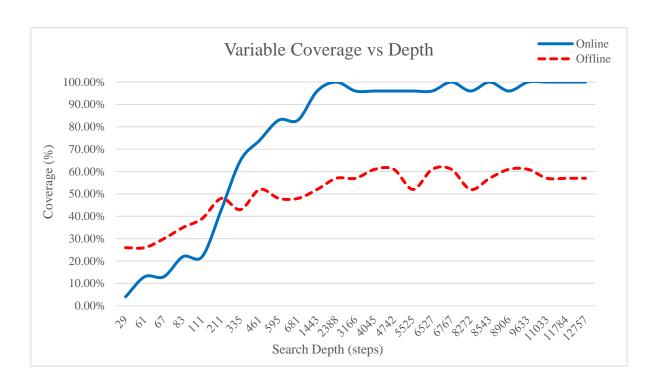

To prove that the MBT platform is effective in detecting errors in the SUT, validation and verification was undertaken, which included validation of the specification requirements and verification of the MBT platform. The verification results indicate that the MBT platform can cover more possible traces and variable values at the same search depth. The author also explores the possibilities of improving the coverage performance of the platform by improving its reachset coverage in key states. Various impact factors have been discovered to be effective in making the platform cover more possibilities in the same testing time.

#### Acknowledgements

I would like to give my sincere appreciation to my supervisors, Dr Lei Chen and Prof. Clive Roberts, for their consistent guidance, support and encouragement during my PhD study. With their help, I have moved firmly and in the correct direction toward my goal. The kind advice and patience they have given me has increased my confidence to overcome difficulties encountered in my PhD research. The knowledge they have given me has brought me benefits in my research and future career.

I would like to extend my gratitude to the Dr Jidong Lv who has selflessly shared his experience and knowledge with me, helping me successfully find the direction for my research. I am also grateful to Dr David Kirkwood who has shared his professional experiences and skills in Java programming and railway simulation with me. I would like to thank Miss Katherine Slater for her great help for proof reading my academic writing. Many thanks go to all the members of the Birmingham Centre for Railway Research and Education for their help and support.

I am also grateful to my wife, parents and father-in-law for their great love and understanding.

Your love is the greatest motivation in my life.

Finally, I would like to express sincere appreciation of my much-missed mother-in-law, an honest and selfless woman who lives in our hearts forever.

## **Table of Contents**

| Abstract                                                                          | ii |

|-----------------------------------------------------------------------------------|----|

| Acknowledgementsi                                                                 | V  |

| Table of Contents                                                                 | V  |

| List of Figuresi                                                                  | X  |

| List of tablesxii                                                                 | ii |

| Abbreviationsxi                                                                   | V  |

| 1 Introduction                                                                    | 1  |

| 1.1 Background                                                                    | 1  |

| 1.2 Motivation and Objectives                                                     | 0  |

| 1.3 Thesis Structure                                                              | 3  |

| 2 Literature Review of Functional Testing in Train Control Systems and Model-Base | d  |

| Testing Methods                                                                   | 5  |

| 2.1 Introduction to Train Control Systems                                         | 7  |

| 2.2 Traditional MBT Methods                                                       | 1  |

| 2.2.1 Introduction of Modelling Methods for MBT2                                  | 4  |

| 2.2.2 Introduction of Test Selection Criteria                                     | 4  |

| 2.2.3 Introduction of Test Tools                                                  | 9  |

| 2.3 Fu  | unctional Testing for Train Control Systems     | 40 |

|---------|-------------------------------------------------|----|

| 2.3.1   | Hardware-in-the-Loop testing for TCSs           | 40 |

| 2.3.2   | Model-Based Testing for TCSs                    | 45 |

| 2.3.3   | Summary                                         | 46 |

| 2.4 Re  | esearch Problem Description                     | 47 |

| 3 Mode  | lling for Simulation Combined MBT               | 49 |

| 3.1 Co  | omparison of Online MBT and Offline MBT         | 49 |

| 3.1.1   | Overview of Online MBT and Offline MBT          | 49 |

| 3.1.2   | Online MBT for TCS                              | 50 |

| 3.1.3   | Introduction of Simulation Combined MBT         | 55 |

| 3.2 Si  | mulation Combined MBT                           | 58 |

| 3.2.1   | Modelling for Online MBT                        | 59 |

| 3.2.2   | Conformance relation in MBT                     | 75 |

| 3.2.3   | Modelling method for Simulation Combined MBT    | 77 |

| 3.3 Su  | ımmary                                          | 88 |

| 4 Imple | mentation of Simulation Combined MBT            | 90 |

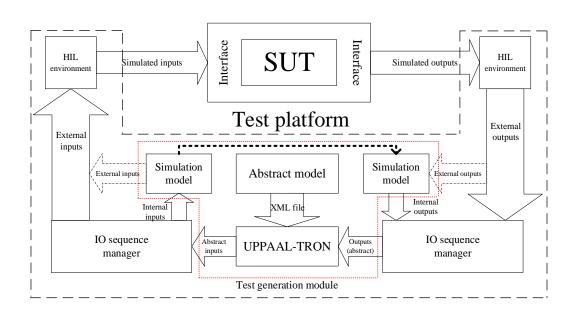

| 4.1 Ov  | verview of the Simulation Combined MBT Platform | 90 |

| 4.2 M   | odelling implementation of SUT                  | 91 |

|   | 4.2.1   | Modelling implementation of the Abstract Model   | 92  |

|---|---------|--------------------------------------------------|-----|

|   | 4.2.2   | Modelling implementation of the Simulation Model | 95  |

|   | 4.3 Te  | est Tool                                         | 98  |

|   | 4.4 I/O | O Sequence Manager                               | 101 |

|   | 4.5 HI  | IL Environment                                   | 105 |

|   | 4.6 Da  | ata flow in the Simulation Combined MBT Platform | 107 |

| 5 | Functi  | ional Testing Case Study on a CBTC System        | 110 |

|   | 5.1 Ca  | ase 1: Single Train Scenario                     | 110 |

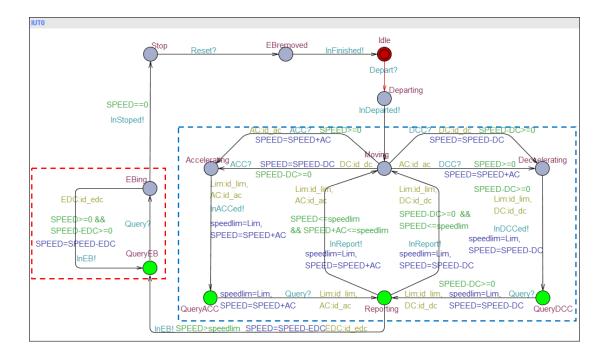

|   | 5.1.1   | Abstract Model                                   | 111 |

|   | 5.1.2   | Simulation Model                                 | 123 |

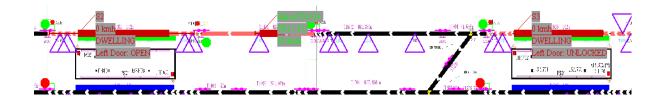

|   | 5.1.3   | HIL Environment                                  | 128 |

|   | 5.1.4   | I/O Sequence Manager                             | 132 |

|   | 5.1.5   | Testing Results                                  | 133 |

|   | 5.2 Ca  | ase 2: Multiple Train Scenario                   | 137 |

|   | 5.2.1   | SUT Models and the HIL Environment               | 139 |

|   | 5.2.2   | Testing Results                                  | 146 |

|   | 5.2.3   | Summary                                          | 153 |

|   | 5.2 Co  | onglusion                                        | 152 |

| 6 | Va                 | alidat  | ion and Verification                     | .154  |

|---|--------------------|---------|------------------------------------------|-------|

|   | 6.1                | Val     | idation of the Specification Requirement | . 156 |

|   | 6.                 | 1.1     | Abstract Model Validation                | .156  |

|   | 6.                 | 1.2     | Simulation Model Validation              | .166  |

|   | 6.2                | Eff     | ectiveness Verification                  | .167  |

|   | 6.2                | 2.1     | Mutation Testing                         | .167  |

|   | 6.2                | 2.2     | Reachset Conformance Relation            | .173  |

|   | 6.3                | Per     | formance Verification                    | .180  |

|   | 6                  | 3.1     | Trace Coverage and Variable Coverage     | . 181 |

|   | 6                  | 3.2     | Reachset Coverage in Key States          | . 184 |

|   | 6.4                | Sur     | nmary                                    | .199  |

| 7 | Co                 | onclu   | sion                                     | .202  |

|   | 7.1                | Coı     | nclusion                                 | .202  |

|   | 7.2                | Coı     | ntribution                               | .204  |

|   | 7.3                | Fut     | ure Work                                 | .205  |

| A | ppend              | dix: F  | Publications                             | .207  |

| D | - <b>f</b> - u - : | • • • • |                                          | 200   |

## **List of Figures**

| Fig 1 General steps of manual testing                                                   | 3 |

|-----------------------------------------------------------------------------------------|---|

| Fig 2 Efficiency comparison of different testing methods [30]                           | 6 |

| Fig 3 Classification of different types of testing                                      | 5 |

| Fig 4 Generalised system structure of ETCS, CBTC or other TCSs                          | 7 |

| Fig 5 Elements of an Event-B model                                                      | 5 |

| Fig 6 Schematic of finite state machines                                                | 7 |

| Fig 7 Schematic of TA model on the UPPAAL platform                                      | 8 |

| Fig 8: Schematic of statechart model on the Simulink platform                           | 9 |

| Fig 9 Complete model for the statechart model                                           | 9 |

| Fig 10 Schematic of finite state machines                                               | 6 |

| Fig 11 Classification of the testing process by different stages of system development4 | 1 |

| Fig 12 HIL testing platform for the OBU of CBTC systems [90]44                          | 4 |

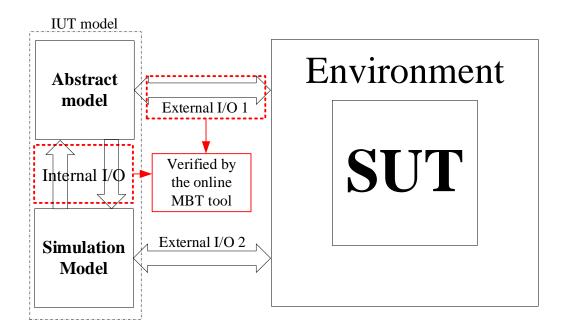

| Fig 13 Structure of traditional MBT and simulation combined MBT56                       | 6 |

| Fig 14 Schematic of an LTS                                                              | 1 |

| Fig 15 Schematic of a TIOTS                                                             | 6 |

| Fig 16 Schematic of the parallel configuration of two TIOTSs                            | 3 |

| Fig 17 Schematic of the conformance relation in MBT                                     | 6 |

| Fig 18 Schematic of an SCTIOTS                                                          | 9 |

| Fig 19 Modelling framework of simulation combined MBT85                                 | 5 |

| Fig 20 Architecture of the simulation combined MBT platform90                           | 0 |

| Fig 21 Example of the TA network model built in UPPAAL                                     | 92  |

|--------------------------------------------------------------------------------------------|-----|

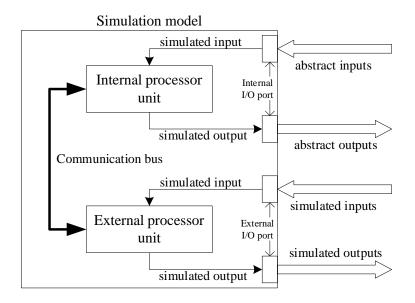

| Fig 22 Internal structure of implementation of the simulation model                        | 97  |

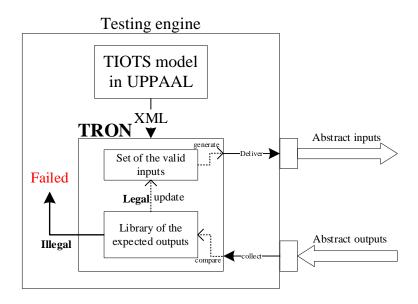

| Fig 23 Internal structure of the test tool UPPAAL-TRON                                     | 100 |

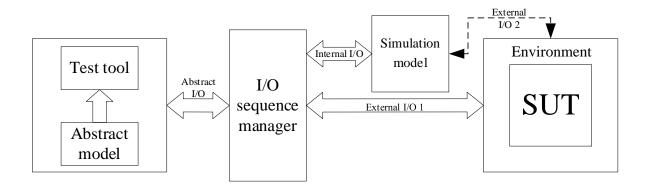

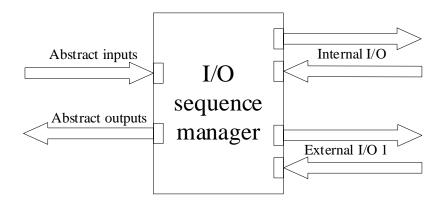

| Fig 24 Operation principle of the I/O sequence manager                                     | 102 |

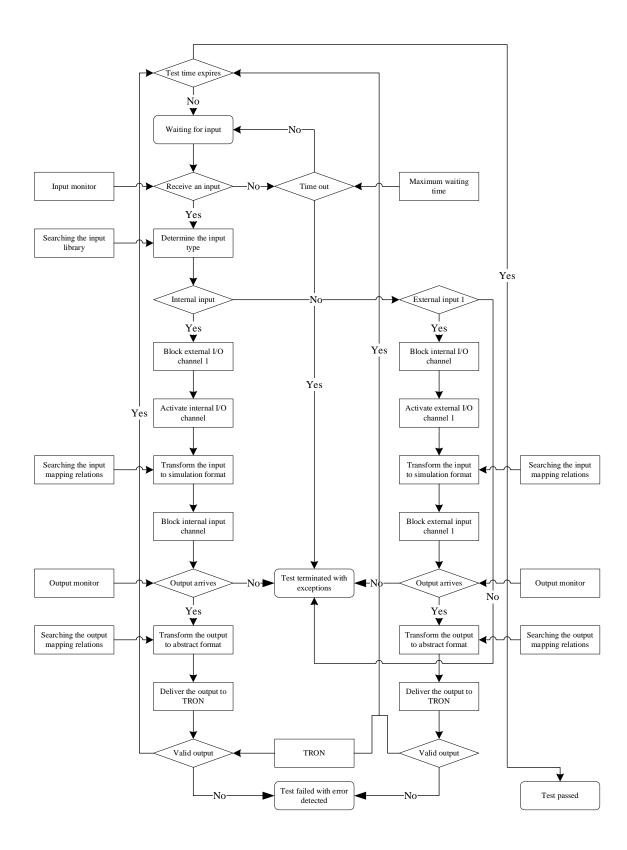

| Fig 25 Flow chart of the functional logic realised by the I/O sequence manager             | 104 |

| Fig 26 Schematic of the testing scenario for a single train                                | 106 |

| Fig 27 Operating principle of the simulation combined MBT platform                         | 108 |

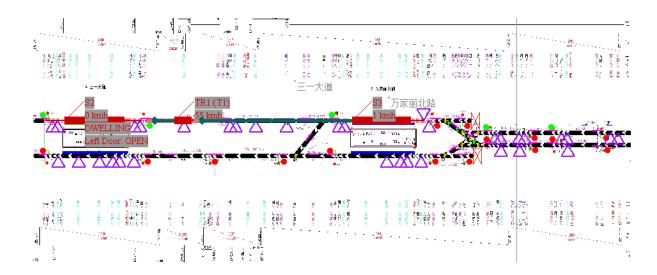

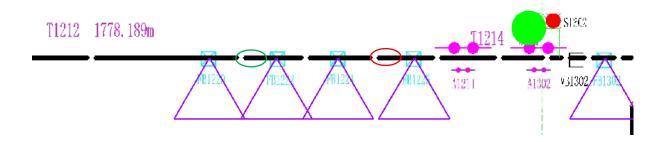

| Fig 28 CAD map of Changsha Metro Line 5                                                    | 111 |

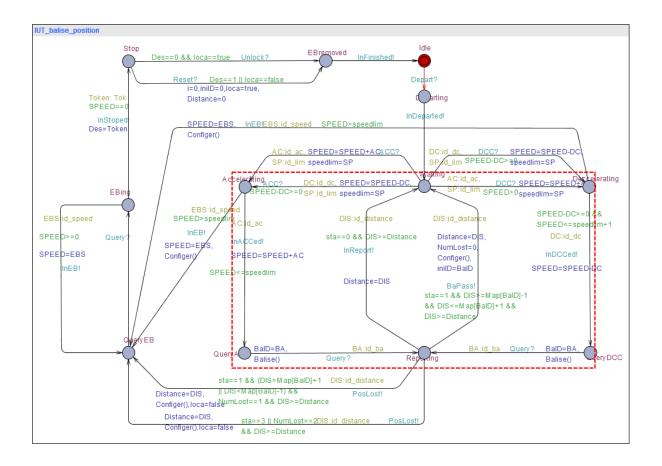

| Fig 29 TA model of the SUT for single-train scenario                                       | 114 |

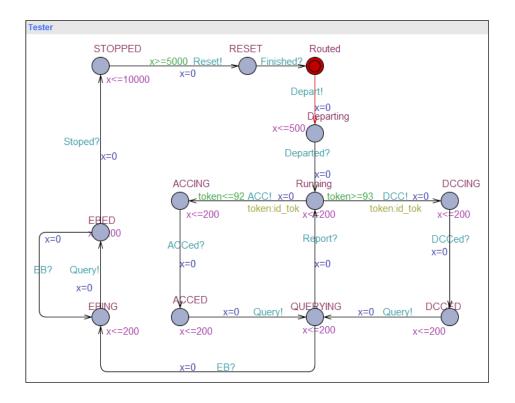

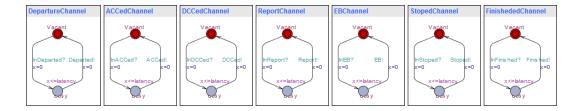

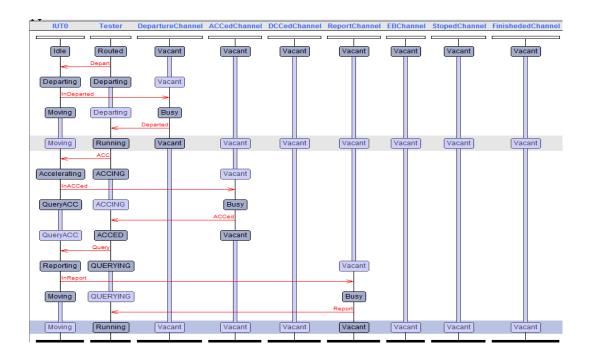

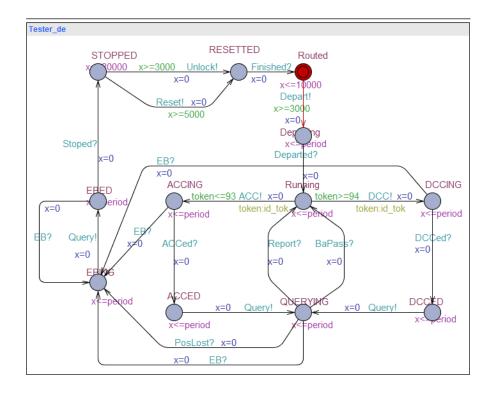

| Fig 30 TA model of the tester for single-train scenario                                    | 119 |

| Fig 31 TA model of the communication channels for single-train scenario                    | 121 |

| Fig 32 Schematic of a trace generated from the TA model of the specification               | 123 |

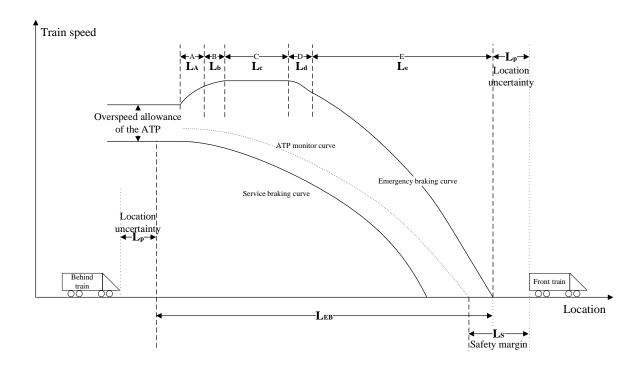

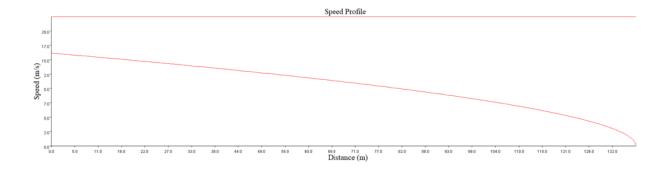

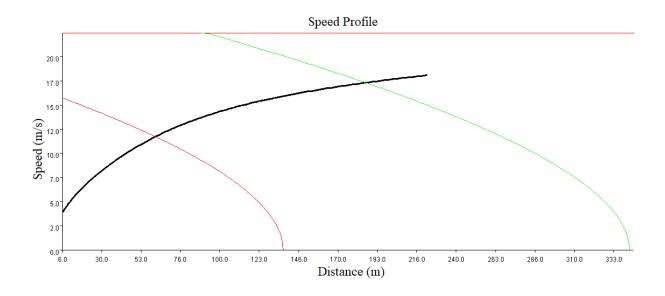

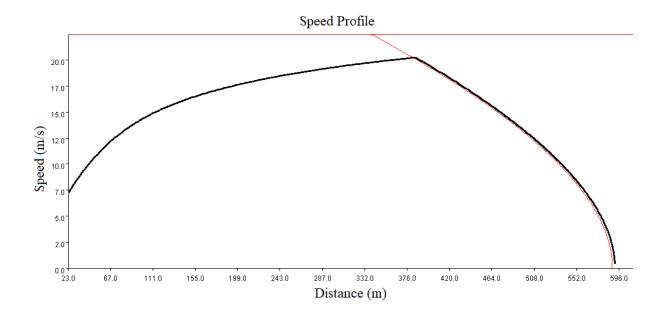

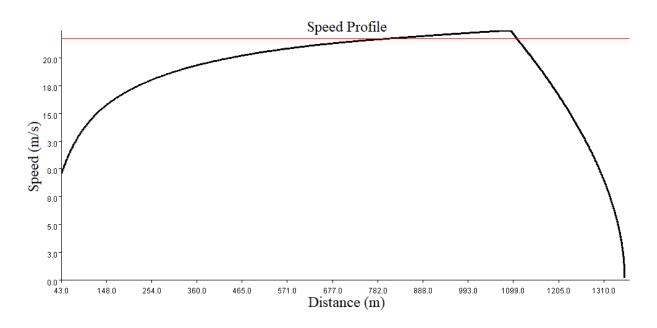

| Fig 33 Calculation principle of braking curves                                             | 124 |

| Fig 34 Illustration of the speed limit calculation modelled in the simulator               | 125 |

| Fig 35 Illustration of the overspeed protection function modelled in the simulator         | 126 |

| Fig 36 Overspeed scenario: exceeding the speed limit generated by MA                       | 127 |

| Fig 37 Overspeed scenario: exceeding the speed limit generated by line speed limit         | 127 |

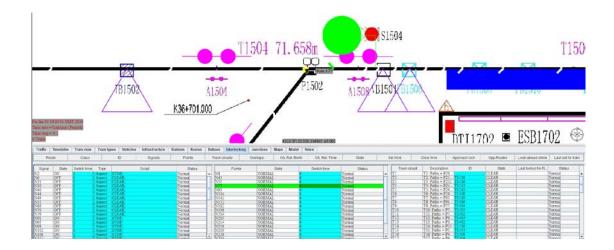

| Fig 38 Schematic of the vehicle model in the microscopic railway simulator                 | 128 |

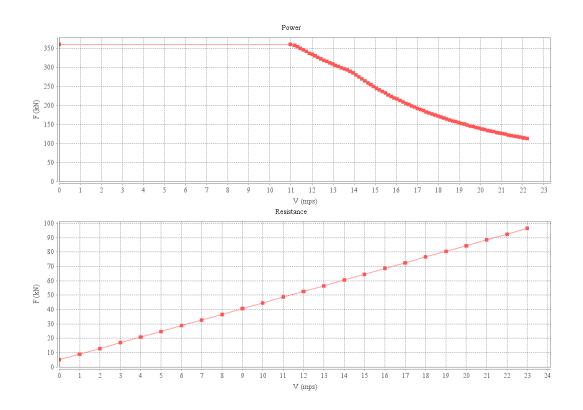

| Fig 39 Traction power and resistance power along with various speeds                       | 129 |

| Fig 40 Schematic of a balise-passing event in the simulator                                | 130 |

| Fig 41 Schematic of signals, axle counters and points of the interlocking in the simulator | 132 |

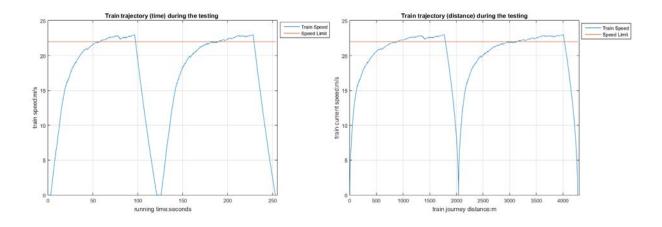

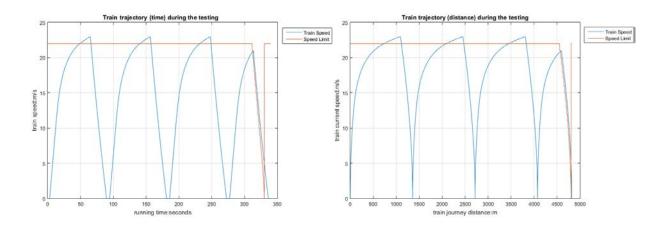

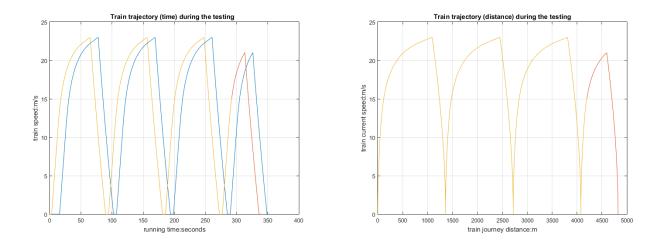

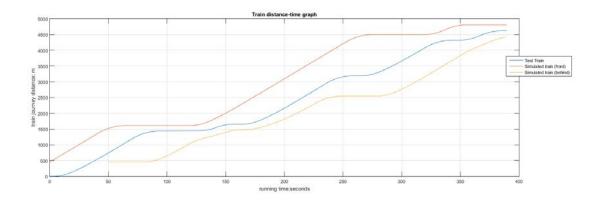

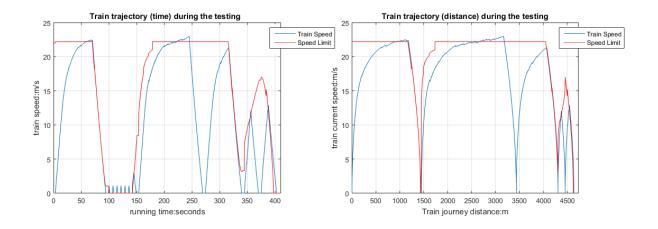

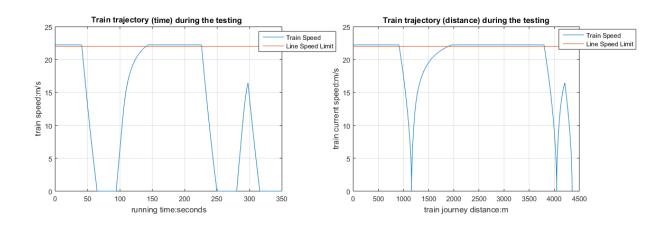

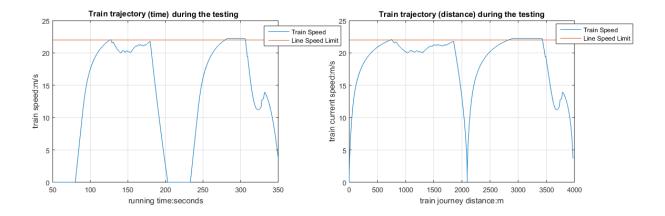

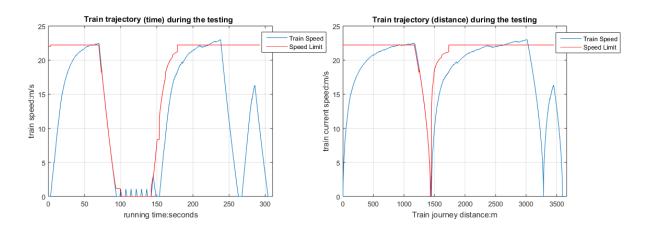

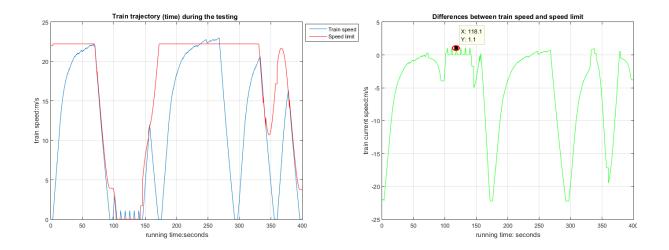

| Fig 42 Train trajectory during the testing process: 93% acceleration                              |

|---------------------------------------------------------------------------------------------------|

| Fig 43 Train trajectory during the testing process: 100% acceleration                             |

| Fig 44 Merged train trajectory run 24 times: 100% acceleration                                    |

| Fig 45 Fragment of the testing log file                                                           |

| Fig 46 Schematic of multiple-train scenario                                                       |

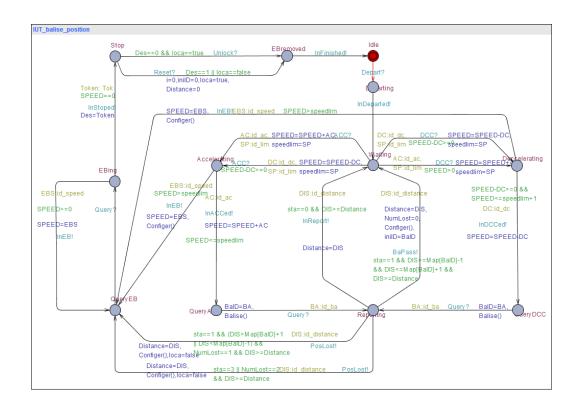

| Fig 47 TA model of the SUT for multiple-train scenario                                            |

| Fig 48 TA model of the tester for multiple-train scenario                                         |

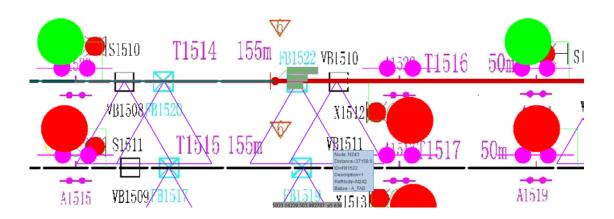

| Fig 49 Schematic of the testing environment for train location function                           |

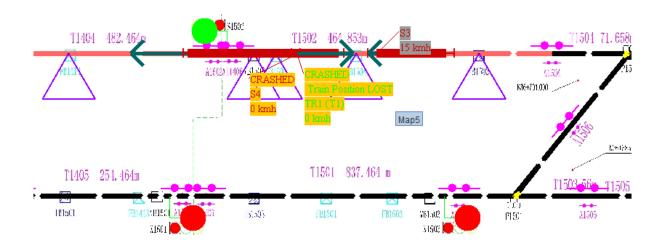

| Fig 50 Schematic of the crash detection function                                                  |

| Fig 51 Distance–time graph of the three trains in the network                                     |

| Fig 52 Trajectory graphs of the SUT train in one loop of testing                                  |

| Fig 53 Trajectory graphs of the front train S2 in one loop of testing149                          |

| Fig 54 Trajectory graphs of the behind train S3 in one loop of testing149                         |

| Fig 55 Trajectory graphs of the SUT train for the example of EB due to lost train location $.150$ |

| Fig 56 Schematic of scenario in which a third EB is triggered                                     |

| Fig 57 Correspondence relations of balise ID between the abstract model and HIL                   |

| environment                                                                                       |

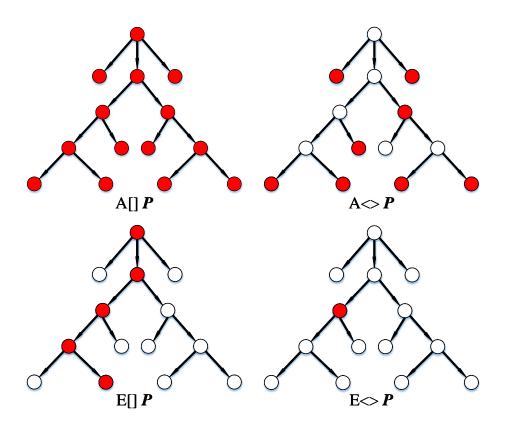

| Fig 58 Schematic of the four formulae supported by UPPAAL                                         |

| Fig 59 Summary of all verified safety and liveness properties                                     |

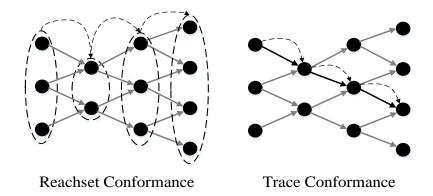

| Fig 60 Comparison between reachset conformance and trace conformance                              |

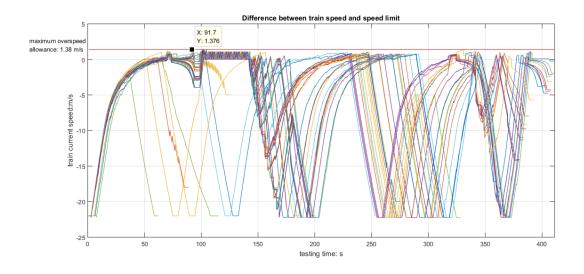

| Fig 61 Example of differences between train speed and speed limit                                 |

| Fig 62 Verification results for the reachset conformance relation                                      |

|--------------------------------------------------------------------------------------------------------|

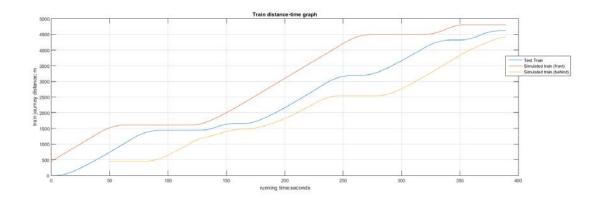

| Fig 63 Example of a distance–time graph for verification                                               |

| Fig 64 Trace of coverage tendency with search depth                                                    |

| Fig 65 Variable coverage tendency with search depth                                                    |

| Fig 66 TA model of the SUT in multiple-train scenario                                                  |

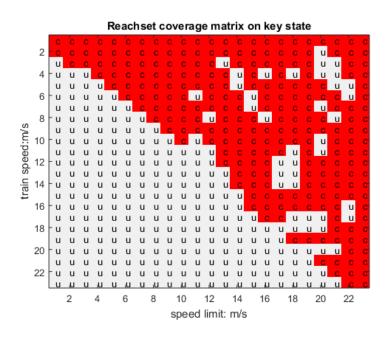

| Fig 67 Coverage matrix of testing platform run for 5000 seconds                                        |

| Fig 68 Maximum number of valid combinations of train speed and speed limit                             |

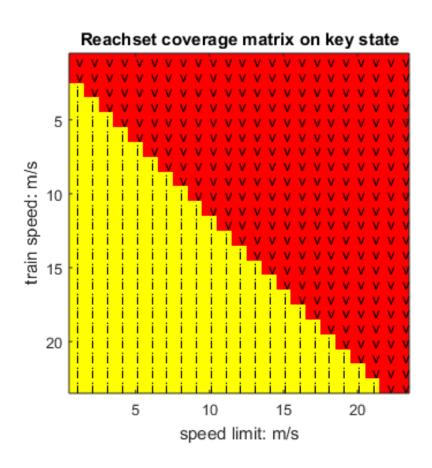

| Fig 69 Coverage matrices for different testing times (1000 seconds on the left and 50000               |

| seconds on the right)                                                                                  |

| Fig 70 Relation between reachset coverage and testing time                                             |

| Fig 71 Reachset coverage under different train interaction intensities (weak interaction on the        |

| left and strong interaction on the right)                                                              |

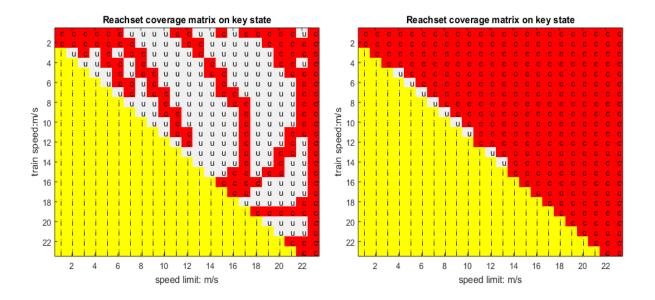

| Fig 72 Reachset coverage matrix for the maximum percentage of 97%                                      |

| Fig 73 Train trajectory for verifying the missed combination ' <b>SPEED</b> =5, <b>speedlim</b> =4'195 |

| Fig 74 Verification result for the missed combination 'SPEED=5, speedlim=4'195                         |

| Fig 75 Reachset coverage strength in key states for every combination                                  |

| Fig 76 Planar figure of the 3D bar graph of coverage strength                                          |

| Fig 77 Improved coverage strength with a lower top speed of the front train 199                        |

## List of tables

| Table 1 Testing time for each version of testing for each testing method [30]         | 6   |

|---------------------------------------------------------------------------------------|-----|

| Table 2 Comparison of ETCS and CBTC systems                                           | 19  |

| Table 3 Summary of formal modelling methods                                           | 34  |

| Table 4 Summary of test tools for model-based testing [85]                            | 40  |

| Table 5 Summary of the abstract input and output actions                              | 120 |

| Table 6 Summary of the parameters in the vehicle model                                | 129 |

| Table 7 Summary of I/O actions on the internal I/O channel and external I/O channel 1 | 133 |

| Table 8 Timetables for simulation trains built in the microscopic railway simulator   | 144 |

| Table 9 Summary of mutation testing results                                           | 168 |

| Table 10 Summary of the verification of missed combinations                           | 196 |

#### **Abbreviations**

ATP Automatic Train Protection

ATS Automatic Train Supervision

BTM Balise Transmission Module

CBI Computer-Based Interlocking

CBTC Communication-Based Train Control

CCS Calculus of Communication System

CRRC China Railway Rolling Stock Corporation

CSP Communicating Sequential Processes

CTC Centralised Traffic Control

DCS Data Communication System

DMI Driver Machine Interface

DR Data Recorder

EB Emergency Brake

ETCS European Train Control System

EVC European Vital Computer

FFFIS Form Fit Functional Interface Specification

FSM Finite State Machine

GSM-R Global System for Mobile Communications – Railway

HIL Hardware-in-the-Loop

HOL Higher-Order Logic

IATP Intermissive Automatic Train Protection

*ioco* Input–output conformance relation

IOTS I/O Transition System

IUT Implementation Under Test

JML Java Modelling Language

JRU Juridical Recording Unit

KVC Kernel Vital Computer

LEU Lineside Electronic Unit

LTS Labelled Transition Systems

MA Movement Authority

MBT Model-Based Testing

MSC Message-Sequence Charts

OBRU On-Board Radio Unit

OBU On-Board Unit

OCL Object Constraint Language

ODO Odometer

PN Petri Net

RBC Radio Block Centre

RTM Radio Transmission Module

SCTIOTS Simulation Combined Model-Based Testing

SIL Safety Integration Level

sioco Symbolic input–output conformance relation

SUT System Under Test

TA Timed Automata

TC Track Circuit

TCC Train Control Centre

TCR Track Circuit Reader

TCS Train Control System

tioco Timed input–output conformance relation

TIA Transponder Interrogator Antennae

TIMS Train Information Management System

TIOTS Timed I/O Transition System

TIU Train Interface Unit

TOD Train Operator Display

UML Unified Modelling Language

UNISIG Union of Signalling Industry

VDM Vienna Development Method

VOBC Vehicle On-Board Controller

WLAN Wireless Local Area Network

ZC Zone Controller

#### 1 Introduction

#### 1.1 Background

The Train Control System (TCS) is a wide-ranging concept with numerous subsystems for different control objectives, such as guaranteeing system safety, improving efficiency and capacity, and optimising energy consumption [1-3]. Among all these subsystems, the TCS is one of the most essential because it is the key element to guaranteeing a system's operational safety and protecting the system from potential dangerous situations such as collision or derailment [4, 5]. Since the railway is utilised to carry a large quantity of passengers or cargo, any dangerous situation can lead to disastrous consequences and huge economic losses. With the same purpose for different uses, there is much variation in the signalling systems adopted in different countries, such as the European Train Control System (ETCS) which is a unified standard and widely adopted in the railway systems of many European countries [6, 7], and the Communication-Based Train Control (CBTC) system which has been widely adopted in many countries.

Since metro lines are usually less complicated than mainline railways in terms of track layout, rolling stock and timetables, moving blocks has been realised in CBTC systems to improve the capacity of metro operations [8, 9]. Different from the ETCS standard which have unified standards determined by authoritative organisations, CBTC system composition varies for different manufacturers, including different system components, structure and performance. Despite ETCS and CBTC being different from each other in many different aspects, they still share a lot in common. For example, the fundamental system structure of each contains

trackside equipment, train-borne equipment, and communication systems, which are used to guarantee the safety of train movements with determined train movement authority (MA) [10, 11]. Based on data transmission between lineside equipment and train-borne equipment via communication channels [12], train movement safety is guaranteed by cooperation of these essential elements, though the cooperation modes may be different in different standards of TCS [13]. Therefore, it is possible to apply a unified method to test different types of signalling system.

As one of the most essential protectors of railway systems operation, TCSs are required to contain no safety-relevant errors that could lead the system operation into dangerous situations [14]. As a result, TCSs consist of a series of Safety Integration Level (SIL) 3 and SIL 4 [15] subsystems and components, which makes a TCS a typical safety-critical system which must be fail-safe [16]. Therefore, functional testing plays an important role in verifying that all safety-related functions in TCSs are correctly designed and precisely realised. To achieve this goal, test cases are written to check against the system specification requirements, aiming to determine whether inconsistencies exist between the system specification and the System Under Test (SUT) [17]. To implement testing, test cases need to be drafted by experts in the testing field, who also need to be experienced in signalling system design. Based on this understanding of a certain signalling system, test cases are written to include a series of different scenarios in which failure or dangerous situations could happen during system operation. This procedure requires the test case drafter to completely master the whole system operation process so that he or she knows every function which needs to be tested. After test

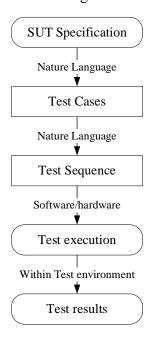

case drafting is finished, the test cases must be translated into a set of test sequences which describe what actually happens in the testing procedure. Finally, the last step is to execute the test sequences generated to determine whether the SUT behaviour complies with the system specification requirements. The test process can be time-consuming because most steps in the process are performed manually, as shown in Fig 1:

Fig 1 General steps of manual testing

According to Fig 1, test cases are written in natural language, according to the specification requirements of the SUT and the expertise of the tester. The test cases are then manually translated into test sequences which are also in natural language, describing the testing steps which happen in the testing process. To execute the testing sequence and eventually obtain the testing results, the testing sequences have to be transformed into a format which is recognisable by the SUT software or hardware; this can be realised by specific interfaces which can realise the translation between different types of data. Finally, the tests are implemented in a valid testing environment, and the testing results are obtained. Due to the

SUT specification requirements, the test case and the test sequence are all in natural language which is understandable for humans but is difficult for computers to process; testing efficiency relies significantly on the person who designs and implements the testing. Therefore, it is extremely difficult to improve testing performance, due to the human factor. Even worse, due to the complexity of TCSs, manually drafted test cases can miss essential testing steps and cause error omissions, even with experienced testers. If the system specification is modified in the system development stage, the test case must be accordingly modified to comply with the specification requirements, which means the test sequences and test executions must be modified as well. Without the assistance of computers, the modification process can take an extremely long time so that the extendibility of the testing can be reduced. Overall, manually oriented testing has become less appropriate for modern TCSs due to the growing demands for quicker product delivery with high quality [18].

Faced with the conflicts between the manual testing method and the requirements for functional testing of TCSs, automatic testing methods have been taken into the field from software testing [19]. Unlike manual testing, automatic testing methods can automatically generate test cases based on the formalised specification requirements of the SUT so that testing quality and duration can be significantly reduced with the assistance of computers [20, 21]. As cutting-edge technology in the testing field, automatic testing has a wide range of realisation methods for different testing objectives, including stress testing [22, 23], usability testing [24], performance testing [25], functional testing, etc.

To verify the functional correctness of the system, which is one of the key tasks in the testing

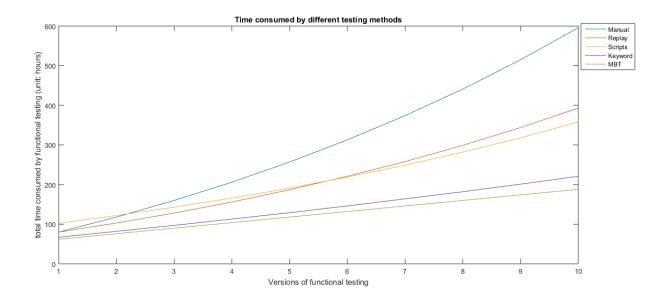

of TCSs, Model-Based Testing (MBT) is one of the most common automatic testing methods for functional testing [26, 27]. To implement MBT, the specification requirements need to be formally described by a specification model which is readable by a computer. The specification model is then analysed by the computer with integrated algorithms, and corresponding test cases are generated based on the properties that need to be verified. Compared with the manual testing method, the MBT method has several advantages which mean it can replace the current manual testing method utilised in TCS testing. Firstly, MBT test generation can be achieved as soon as the specification requirements are formally presented, which means the whole testing process period can be significantly shortened. Compared with test cases which are written in natural language, the formal models that describe an SUT according to its specification requirements are more precise because formal language is more logical and mathematical and has less ambiguity. This is extremely important for the testing of safety-critical systems such as TCSs because even a slight misunderstanding of the specification requirements can result in an incorrect testing verdict, leading to serious consequences [28]. That is why more and more manual testing adopts formal language to describe the specification requirements of the SUT, even though the test cases are still executed manually. Secondly, with MBT test generation algorithms based on formalised specification requirements, coverage of the generated test cases can be conveniently calculated and improved by the algorithm so that testing efficiency and coverage can be dramatically improved [29]. The research results of Utting and Legeard [30] show the significance of automating the process of functional testing.

| A ativita                       | Total testing time |        |        |         |     |  |  |

|---------------------------------|--------------------|--------|--------|---------|-----|--|--|

| Activity                        | Manual             | Replay | Script | Keyword | MBT |  |  |

| Test design                     | 50                 | 50     | 50     | 50      | 0   |  |  |

| Modelling                       | -                  | -      | -      | -       | 30  |  |  |

| Initial configuration           | -                  | -      | 50     | 15      | 30  |  |  |

| Initial test execution          | 30                 | 30     | 2      | 2       | 2   |  |  |

| Total testing time by version 1 | 80                 | 80     | 102    | 67      | 62  |  |  |

| Total testing time by version 2 | 118                | 103    | 122    | 82      | 76  |  |  |

| Total testing time by version 3 | 160                | 128    | 143    | 97      | 90  |  |  |

| Total testing time by version 4 | 206                | 156    | 166    | 113     | 104 |  |  |

| Total testing time by version 5 | 257                | 187    | 191    | 129     | 118 |  |  |

| Total testing time by version 6 | 313                | 221    | 219    | 146     | 132 |  |  |

| Total testing time by version 7 | 374                | 258    | 249    | 164     | 146 |  |  |

| Total testing time by version 8 | 441                | 299    | 282    | 182     | 160 |  |  |

| Total testing time by version 9 | 515                | 344    | 318    | 201     | 174 |  |  |

| Total testing time by version   | 596                | 393    | 358    | 221     | 188 |  |  |

| 10                              |                    |        |        |         |     |  |  |

Table 1 Testing time for each version of testing for each testing method [30]

Fig 2 Efficiency comparison of different testing methods [30]

As revealed by Table 1 and Fig 2, the total test duration increases along with an increasing

number of versions, where more and more functions are included in the testing so that more and more test cases need to be generated and executed. Obviously, for the initial versions, the duration of the five testing methods do not differ a lot compared with the following versions. However, the growth rates of manual testing, replay testing [31] and script-based testing [32, 33] are much greater than those of keyword-driven testing [34] and MBT. As a result, when the testing versions are updated, which means that more and more functions are tested, keyword-driven testing and MBT can save a large amount of testing time compared to other testing methods. Since MBT is the only testing method that can automate the test design process, its advantages against keyword-driven testing appear when more and more functions need to be tested. For complex systems such as TCSs, the number of functions under test can be high so that MBT can play its strengths when testing such kinds of system. Furthermore, in manual testing, a single test sequence is assigned to one test case to ensure that the corresponding function in the SUT is covered by the testing. However, there can be a lot of different testing sequences contained in the same test case, which means that in some instances, one cannot stand for all of them. In manual testing, there are too many remaining valid test sequences to be fully covered by human design. Since formal models can be understood by computers, a computer can find out all the valid test cases from the specification requirements, and all the test sequences based on the test cases generated. As a result, coverage of the testing can be significantly improved with MBT test generation algorithms. Furthermore, the test cases generated can be easily transformed into test sequences, which can be used to realise automatic test execution with a specified interface

connecting the real SUT and the test tool. Consequently, the test execution efficiency can be greatly improved without any risk of affecting the accuracy of the testing results. Lastly, the generation and execution processes in MBT testing are all dependent on computer algorithms, which means that error omission caused by human factors is isolated from the testing procedure. In MBT testing, the only element which needs to be develop by humans is the formal model of the SUT behaviour which is also known as the test oracle [35]. Provided the formal model is correctly built according to the specification requirements of the SUT, it promises to obtain a convincing testing result which determines whether SUT behaviour complies with the given specification requirements. Overall, MBT is more eligible than manual testing for testing safety-critical systems such as TCSs.

Although MBT has been rapidly developing and has been proven to be suitable for testing large-scale systems including software and hardware, it is still challenging to apply MBT for testing industrial-sized systems with a high degree of complexity, such as TCSs which contain many subsystems and components with complex interactions and many nondeterministic situations. As one of the key steps in MBT methods, formal modelling is relatively difficult compared to manual test generation, especially when dealing with complex modelling subjects such as TCSs. Since formal language does not describe the modelling subjects in a natural manner which can be understood by most people, formal modelling can take longer than manual test case drafting, even for an experienced tester. When the modelling subjects are of industrial size, they can consist of numerous components with intricate structures for realising various functions by series of interactions, which exponentially increase the

still be too complex to be processed by computers in an acceptable time frame. When a formal model becomes too complex, which means that there are too many possibilities contained in it, state explosion may happen when applying test generation and execution algorithms so that the computational resources of computers can be exhausted, which means the MBT cannot be applied to test industrial-sized SUTs without controlling the formal modelling scales. Different from manual testing methods which specifically emphasise sequences of valid inputs and corresponding expected outputs, the modelling methods of MBT model SUTs in a format of different types of formal expression, which is not understandable for nonexperts. Therefore, it is difficult for an inexperienced tester to determine whether the specification model correctly presents every essential element involved in the specification requirements of the SUT. However, without correct formal models, the test cases derived can be invalid or inaccurate for use in testing the SUT, so that the testing results obtained are meaningless.

Compared with MBT methods, manual testing methods are mostly straightforward, conforming to natural human habits of testing, and are understandable for most testers who are familiar with the functional characteristics of the SUT. Unlike formal models, the correctness of which needs to be verified by relevant techniques such as model-checking [36, 37] and theorem proven, test cases for manual testing are drafted by the experts from authoritative organisations such as UNISIG, which takes charge of standardising the Form Fit Functional Interface Specification (FFFIS) of all subsystems and key components contained in the ETCS system, and the corresponding test cases and test facility for those test

specifications. With technical support from the professional company members of UNISIG such as Alstom, Ansaldo, Bombardier, Siemens and Thales, the correctness of the test cases is convincing. That is why the testing of TCSs still depends mainly on manual testing, though it relies more and more on formal methods such as MBT.

#### 1.2 Motivation and Objectives

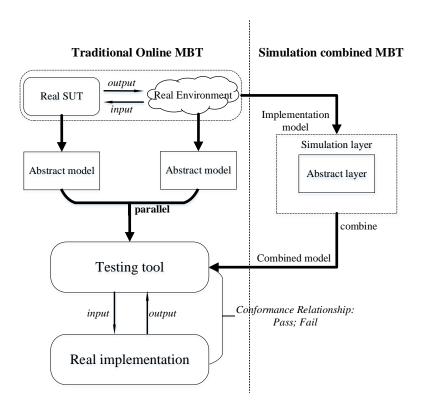

To address the challenge of applying MBT methods in TCS testing, the limitations of formal modelling methods must firstly be overcome. Therefore, the author has developed a novel MBT method called simulation combined MBT, which overcomes the aforementioned difficulties of utilising the MBT method to test complex systems. In contrast with traditional MBT methods which describe SUT behaviour in a single formal language or in multi-layer formal language, simulation combined MBT obtains the SUT model from formal modelling combined with simulation, targeting two types of system behaviour in two models. To decrease the modelling difficulties as well as to control the model complexity under an acceptable level, the SUT model is divided into two models, the abstract models in charge of abstract and discrete system behaviour, and the simulation model in charge of concrete and continuous system behaviour. Based on the two-model-combined structure, the system behaviour for relatively complex SUTs can be modelled entirely without the risk of state explosion. Furthermore, it simplifies the process of building formal models by moving most of the continuous behaviour, which is difficult to model in formal language, from formal models into simulation models.

Compared with formal language, simulation is more applicable for describing continuous behaviour from a macroscopic view because of the flexible features of simulation. For a complex system with hybrid characteristics, such as a TCS, combining discrete condition-switching, such as the transition mode of the On-Board Unit (OBU), and continuous variable changes, such as the train speed varying in operational procedures, the two-model-combined structure takes advantage of both formal modelling, which is adept at describing discrete transition processes, and of simulation, which is good at depicting continuous variation processes. With the combination of both modelling methods, the modelling difficulties of the SUT and the processing difficulties of the SUT models are together reduced, which significantly increases the feasibility of applying MBT methods in complex system testing. Since the modelling method is different from those of traditional MBT, the test tool which is utilised to generate test sequences based on the analysis of formal models cannot be directly adopted in simulation combined MBT. Therefore, a customised interface has been developed for the application of an online MBT test tool, allowing the online testing of complex systems to be realised.

In the field of MBT, online testing and offline testing are two contrary concepts of different kinds of testing implementation technique; offline testing generates test cases then executes them, while online testing generates and executes test cases simultaneously. Online testing can deal with nondeterminism contained in the formal model, but performs worse than offline testing in checking strict time restrictions because the test cases cannot be generated in time for execution when the formal model is too complex. By comparison, offline testing cannot

deal with nondeterminism contained in the formal model, but it is good at checking strict time restrictions, and the generation and execution processes are separated. Since a TCS is a typical nondeterministic system with a high degree of complexity, the author aims to implement online MBT testing based on the simulation combined MBT method introduced, considering testing accuracy and efficiency, which leads to the following objectives:

- Discuss the main tasks of testing the functions of a TCS.

- Based on the discussion, explore the feasibility of applying MBT to test TCSs.

- According to the exploration results, develop a simulation combined MBT which is suitable for testing TCSs.

- With application of the simulation combined MBT, build up an online MBT testing

platform which can be applied to test different types of TCS in various railway

networks.

- Implement online testing based on a case study of a TCS utilised in real railway systems and draw an eventual testing verdict.

- Verify the testing results obtained, determine the effectiveness of the simulation combined MBT, analyse whether testing performance is better than that of existing testing methods.

With all the objectives achieved, the author expects that simulation combined MBT can be applied to test TCSs and other industrial-sized systems with complex functions and structures. With verification of the testing results, the online MBT platform developed by the author is expected to obtain better performance in terms of testing correctness, functional coverage and

time efficiency.

#### 1.3 Thesis Structure

The thesis is presented with the following structure:

#### • Chapter 2:

Different types of TCSs, which are the SUTs, are introduced. Traditional MBT methods and traditional functional testing of TCSs are introduced. Based on the review, the research problem is formulated.

#### • Chapter 3:

The reason for choosing online MBT is explained. Evolved from the traditional modelling method for online MBT, the Simulation Combined Timed I/O Transition System (SCTIOTS) modelling theory is developed with formula derivation. Based on SCTIOTS, simulation combined MBT methodology is proposed.

#### • Chapter 4:

The method of implementing simulation combined MBT is introduced by developing a simulation combined MBT platform. The essential components of the platform are introduced, including the modelling tools, test tool, I/O sequence manager and Hardware-in-the-Loop (HIL) environment. The architecture of the platform is explained at the end of the chapter.

#### • Chapter 5:

Two case studies are undertaken to prove the feasibility of the proposed testing method

and developed platform. The first case concentrates on explaining the developed components of the simulation combined MBT platform. The second case concentrates on testing the overspeed protection function and the train location function of an SUT Vehicle On-Board Controller (VOBC). Testing results are recorded and analysed in both cases.

#### • Chapter 6:

The effectiveness and performance of the simulation combined MBT platform are verified, including validation of the specification requirements, verification of the effectiveness of the testing platform, and verification of the performance of the testing platform. Impact factors of test efficiency and quality are explored at the end of the chapter.

#### • Chapter 7:

The conclusion and contribution of the thesis are summarised. Future work is presented at the end of the chapter.

## 2 Literature Review of Functional Testing in Train Control Systems and Model-Based Testing Methods

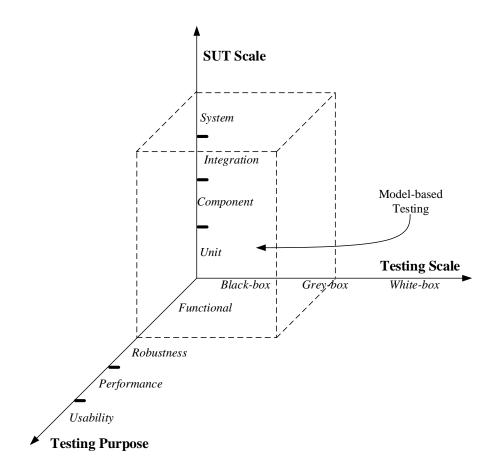

Testing is a broad concept with definitions that can vary from field to field, and each one can be quite different from the rest when considering different testing purposes and testing scales. Therefore, before MBT can be applied to test an SUT, three essential elements, the scale of the SUT, the scale of the testing and the purpose of the testing, must be specified to determine the appropriate type of test. Evolved from the model defined by Utting and Legeard [30], the concept of different types of testing is generally defined by Fig 3:

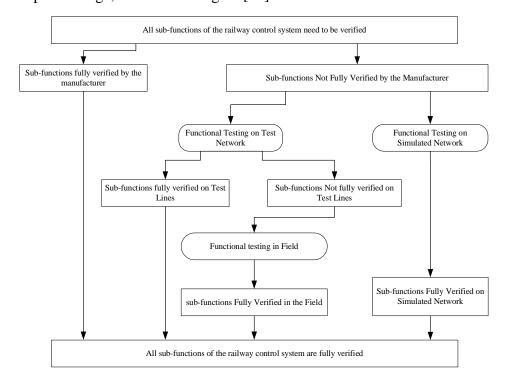

Fig 3 Classification of different types of testing

As depicted in Fig 3, three key indices profile different types of testing by determining the testing purpose, testing scale and SUT scale of testing. For testing scale, black-box testing means that the tester does not have the access required to know the internal behaviour of the SUT, while white-box testing means that the tester does have access to the internal behaviour of the SUT [38]. That is to say, white-box testing aims to test the internal behaviour of the SUT, which means that the tester needs to understand its internal operating principles [39]. In grey-box testing, which is related to black-box testing and white-box testing, the tester only has partial knowledge of the internal SUT behaviour, so that it can have the characteristics of both black-box testing and white-box testing and can be a richer approach [40]. For SUT scale, testing has different meanings when it is implemented at different levels of SUTs, including unit testing, component testing, integration testing and system testing. Obviously, it is difficult to distinguish these four levels in complex systems with a complicated structure, such as TCSs which consist of a series of subsystems, components and units. For such a system, it necessary to define the boundary between the internal and external layers of the SUT, without necessarily defining which level the testing belongs to. In testing purposes which directly determine the testing type, testing is classified into different categories, including functional testing, robustness testing, performance testing and usability testing, each of which refers to corresponding testing methods. As mentioned above, functional testing aims to verify the system's functional behaviour which is designed and developed within the system specification requirements so that it usually connects with black-box testing. As conclusively indicated by Fig 3, the relevant fields of MBT are restricted inside the dotted cube, indicating

that MBT is designed and implemented for functional testing with a black-box or grey-box testing scale, though it can be adopted to test any level of the SUT. It is worth noting that the dotted cube does not mean a strict restriction, which means that the MBT can still be utilised for other testing purposes, such as performance testing and robustness testing. However, functional black-box testing is the main application scenario.

#### 2.1 Introduction to Train Control Systems

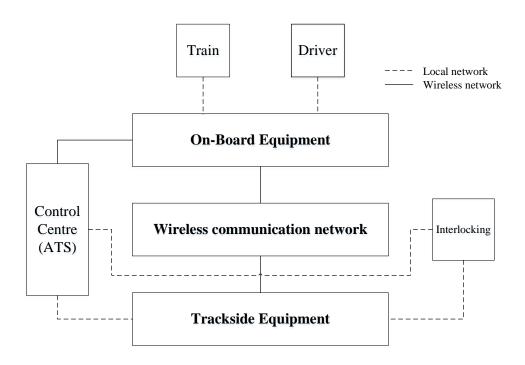

As mentioned in section 1.1, different types of TCS are selected for use in different countries based on national rulebooks and other constraints. To indicate that the proposed testing method can be adopted to test ETCS, CBTC or other TCSs, the author has generalised the system structures of the different TCSs to illustrate their similarities.

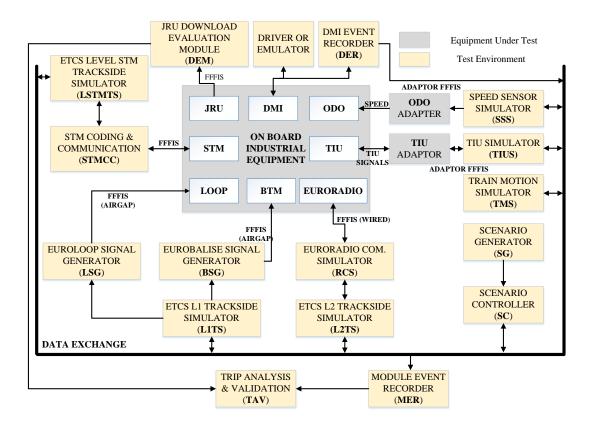

Fig 4 Generalised system structure of ETCS, CBTC or other TCSs

As indicated by Fig 4, different types of TCS share a generalised system structure which includes the on-board equipment, trackside equipment and radio communication network. On-board equipment, such as the OBU in ETCS or the VOBC in CBTC, is responsible for guaranteeing the safe movement of the train and feeds back the operation conditions of the train to the trackside equipment. Trackside equipment, such as the Radio Block Centre (RBC) in ETCS or the Zone Controller (ZC) in CBTC, is responsible for indicating where the train should go along the track and feeds back the track conditions to the control centre or Automatic Train Supervision (ATS), in collaboration with the interlocking. ATS is responsible for supervising the operation conditions of the integrated railway system, and sends macro-control commands when necessary, such as sending a rescheduling command when a delay happens. The on-board equipment is installed on the train to control the train movements. The driver can send a command to the on-board equipment via the Driver-Machine Interface (DMI) when necessary. Based on the generalised structure of different types of TCS, functions need to be realised collaboratively by two or more of the elements presented, which means that the functional behaviour of the systems can be complex, and the modelling difficulties can increase. Even so, TCSs can be modelled in the same framework, which means they can be tested by the same MBT method. The following table shows a comparison of the functions and system composition of ETCS and CBTC systems [41], where 'X' denotes the presence of the component and '-' denotes the absence of the component:

|       |       |             | CBTC      |          |   |           |             |  |

|-------|-------|-------------|-----------|----------|---|-----------|-------------|--|

| Earli | nnant |             | Operation | on Level |   | D.        | aviene on t |  |

| Equi  | pment | LO L1 L2 L3 |           |          |   | Equipment |             |  |

| OBU   | DMI   | X           | X         | X        | X | VOBC      | TOD         |  |

|           | ı             |   | 1 |   | 1 |           |              |

|-----------|---------------|---|---|---|---|-----------|--------------|

|           | BTM           | ı | X | X | X |           | TIA          |

|           | TCR           | X | X | X | - |           | -            |

|           | ODO           | X | X | X | X |           | ODO          |

|           | EVC           | X | X | X | X |           | KVC          |

|           | Euroradio     | X | X | X | X |           | OBRU         |

|           | JRU           | X | X | X | X |           | DR           |

|           | TIU           | X | X | X | X |           | TIMS         |

|           | Eurobalise    |   | X | X | X |           | Balise       |

|           | (or Euroloop) | - | Λ | Λ | Λ |           |              |

| Trackside | TC (or axle   | X | X | X |   | Trackside | Axle Counter |

| Trackside | counter)      | Λ | Λ | Λ | _ | Trackside |              |

|           | LEU           | - | X | - | - |           | -            |

|           | RBC           | - | - | X | X |           | ZC           |

| Wireless  | GSM-R         | X | X | X | X | DCS       | S (WLAN)     |

| network   | USWI-K        | Λ | Λ | Λ | Λ | DC        | o (WLAIN)    |

Table 2 Comparison of ETCS and CBTC systems

In ETCS and CBTC systems, some components with similar functions are given different names, such as the European Vital Computer (EVC) in ETCS and the Kernel Vital Computer (KVC) in CBTC, which are both vital computers providing the necessary computations for train control. Similarly, Euroradio and On-Board Radio Unit (OBRU) are both radio communication terminals for on-board equipment of ETCS and CBTC. Overall, ETCS and CBTC systems control train movements by the cooperation of on-board and trackside equipment. Bidirectional communication is established between the on-board and trackside equipment to exchange information essential for their operation. Four operational levels are included in ETCS systems to adapt to the operation of the legacy railway systems existing in different European countries.

In order to fulfil the reviewed system requirements, companies such as Siemens, Bombardier,

Thales and the China Railway Rolling Stock Corporation (CRRC), have developed their own CBTC solutions. Although the CBTC systems developed share the same architecture as illustrated in Fig 4, the components used in each of the systems are different; the author has therefore not fully listed the components of the CBTC system, instead including only the main components and subsystems. One prominent feature of CBTC systems is that Wireless Local Area Networks (WLAN) are most commonly used as the radio communication network of the Data Communication System (DCS), while ETCS systems usually utilise GSM-R. Due to the different application scenarios, the specific functional performance of the subsystems and components in ETCS and CBTC systems can be different. Nevertheless, the macro-system architecture, specifically the cooperation of trackside and on-board subsystems by wireless communication via a radio network, is highly uniform.

As revealed by Fig 4 and Table 2, ETCS and CBTC systems, which between them represent the majority of modern TCSs, share a united system structure and functional features. For black-box testing which aims to verify that the functions developed comply with the specification requirements, the similarities between the TCSs means that the I/O interface between the SUT and the testing tool can be used for testing different systems, with minor modifications. For HIL testing, similar system structures and composition mean that the simulation for an HIL environment can be used repeatedly without major modifications when testing different types of TCS. For MBT, formal modelling of TCSs with similar features means that modelling difficulties will not increase when testing different types of TCS. As a result, functional testing of modern TCSs based on a unified testing method can be

promisingly realised.

#### 2.2 Traditional MBT Methods

Based on the discussion in section 1.1, MBT can significantly reduce the cost and time associated with testing, and achieve better quality performance by having better traceability and extendibility compared with traditional manual testing methods. Despite this, it is not a flawless testing method without limitations. Firstly, MBT does not enhance the ability to detect defects in the SUT, because it still relies the tester to build the specification model, which is the mechanism used to determine whether the test should pass, and to choose the test generation strategies; this means the performance of the MBT is determined by the skill and experience of the tester [30]. Further, MBT cannot be guaranteed to find all the errors contained in the SUT, which is the limitation for all other testing methods [26]. Nevertheless, with a well-modelled test oracle and a correctly selected test generation strategy, MBT increases the possibility of finding errors at a lower test cost and in a shorter test time. This leads to the second disadvantage of MBT, which is that it is more difficult to implement than manual testing because of difficulties in formal modelling and test generation algorithms [18]. To formalise the SUT behaviour, MBT demands that testers have a deep understanding of the operation principles of the SUT so that they can build a precise and unambiguous model which can be understood and processed by various test tools. It can take the tester years of practice to be familiar with one type of formal modelling method and the corresponding test generation algorithms. Furthermore, testers should understand how to test SUTs manually in order to build specification model for MBT because MBT is an automation of manual testing methods.

In addition, MBT is strongly associated with functional testing and is rarely utilised in other types of testing, except that it is occasionally used in stress testing [30]. Some kinds of SUT, such as those which involve plenty of man—machine interactions, are not eligible for applying MBT because of their unique characteristics. For example, the DMI which is one of the components in the OBU is not suitable for automatic testing methods such as MBT because it is designed to provide driving instructions for the driver via a screen. Although MBT can check whether the I/O data of the DMI is correct, it cannot prove that the corresponding screen display is correct. As a result, these kinds of SUT should be manually tested. Even worse, analysis of failed tests in MBT can be time-consuming because the testing results obtained are in a formal format, which can be understood by a computer but is not convenient for inexperienced people to understand. By comparison, testing results in manual black-box testing are easier to analyse because they are straightforward so that the tester can locate the errors by comparing the results with the specification requirements.

Lastly, traditional MBT methods mostly require that the specification model is deterministic regardless of whether the SUT itself is deterministic. However, complex systems such as TCSs can be nondeterministic in some or all layers, including the unit layer, component layer, subsystem layer and system layer. Elimination of nondeterminism is not only a time-consuming and difficult process but can also be a risky operation leading to state explosion. Online MBT algorithms are designed to deal with nondeterministic SUTs, which further increases the difficulties in implementing MBT. As mentioned in section 1.1, online

testing is more appropriate for the implementation of TCS testing due to its ability to deal with nondeterminisms contained in the system with less strict time constraints. Since online testing needs to simultaneously generate and execute test cases, the test tools must be highly synchronised with the SUT to guarantee that the observed I/O sequences are valid for the defined outcome criteria. Therefore, the interfaces used for mapping the abstract I/O for test tools and real I/O for SUTs are one of the key elements in testing implementation, and any wrong I/O mapping or poor efficiency of translation can lead to a failure result. Another adverse factor is that a communication delay between the test tool and the SUT becomes non-negligible when the SUT is a timed system with a set of time constraints [42], especially when dealing with complex SUTs such as TCSs which include communications between hardware and software components. This increases the modelling difficulties in online MBT. Because of the difficulties and limitations mentioned, online MBT is only supported by a few MBT tools, such as QTronic and UPPAAL-TRON.

Despite the limitations discussed, online MBT is still a feasible solution for automatic testing. Unlike other automatic testing methods such as script testing or keyword-driven testing, which incompletely automate the functional testing process, MBT can completely automate the test process: the test is automatically generated and executed, and the testing results are automatically qualitatively analysed. Therefore, MBT is adopted more and more to save testing time and resources, improve testing quality and guaranteeing its correctness.

For MBT, modelling methods, test selection criteria and test tools are the three key elements, and the tester needs to make appropriate choices for each of these three according to the

characteristics of the SUT and its testing environment. Hundreds of different modelling methods have been used to describe SUT behaviour for MBT. As one modelling method commonly corresponds to one or more test generation tools, the author will first classify and introduce different MBT methods by introducing various modelling methods. Next, the author lists a series of test selection criteria for different types of model with different testing purposes. Finally, the author introduces several test tools which support the modelling methods and test selection criteria introduced.

## 2.2.1 Introduction of Modelling Methods for MBT

As a wide-ranging concept which can appear in many fields, modelling has a set of different meanings for different purposes. Since MBT mainly depends on formal modelling methods which can be used as the test oracle for test case generation and test result verdicts, the author focuses on formal modelling methods in this thesis [43]. The basis for classification can vary from person to person, and the author has adopted one proposed by Utting and Legeard [30]. The original classification targets the industrial field, introducing almost every modelling method involved with MBT in detail. In this thesis, the author has refined the original classification scheme by omitting modelling methods which are rarely utilised in MBT, and explains in detail those which are commonly adopted for research purposes. As a result, the modelling methods for MBT are divided into three categories; state-based modelling methods, transition-based modelling methods and other modelling methods.

#### 2.2.1.1 State-Based Modelling Methods

State-based, also known as pre/post, modelling methods depict a system based on a set of states with variables in and constraints on those states. In one state, actions or operations may happen when the corresponding conditions are satisfied, and the variables are then updated according to the defined relations. State-based modelling methods concentrate on describing the internal conditions in states, and therefore weaken the external transitions between two states. As a result, they are more suitable for modelling data flow-oriented SUTs of which functional testing emphasises correct data flow and is less concerned about control flow. Typical examples of state-based modelling methods include but are not limited to B/Event-B [44, 45], Z [46], Unified Modelling Language (UML), Object Constraint Language (OCL), Java Modelling Language (JML) [47], Spec# [48] and the Vienna Development Method (VDM) [30]. As one of the most typical state-based modelling methods, Event-B will now be introduced by the author with a modelling example.

As an evolved version of the B method, Event-B makes it easier to perform refinement and verification processes with the help of developed software platforms [49]. Summarised by Cansell and Mery [45], the key elements of an Event-B model are illustrated by Fig 5:

machine sets constants properties axioms end

Fig 5 Elements of an Event-B model

As illustrated by Fig 5, Event-B is a contextual modelling notation in which a model consists of the following clauses: the *machine*, the *sets*, the *constants*, the *properties* and the *axioms*. The clause *machine* gives the model a name; the clause *sets* contains definitions of sets in the problem; the clause *constants* summarises the variables involved in the clause *properties* which are the detailed definition of the *sets*; the clause *axioms* contains the invariant rules that should be held by the developed model and which are going to be verified by the proof engine. Once the specification model of the SUT is obtained based on Event-B, the test cases can be derived from the specification model with the assistance of test tools along with selected test selection criteria.

# 2.2.1.2 Transition-Based Modelling Methods

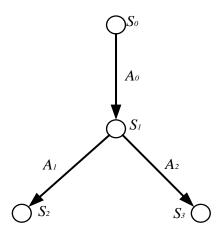

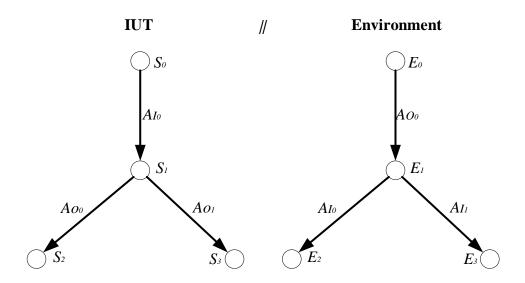

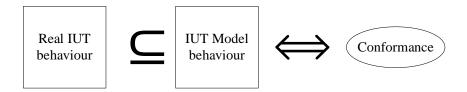

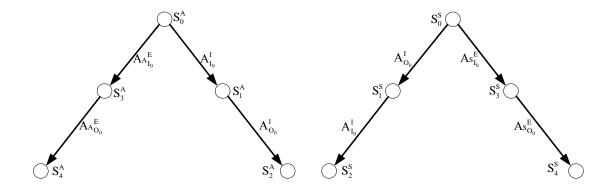

Compared with state-based modelling methods, transition-based modelling methods emphasise transitions from state to state and concentrate less on the profiles of internal states. One of the typical representatives is the Finite State Machine (FSM), which is a graphical notation describing a system with the pattern node—transition—node. The node represents the essential states of a system, and the transition represents the actions or operations which happen when the transitions happen, as shown by Fig 6:

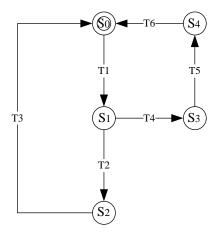

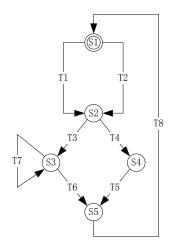

Fig 6 Schematic of finite state machines

In practice, an FSM can be extended by adding snapshots of each state, configuring hierarchical structures for different layers, and establishing parallel connections between several state machines. Extended versions adapt to different characteristics of systems so that they can model the transition flow of the systems without losing other essential system information. Typical examples of transition-based modelling methods include FSM [50] and its varieties such as Labelled Transition Systems (LTS), I/O automata, Timed Automata (TA) and hybrid automata, and statecharts such as UML State Machines, STATEMATE statecharts and Simulink Stateflow charts [30]. Although the methods mentioned have specialisation use in particular scenarios, they share the common points that they are all transition-based; the main differences come from the different configurations of their platform. Therefore, the author introduces two of the methods to indicate the similarities and differences between different transition-based modelling methods.

# • Timed automata [51]

As one of the varieties of FSM, TA evolves with a finite set of timed clocks which linearly

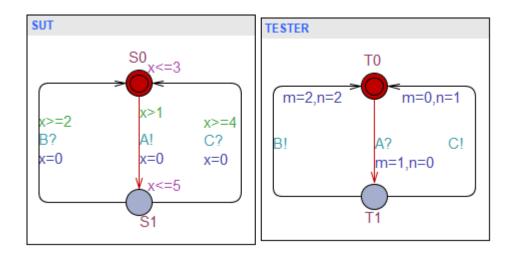

increase in states during the operation procedure. TA is suitable for modelling timed systems with linear time constraints. With the assistance of model checkers, TA models can be verified against formalised properties such as liveness which means some states are reachable and safety. The author will now introduce the UPPAAL platform, which models a system based on the TA format [52, 53].

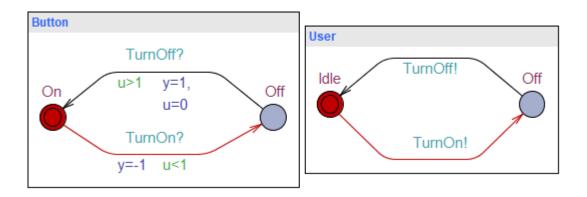

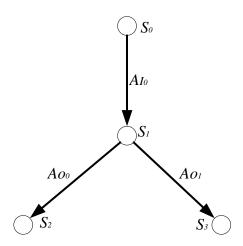

Fig 7 Schematic of TA model on the UPPAAL platform

As indicated by Fig 7 which is a formal model of a button, the TA model on the UPPAAL platform absorbs the features of labelled transitions systems and I/O automata, and the input and output are respectively indicated by specific labels. This configuration is specially designed so that it is more convenient for the test generation tool to recognise inputs and outputs. Another feature is that the TA modelling method models the SUT and its operational environment or user in a parallel structure of two or several automata, where two transitions are synchronised by an input/output pair to happen at the same time. With the corresponding test generation tools, the test cases or sequences can be derived from the TA models built.

#### Statecharts

Statecharts are quite similar to FSM-based modelling methods such as the TA modelling

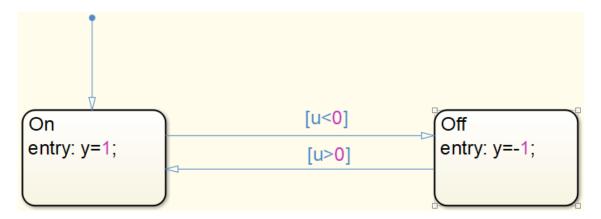

method. However, there are still some differences between them so that the tester should select the appropriate modelling method according to their specific testing purpose. As revealed by Fig 8 and Fig 9, which show a button model built on the MATLAB Simulink platform, statecharts on the Simulink platform can describe systems in a hierarchical structure, while the TA on the UPPAAL platform can only support a parallel structure. This could be an advantage when modelling complex systems consisting of numerous layers. Furthermore, with a more advanced graphical user interface, modelling difficulties can be reduced so that the modelling efficiency can be improved.

Fig 8: Schematic of statechart model on the Simulink platform

Fig 9 Complete model for the statechart model

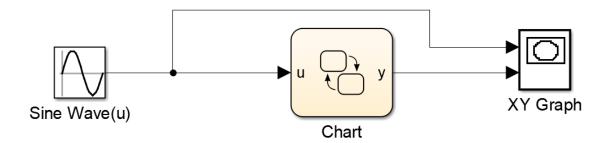

As shown in Fig 9, the external stimulus, which can be a continuous or discrete signal, can be

freely defined by the user; this is difficult to achieve with FSM-based tools such as UPPAAL. Based on more simulation models, Simulink statecharts can include more detailed information in the model. However, most of the matched test tools for Simulink statecharts stay at the stage of script testing or keyword-driven testing, both of which entirely or partially rely on the tester to design the test cases; neither of them provides genuine automatic test case generation. According to Fig 2, the efficiency advantage of MBT appears gradually along with an increasing number of test cases, in other words, with the complexity of the SUT. When testing systems like TCSs, automatic design of functional testing becomes more important. Although some of test tools are claimed to be able to realise automatic test case generation, they are still in immature forms. For example, Li and Kumar [54] developed an algorithm for automatic test case generation based on the Simulink statechart model that translated the statechart model into IO-EFA, a variety of FSM, then applied model-checking to generate test cases. The company T-Vec [55] claims that their product can automatically generate test cases, but the test tool is commercial making its performance difficult to verify. According to Blackburn et al. [56-58], their product aims to automatically generate test vectors, a set of various inputs desired for certain testing purposes, which belong to the fields of script testing and keyword-driven (table-driven) testing. In general, most of the test tools based on Simulink cannot realise automatic test case generation.

#### 2.2.1.3 Other Modelling Methods

The author has gathered the remaining kinds of modelling method into this category because they are usually utilised in combination with one or several other modelling methods. History-based modelling methods such as Message-Sequence Charts (MSC) [59] describe system behaviour by recording the message exchange process between two or more components. As a result, though it can be eligible for modelling communication protocols, the preferred usage is to present the test cases or test sequences generated by specifying the data exchanged between the tester and the SUT. As typical representatives of operational modelling methods which focus on describing interactions between concurrent systems [60], Communicating Sequential Processes (CSP) and Petri Nets (PN) [61] are often used in combination with other modelling methods, such as FSM-based methods, to formally obtain hierarchical system models [62, 63]. Other modelling methods such as functional notations, statistical notations such as Markov chains [64], and data-flow notations are occasionally adopted by some modelling tools for system modelling, verification and testing.

# 2.2.1.4 Summary

Countless modelling methods have been applied to the MBT field, and it would not be appropriate for the author to include all of them in this thesis. Instead, those most representative of the main categories have been introduced by the author. To automate the testing process, a specification model needs to be utilised to formally describe the SUT behaviour so that the computer can generate test cases by analysing the specification model. Therefore, choosing the appropriate modelling method is an essential foundation of successful implementation of MBT. One of the guiding principles of choosing a modelling method for MBT is to choose according to the characteristics [30] and emphasis of the SUT. For testing data-oriented SUTs where the tester focuses on the key parameters, it is recommended to

choose state-based modelling methods because methods such as the B method, as these support a wide range of data types allowing the tester to precisely describe the SUT behaviour. Transition-based modelling methods, such as LTS, can conveniently describe the complex transition relations between different nodes of the state machine based on the node–transition–node format. However, state–based modelling methods have to specify the precondition and postcondition for every state so that the model becomes unnecessarily large when the transition relationship is complex. Therefore, for testing control-oriented SUTs where the tester is concerned about the transition flow of the SUT, it is recommended to utilise transition-based modelling methods to guarantee modelling efficiency.

The classification between data-oriented and control-oriented systems becomes ambiguous when the SUT is an integrated system with a relatively high degree of complexity, such as a TCS, for which extensive data verification and control-flow verification are both required in the testing. Therefore, the tester should select a suitable modelling method that can fulfil the requirements of testing implementation for such systems. State-based modelling methods can still deal with control-oriented SUTs, and transition-based modelling methods can still deal with data-oriented SUTs. As a result, the type of SUT is not the only basis for determining the modelling method. In conclusion, a modelling method is appropriate if it can precisely describe the SUT behaviour. In Table 3, some modelling methods which have been frequently adopted for MBT are listed with their classification and a brief description.

| Notation                  | Classification       | Remarks                                                                                |  |

|---------------------------|----------------------|----------------------------------------------------------------------------------------|--|

| В                         | State-based          | Abstract machine notation                                                              |  |

| Z                         | State-based          | Based on first-order predicate logic and set theory                                    |  |

| JML                       | State-based          | Behavioural specification language                                                     |  |

| Spec# [65]                | State-based          | Object-oriented language, extension of C#                                              |  |

| SeC (C++) [66, 67]        | State-based          | Applying contract approach, based on C, C# and Java                                    |  |

| OCL [30, 68]              | State-based          | Object-oriented language supporting UML                                                |  |

| VDM [69, 70]              | State-based          | Object-oriented specification language                                                 |  |

| Statecharts [71]          | Transition-based     | Formal realisation of FSM                                                              |  |

| UML SM [72, 73]           | Transition-based     | Behaviour description language based on UML                                            |  |

| Stateflow charts [74, 75] | Transition-based     | Supported by UML and MATLAB Simulink                                                   |  |

| LTS [76, 77]              | Transition-based     | Behaviour description language, basis of I/O automata and other FSM-based varieties    |  |

| TA [51, 78]               | Transition-based     | Extended LTS with time constraints, supported by UPPAAL                                |  |

| MSC                       | History-based        | Often combined with SDL                                                                |  |

| HOL [79]                  | Functional notation  | Often combined with other software tools                                               |  |

| CSP                       | Operational notation | Often combined with PN                                                                 |  |

| CCS                       | Operational notation | Often combined with PN                                                                 |  |

| Petri net                 | Operational notation | Often combined with CSP, CCS                                                           |  |

| Markov chains             | Statistical notation | Good at describing a choice of input, weak at predicting expected output. So, needs to |  |

|                 |           | be combined with other modelling methods   |  |

|-----------------|-----------|--------------------------------------------|--|

| Lustre [80, 81] | Data-flow | Describes concurrent systems, supported by |  |

|                 | notation  | MATLAB Simulink and SCADE                  |  |

| Block diagram   | Data-flow | For modelling continuous systems           |  |

|                 | notation  |                                            |  |

Table 3 Summary of formal modelling methods

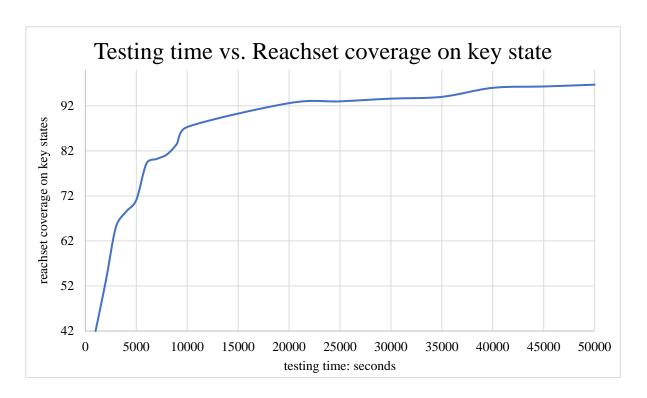

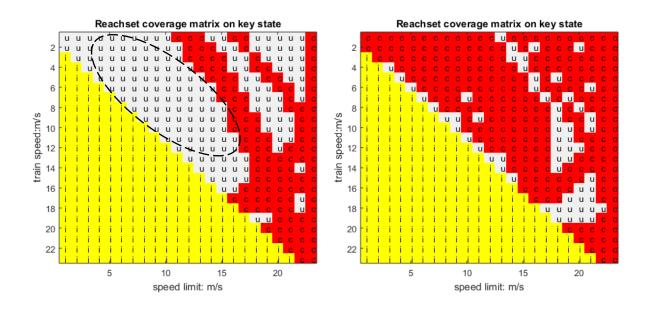

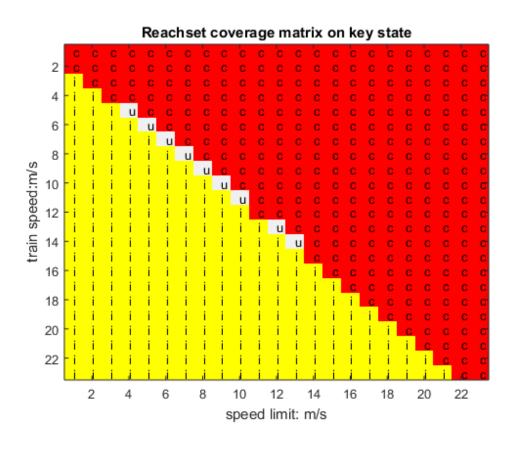

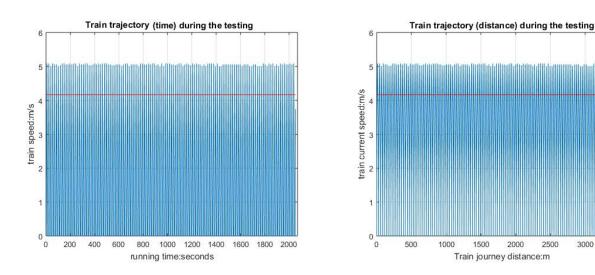

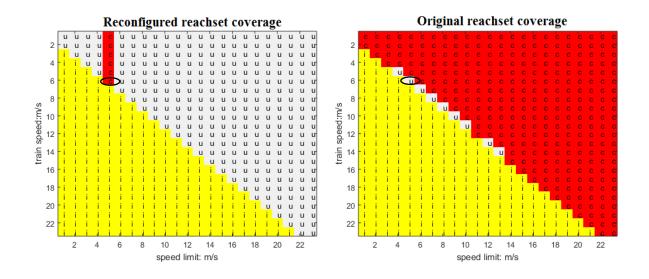

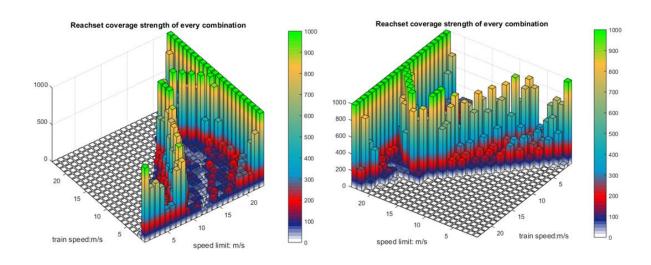

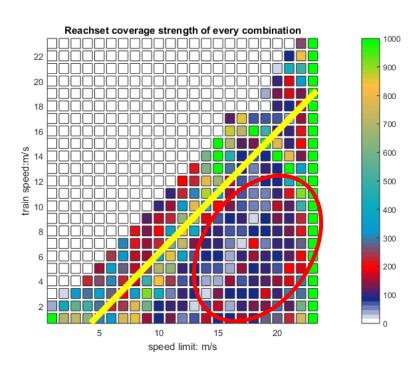

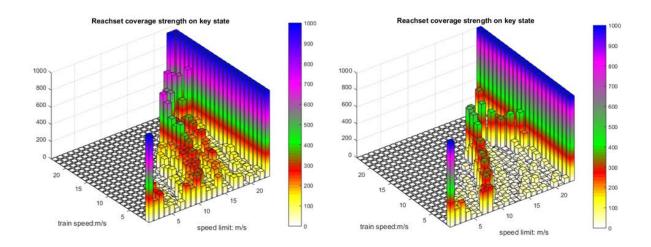

#### 2.2.2 Introduction of Test Selection Criteria