# BEHAVIOURAL SYNTHESIS OF ANALOGUE INTEGRATED CIRCUITS

by

SIMON JAMES PARISH

DOCTOR OF PHILOSOPHY

School of Electronic, Electrical and Computer Engineering The University of Birmingham B15 2TT England

January 14, 2010.

## UNIVERSITY<sup>OF</sup> BIRMINGHAM

### **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

# Contents

| 1        | Introduction & Motivation |                                                 |    |  |  |  |

|----------|---------------------------|-------------------------------------------------|----|--|--|--|

|          | 1.1                       | The Analogue Design Problem                     | 2  |  |  |  |

|          |                           | 1.1.1 The 'Dark Arts'                           | 3  |  |  |  |

|          |                           | 1.1.2 Design Automation                         | 3  |  |  |  |

|          |                           | 1.1.3 The Digital/Analogue Split                | 4  |  |  |  |

|          |                           | 1.1.4 Circuit Topology, Sizing & Layout         | 6  |  |  |  |

|          | 1.2                       | The Analogue Synthesis Problem                  | 7  |  |  |  |

|          |                           | 1.2.1 Previous Research                         | 8  |  |  |  |

|          | 1.3                       | Research Overview                               | 9  |  |  |  |

|          |                           | 1.3.1 Research Objectives                       | 10 |  |  |  |

|          | 1.4                       | Thesis Contributions                            | 11 |  |  |  |

|          | 1.5                       | Thesis Structure                                | 12 |  |  |  |

| <b>2</b> | Elec                      | ctronic Design Automation: A Brief Introduction | 14 |  |  |  |

|          | 2.1                       | Introduction to EDA                             | 15 |  |  |  |

|   |                            | 2.1.1                               | Circuit Abstraction                                                                    | 16                               |

|---|----------------------------|-------------------------------------|----------------------------------------------------------------------------------------|----------------------------------|

|   |                            | 2.1.2                               | EDA Concepts                                                                           | 17                               |

|   |                            | 2.1.3                               | A Typical Design Flow For Digital ICs                                                  | 20                               |

|   |                            | 2.1.4                               | A Typical Design Flow For Analogue & Mixed Signal ICs                                  | 23                               |

|   | 2.2                        | Evolu                               | cion of EDA                                                                            | 26                               |

|   |                            | 2.2.1                               | Early Computers And The First Integrated Circuits                                      | 26                               |

|   |                            | 2.2.2                               | Early ICs & Design Methods                                                             | 28                               |

|   |                            | 2.2.3                               | The Mead-Conway Revolution                                                             | 29                               |

|   |                            | 2.2.4                               | HDLs and Modern EDA                                                                    | 31                               |

|   | 2.3                        | Challe                              | enges Faced By Analogue EDA                                                            | 32                               |

|   |                            |                                     |                                                                                        |                                  |

| 3 | Арр                        | oroach                              | es to Analogue Synthesis: Attempts At Solving The Problem                              | 35                               |

| 3 | <b>Ap</b> <sub>1</sub> 3.1 |                                     | es to Analogue Synthesis: Attempts At Solving The Problem  Is Synthesis Not Synthesis? | <b>35</b>                        |

| 3 |                            |                                     |                                                                                        |                                  |

| 3 |                            | When 3.1.1                          | Is Synthesis Not Synthesis?                                                            | 36<br>37                         |

| 3 |                            | When 3.1.1                          | Is Synthesis Not Synthesis?                                                            | 36<br>37                         |

| 3 |                            | When 3.1.1 3.1.2 3.1.3              | Is Synthesis Not Synthesis?                                                            | 36<br>37<br>38                   |

| 3 | 3.1                        | When 3.1.1 3.1.2 3.1.3              | Is Synthesis Not Synthesis?                                                            | 36<br>37<br>38<br>38             |

| 3 | 3.1                        | When 3.1.1 3.1.2 3.1.3 Relate       | Is Synthesis Not Synthesis?                                                            | 36<br>37<br>38<br>38<br>40       |

| 3 | 3.1                        | When 3.1.1 3.1.2 3.1.3 Relate 3.2.1 | Is Synthesis Not Synthesis?                                                            | 36<br>37<br>38<br>38<br>40<br>40 |

|   |     | 3.2.5 Circuit Evaluators                   | 62 |

|---|-----|--------------------------------------------|----|

| 4 | Gen | netic Algorithms                           | 65 |

|   | 4.1 | The Classic GA                             | 66 |

|   | 4.2 | Encoding Schemes                           | 68 |

|   | 4.3 | Schemata                                   | 69 |

|   | 4.4 | Genetic Operators                          | 70 |

|   |     | 4.4.1 Selection                            | 70 |

|   |     | 4.4.2 Crossover                            | 71 |

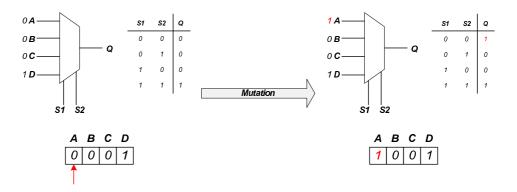

|   |     | 4.4.3 Mutation                             | 72 |

|   | 4.5 | Schema Theory                              | 73 |

|   | 4.6 | Alternative GA Implementations             | 75 |

|   |     | 4.6.1 Alphabet Cardinalities               | 76 |

|   |     | 4.6.2 Variable Length Encoding Schemes     | 76 |

|   |     | 4.6.3 Crossover For Other Encoding Schemes | 77 |

|   |     | 4.6.4 Selection Operators                  | 77 |

|   | 4.7 | Fitness Functions                          | 79 |

|   | 4.8 | Genetic Programming                        | 81 |

|   |     | 4.8.1 Parse Trees                          | 82 |

|   |     | 4.8.2 GP Crossover                         | 82 |

|   |     | 4.8.3 GP Mutation                          | 85 |

|   |                                               | 4.8.4                                        | GP For Circuit Synthesis                | 85                                                   |

|---|-----------------------------------------------|----------------------------------------------|-----------------------------------------|------------------------------------------------------|

| 5 | SPI                                           | CE Si                                        | mulation & Other GA Issues              | 87                                                   |

|   | 5.1                                           | Circui                                       | t Encoding Considerations               | 88                                                   |

|   | 5.2                                           | The P                                        | roblem With SPICE                       | 89                                                   |

|   |                                               | 5.2.1                                        | SPICE Basics & Analysis Types           | 90                                                   |

|   |                                               | 5.2.2                                        | Aborted & Non-Convergent Simulations    | 92                                                   |

|   |                                               | 5.2.3                                        | Sources Of Error                        | 97                                                   |

|   |                                               | 5.2.4                                        | Other Simulators                        | 99                                                   |

|   |                                               | 5.2.5                                        | Implications For Genetic Algorithms     | 99                                                   |

|   |                                               |                                              |                                         |                                                      |

| 6 | A                                             | Genetic                                      | Algorithm System for Analogue Synthesis | 103                                                  |

| 6 | <b>A G</b> 6.1                                |                                              | Algorithm System for Analogue Synthesis |                                                      |

| 6 |                                               | Object                                       |                                         | 104                                                  |

| 6 | 6.1                                           | Object                                       | tives                                   | 104<br>104                                           |

| 6 | 6.1                                           | Object Overv                                 | iew Of Implementation                   | 104<br>104<br>106                                    |

| 6 | 6.1                                           | Object Overv                                 | tives                                   | 104<br>104<br>106<br>111                             |

| 6 | 6.1                                           | Object Overve 6.2.1 GA Sy                    | tives                                   | 104<br>104<br>106<br>1111                            |

| 6 | 6.1                                           | Object Overv. 6.2.1 GA Sy 6.3.1 6.3.2        | tives                                   | 104<br>104<br>106<br>111<br>111<br>113               |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Object Overv. 6.2.1 GA Sy 6.3.1 6.3.2        | tives                                   | 104<br>104<br>106<br>111<br>111<br>113               |

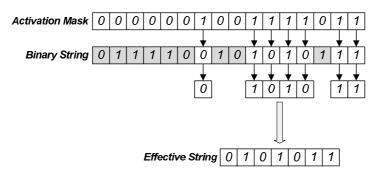

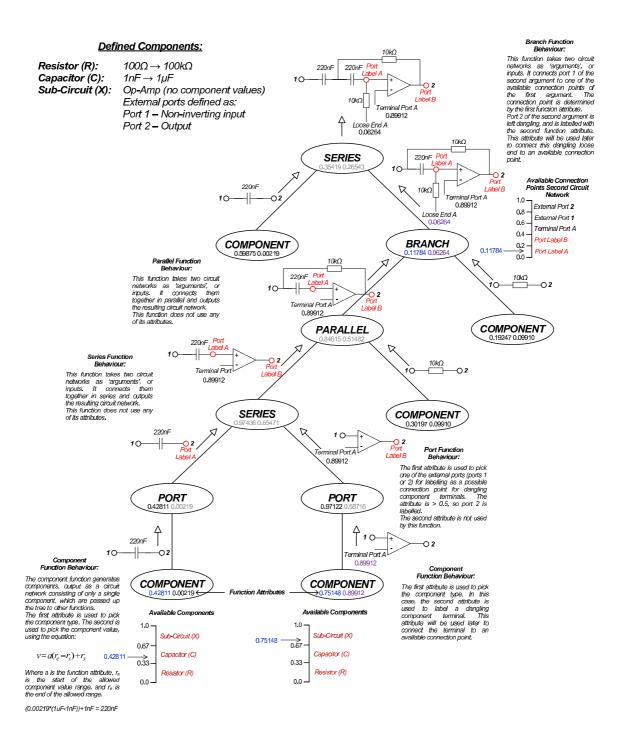

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | Object Overvi 6.2.1 GA Sy 6.3.1 6.3.2 Encode | tives                                   | 104<br>104<br>106<br>111<br>111<br>113<br>114<br>116 |

|   |     | 0.4.4   | Circuit Finalisation                                 | . 128 |

|---|-----|---------|------------------------------------------------------|-------|

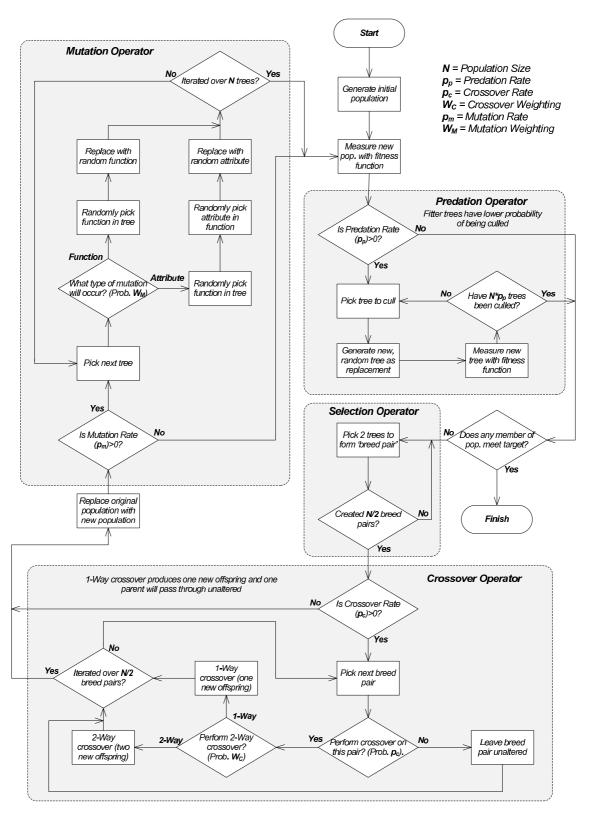

|   | 6.5 | Genet   | ic Operators                                         | . 131 |

|   |     | 6.5.1   | Selection                                            | . 132 |

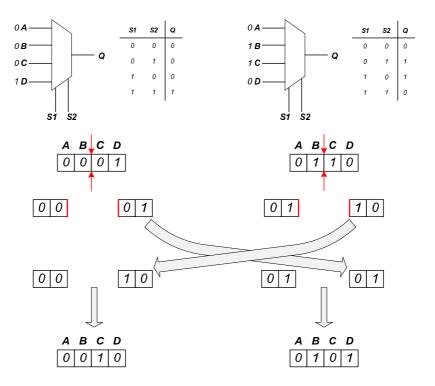

|   |     | 6.5.2   | Crossover                                            | . 133 |

|   |     | 6.5.3   | Mutation                                             | . 135 |

|   |     | 6.5.4   | Predation                                            | . 136 |

|   | 6.6 | Candi   | date Circuit Characterisation                        | . 136 |

|   | 6.7 | Fitnes  | s Functions                                          | . 137 |

|   |     | 6.7.1   | Shape-fitting                                        | . 138 |

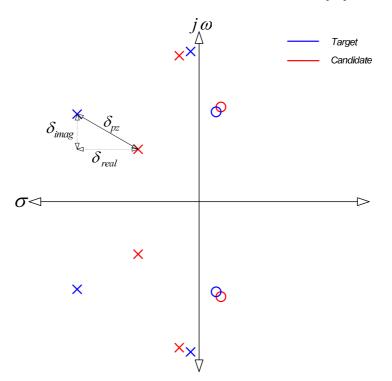

|   |     | 6.7.2   | Pole-Zero                                            | . 138 |

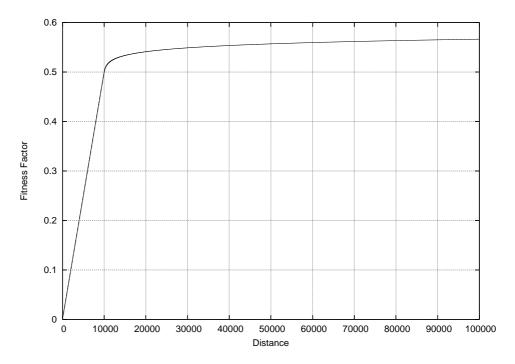

|   |     | 6.7.3   | Component Count                                      | . 142 |

|   | 6.8 | GA Sy   | ystem Outputs                                        | . 143 |

| 7 | Cas | e Stud  | lies                                                 | 144   |

|   | 7.1 | Initial | Experiments                                          | 1/15  |

|   | 7.1 | IIIIIII |                                                      |       |

|   |     | 7.1.1   | Experiment 1: 4 <sup>th</sup> Order Chebyshev Filter | . 146 |

|   |     | 7.1.2   | Experiment 2: 5th Order Chebyshev Filter             | . 150 |

|   |     | 7.1.3   | Experiment 3: 6th Order Chebyshev Filter             | . 153 |

|   |     | 7.1.4   | Discussion of Initial Experiments                    | . 155 |

|   | 7.2 | GA Se   | ensitivity Experiments                               | . 158 |

|   |     | 7.2.1   | Experiment 4: Varying The Population Size            | . 159 |

|     | 7.2.2  | Experiment 5: Varying The Crossover Rate                            |

|-----|--------|---------------------------------------------------------------------|

|     | 7.2.3  | Experiment 6: Varying The Mutation Rate                             |

|     | 7.2.4  | Experiment 7: Varying The Predation Type                            |

|     | 7.2.5  | Discussion of GA Sensitivity Experiments                            |

| 7.3 | Fitnes | s Function Comparison Experiments                                   |

|     | 7.3.1  | Experiment 8: Shape Fitting Fitness Function                        |

|     | 7.3.2  | Discussion of Shape Fitting Experiment                              |

| 7.4 | Active | Filter Synthesis Experiments                                        |

|     | 7.4.1  | Experiment 9: 2 <sup>nd</sup> Order Sallen-Key Filter - Transistors |

|     | 7.4.2  | Experiment 10: 2 <sup>nd</sup> Order Sallen-Key Filter - OpAmps     |

|     | 7.4.3  | Discussion of Active Filter Synthesis Experiments                   |

| 7.5 | Schem  | ata Re-examined                                                     |

|     | 7.5.1  | Definitions For Analogue Circuit Schemata                           |

| 7.6 | Topolo | pgy Mutability Experiments                                          |

|     | 7.6.1  | Experiment 11: Component Value Modification                         |

|     | 7.6.2  | Experiment 12: Component Type Modification                          |

|     | 7.6.3  | Experiment 13: Structural Modification                              |

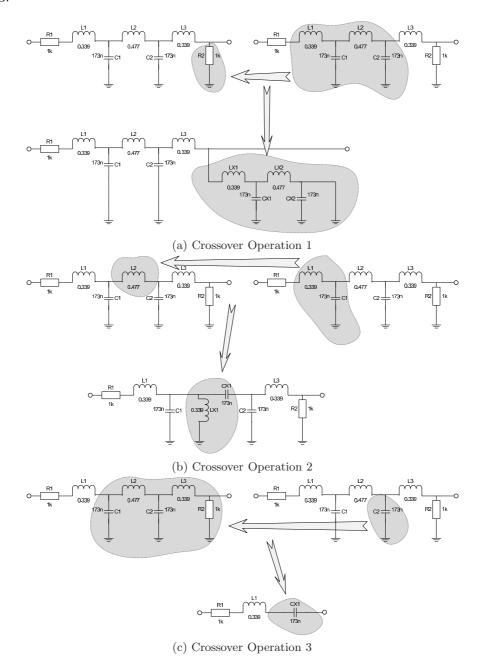

|     | 7.6.4  | Experiment 14: Modification By Crossover                            |

|     | 7.6.5  | Discussion Of Topology Mutability Experiments                       |

|     | 7.6.6  | Deduced Nature Of Schemata Of Analogue Circuits 199                 |

|     | 767    | Component Redundancy & Replication 199                              |

| 3                | Con  | iclusion | ns                                         | 203 |

|------------------|------|----------|--------------------------------------------|-----|

|                  | 8.1  | Applic   | ability of GAs to Analogue Synthesis       | 204 |

|                  |      | 8.1.1    | Guiding the Search                         | 205 |

|                  | 8.2  | Drawn    | Conclusions                                | 207 |

|                  |      | 8.2.1    | Resource Requirements                      | 207 |

|                  |      | 8.2.2    | Fitness Functions                          | 207 |

|                  |      | 8.2.3    | Impact of SPICE Non-Convergence            | 208 |

|                  |      | 8.2.4    | Topology Generation                        | 210 |

|                  |      | 8.2.5    | Genetic Algorithms As A Useful Design Tool | 211 |

|                  | 8.3  | Practio  | cal Significance Of Schema Theory          | 212 |

|                  |      | 8.3.1    | Constructive Effects Of Genetic Operators  | 213 |

|                  |      | 8.3.2    | Encoding Schemes                           | 214 |

|                  |      | 8.3.3    | Low Alphabet Cardinality                   | 215 |

|                  | 8.4  | Future   | View                                       | 216 |

|                  |      | 8.4.1    | Dynamic GA Parameter Variation             | 216 |

|                  |      | 8.4.2    | Predation Operator                         | 216 |

|                  |      | 8.4.3    | Topology Generation                        | 217 |

|                  |      | 8.4.4    | Fitness Functions                          | 218 |

| $\mathbf{A}_{]}$ | ppen | dices    |                                            | 221 |

| 4                | Exp  | erimer   | nt Run-Time                                | 221 |

| A.1  | Comp   | uting Hardware Used                     | 222 |

|------|--------|-----------------------------------------|-----|

| A.2  | Execu  | tion Times                              | 222 |

|      | A.2.1  | Initial Experiments                     | 222 |

|      | A.2.2  | GA Sensitivity Experiments              | 223 |

|      | A.2.3  | Fitness Function Comparison Experiments | 225 |

|      | A.2.4  | Active Filter Experiments               | 226 |

| Refe | erence | S                                       | 232 |

# List of Figures

| 1.1 | Relationship Between Synthesis & Simulation | 5  |

|-----|---------------------------------------------|----|

| 1.2 | Synthesis & Component Sizing                | 6  |

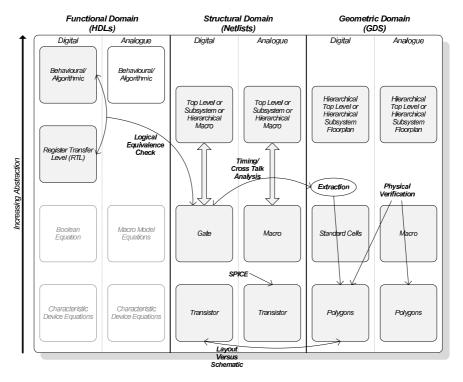

| 2.1 | Levels of Circuit Abstraction               | 17 |

| 2.2 | EDA Translation                             | 18 |

| 2.3 | EDA Verification                            | 19 |

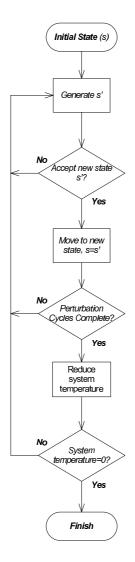

| 3.1 | Simulated Annealing Algorithm               | 43 |

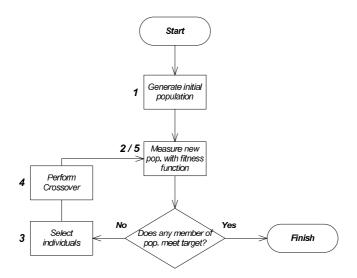

| 3.2 | Overview of Genetic Algorithm               | 47 |

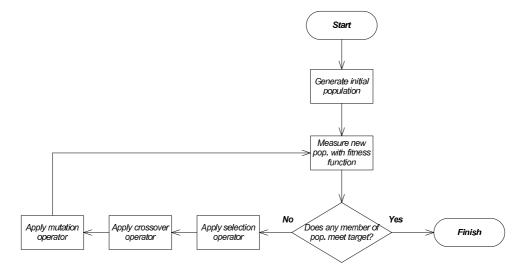

| 4.1 | Classic Genetic Algorithm                   | 67 |

| 4.2 | Example of Real Valued String Encoding      | 69 |

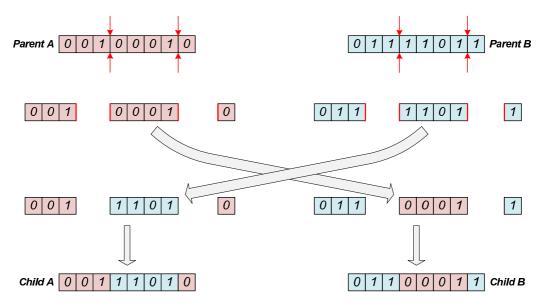

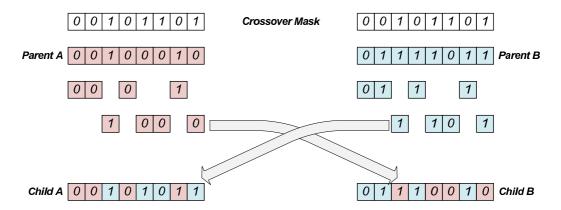

| 4.3 | Example of Binary String Crossover          | 72 |

| 4.4 | Example of Binary String Mutation           | 73 |

| 4.5 | Variable Length Strings                     | 76 |

| 4.6 | Two Point Crossover                         | 77 |

| 4.7 | Uniform Crossover                           | 78 |

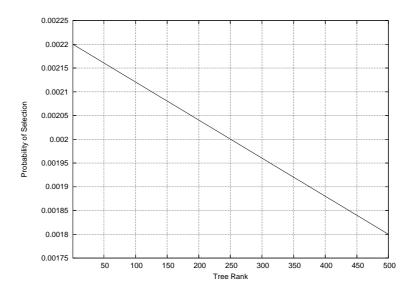

| 4.8  | Linear Rank Selection $\eta_{max} = 1.1 \ \eta_{min} = 0.9 \ \dots \ $ | 7 <u>9</u> |

|------|------------------------------------------------------------------------|------------|

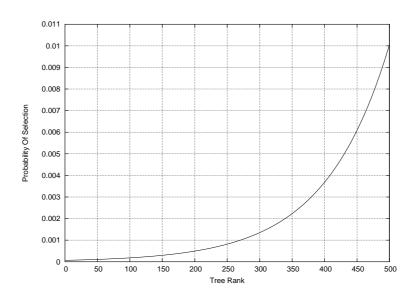

| 4.9  | Exponential Rank Selection $c=0.99$                                    | 7 <u>9</u> |

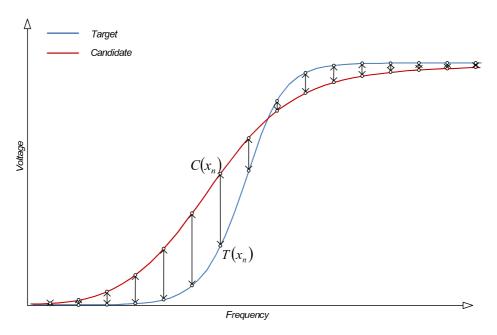

| 4.10 | Computation Of Shape-Fitting Fitness Function                          | 31         |

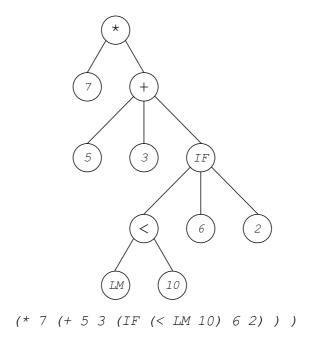

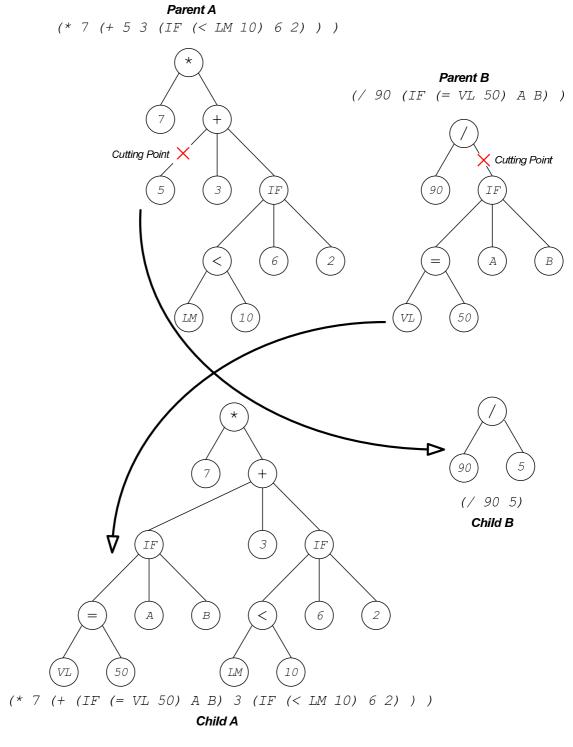

| 4.11 | LISP Parse Trees                                                       | 33         |

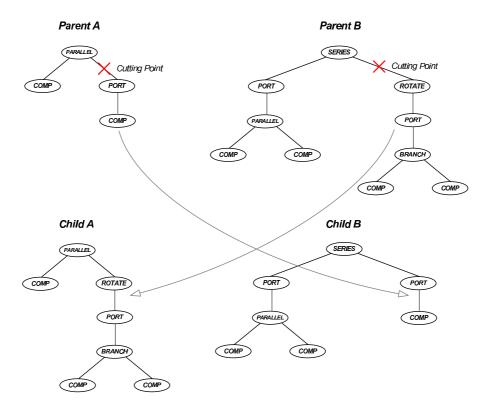

| 4.12 | GP Crossover                                                           | 34         |

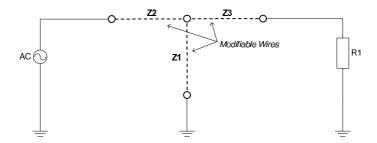

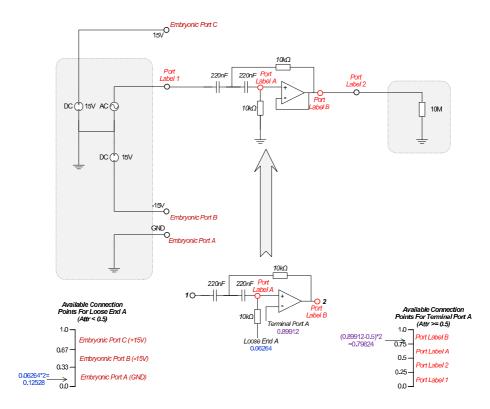

| 4.13 | GP Circuit Embryo                                                      | 36         |

| 5.1  | System Equation of SPICE                                               | <b>)</b> 1 |

| 6.1  | Implemented Genetic Algorithm                                          | )5         |

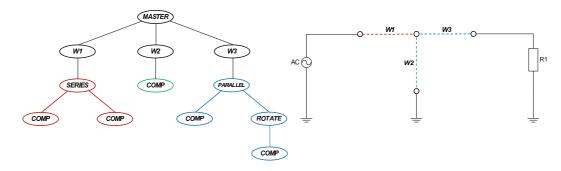

| 6.2  | Circuit Encoding Tree                                                  | )6         |

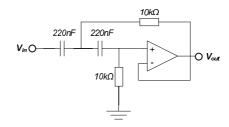

| 6.3  | High-Pass Sallen-Key Filter                                            | )8         |

| 6.4  | Example Circuit Embryo                                                 | )8         |

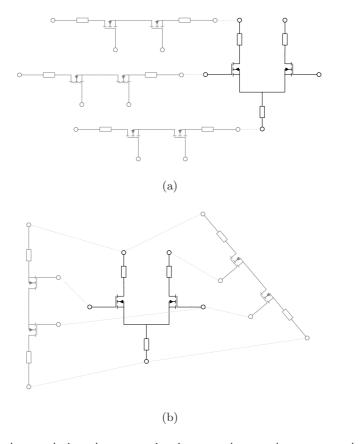

| 6.5  | Example Of Tree Encoding                                               | )6         |

| 6.6  | Circuit Finalisation                                                   | 10         |

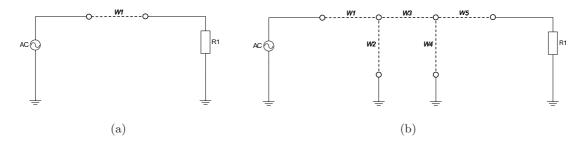

| 6.7  | Examples of Circuit Embryos                                            | 13         |

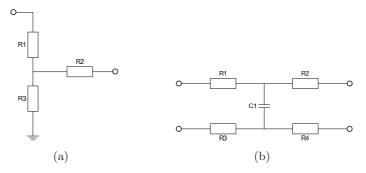

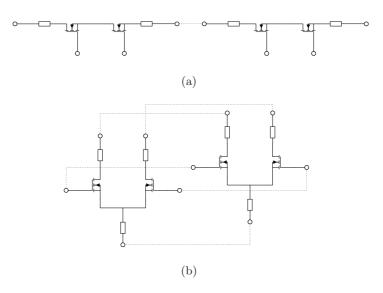

| 6.8  | Examples of Circuit Branches                                           | L7         |

| 6.9  | Series & Parallel Connection of Circuit Networks                       | 18         |

| 6.10 | Series & Parallel Connection of Multi-Terminal Circuit Networks        | 18         |

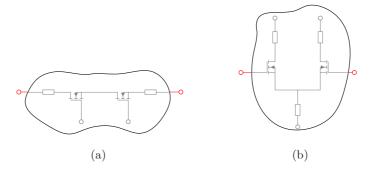

| 6.11 | Primary Ports of Multi-Terminal Circuit Networks                       | 19         |

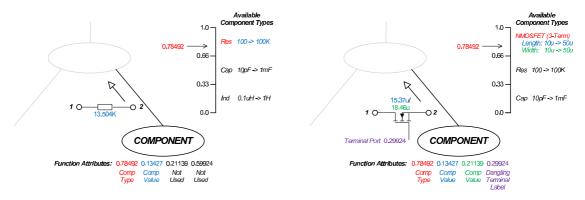

| 6.12 | Component Construction Function                                        | 21         |

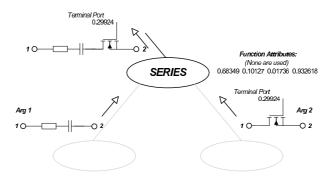

| 6 13 | Series Construction Function                                           | 22         |

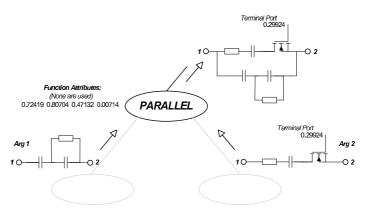

| 6.14 | Parallel Construction Function                                                         | 123 |

|------|----------------------------------------------------------------------------------------|-----|

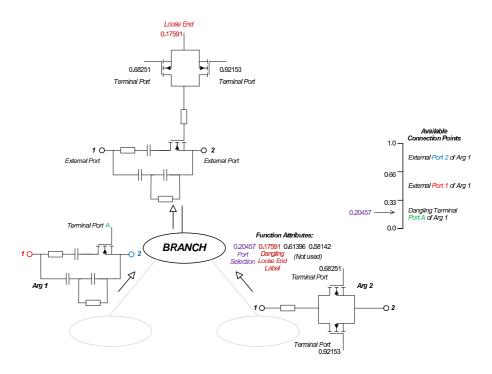

| 6.15 | Branch Construction Function                                                           | 124 |

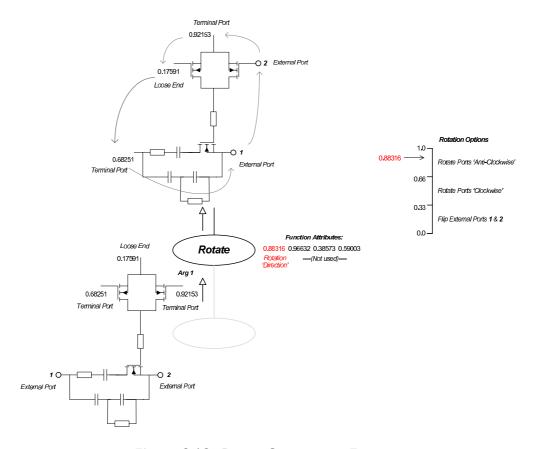

| 6.16 | Rotate Construction Function                                                           | 125 |

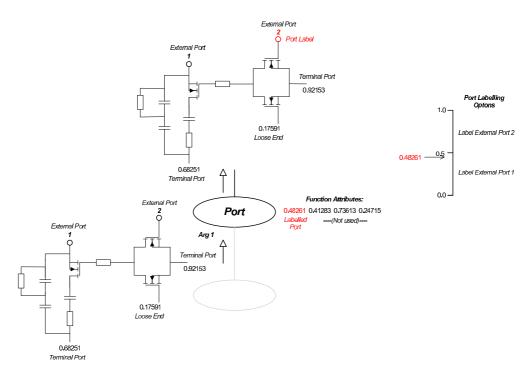

| 6.17 | Port Construction Function                                                             | 126 |

| 6.18 | Multi-Wire Circuit Embryo                                                              | 128 |

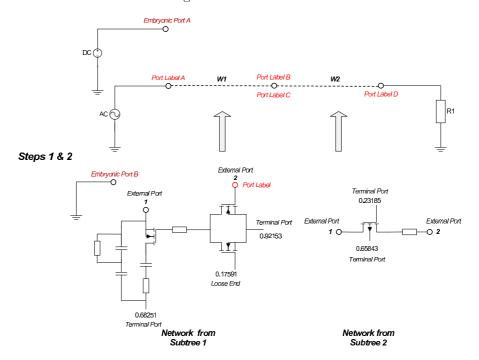

| 6.19 | Steps 1 & 2 of Circuit Finalisation                                                    | 130 |

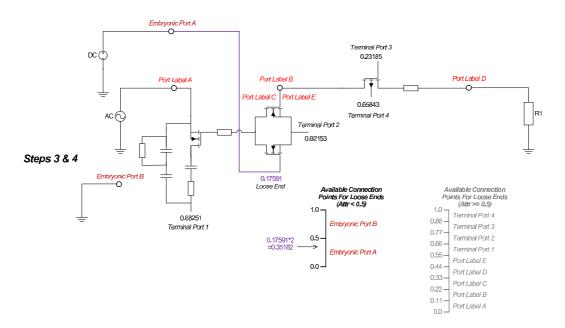

| 6.20 | Steps 3 & 4 of Circuit Finalisation                                                    | 131 |

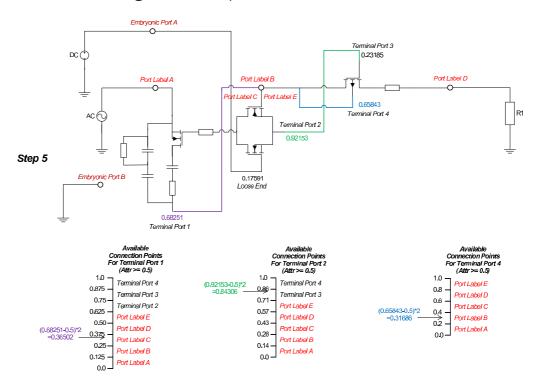

| 6.21 | Step 5 of Circuit Finalisation                                                         | 131 |

| 6.22 | GA Tree Crossover                                                                      | 134 |

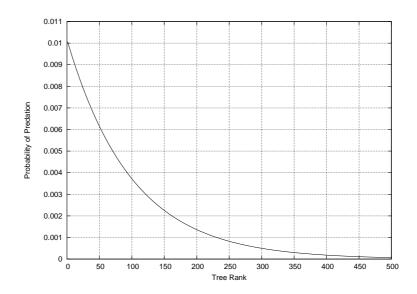

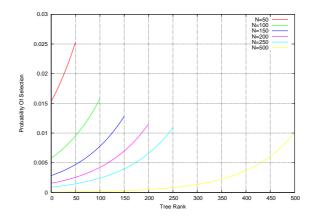

| 6.23 | Probability of Predation Based on Tree Rank                                            | 137 |

| 6.24 | Pole Zero Fitness Function                                                             | 138 |

| 6.25 | Distance Score Coefficient Curve for $P_{dist}=10000~\&~P_{lin}=0.5~\dots$             | 141 |

| 7.1  | Ideal 4th Order Chebyshev                                                              | 146 |

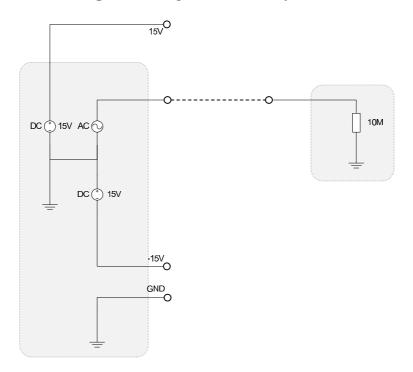

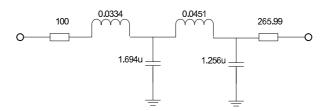

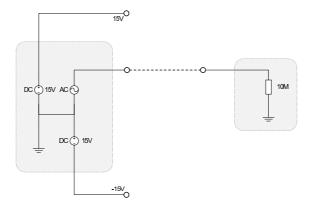

| 7.2  | Embryonic Circuit                                                                      | 147 |

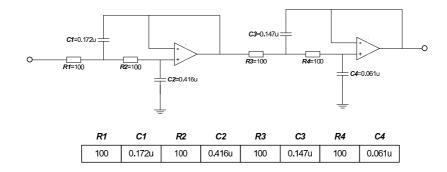

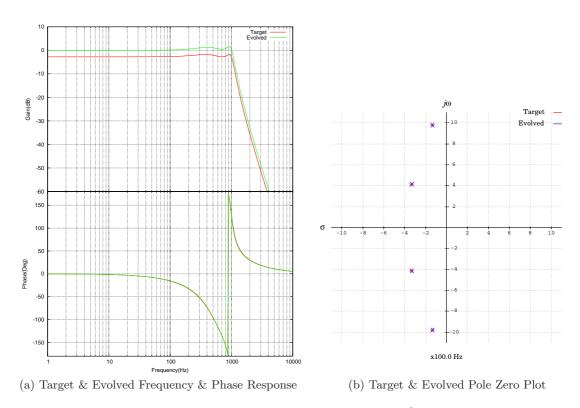

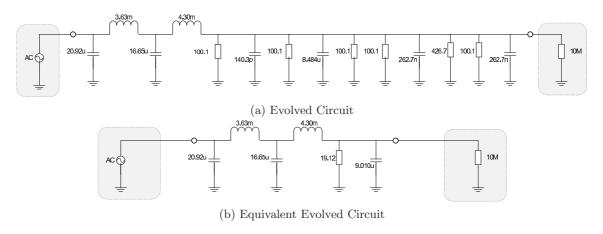

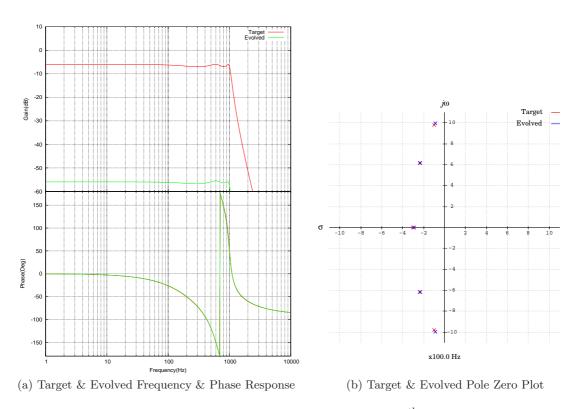

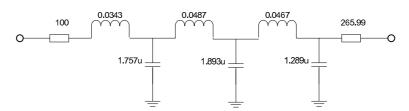

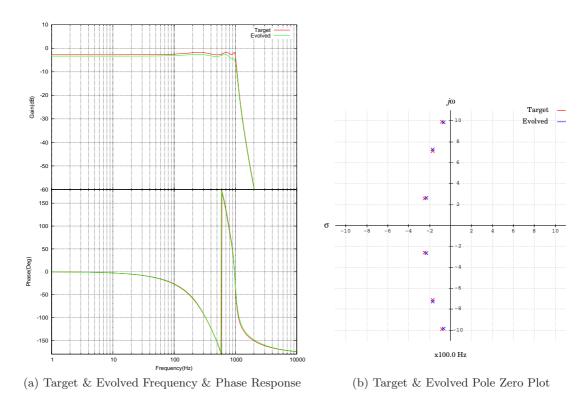

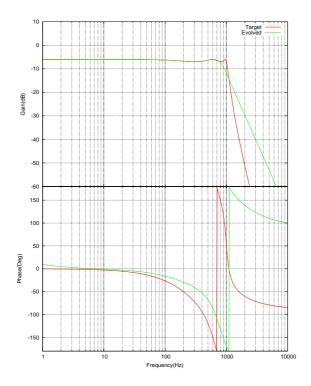

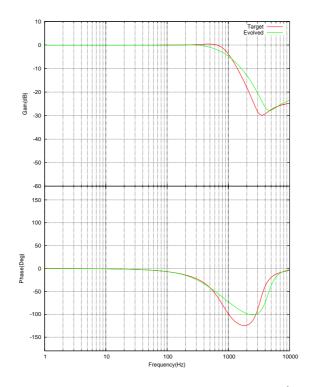

| 7.3  | Target & Evolved Circuit Characteristics Of $4^{\mathrm{th}}$ Order Chebyshev Filter   | 148 |

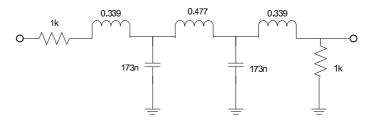

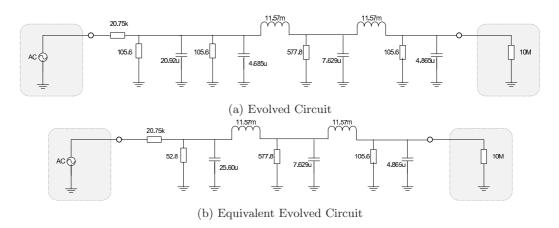

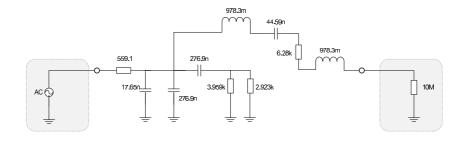

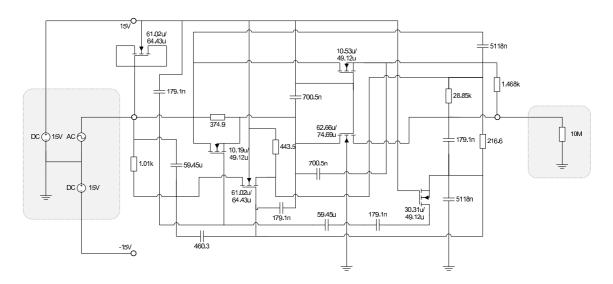

| 7.4  | Actual & Equivalent Evolved Circuits                                                   | 148 |

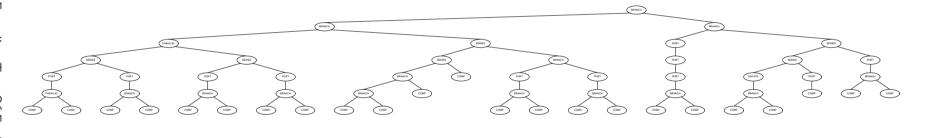

| 7.5  | Encoding Tree Of Evolved Circuit                                                       | 148 |

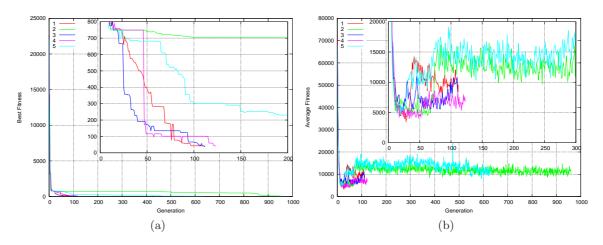

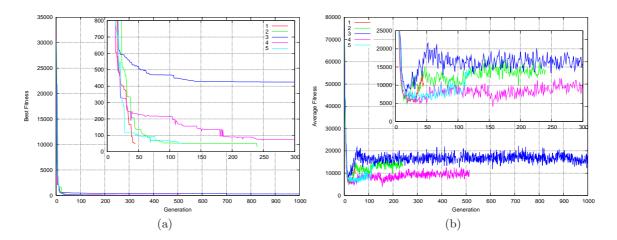

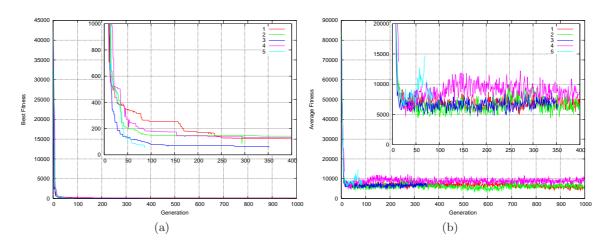

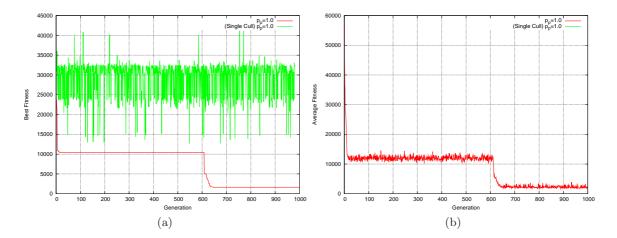

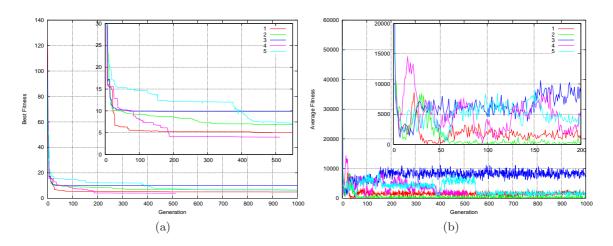

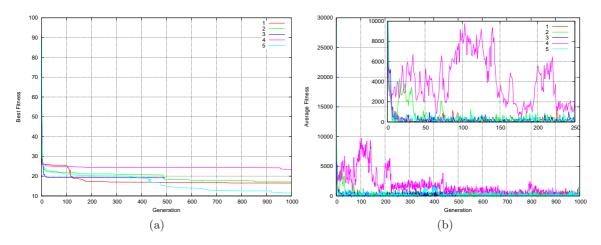

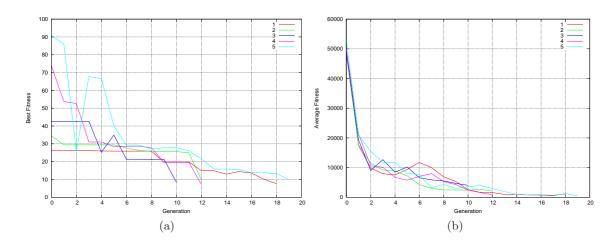

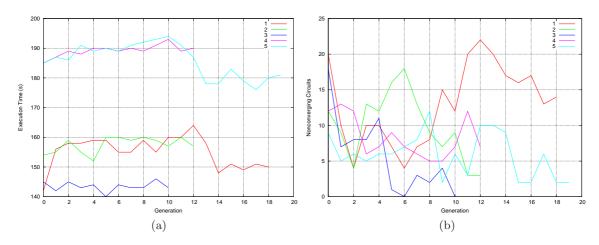

| 7.6  | Peak & Average Fitness Graphs of Five Runs of $4^{\rm th}{\rm Order}$ Chebyshev Filter | 149 |

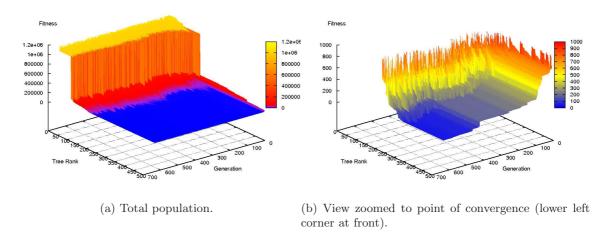

| 7.7  | Population Over Total Run of Experiment                                                | 149 |

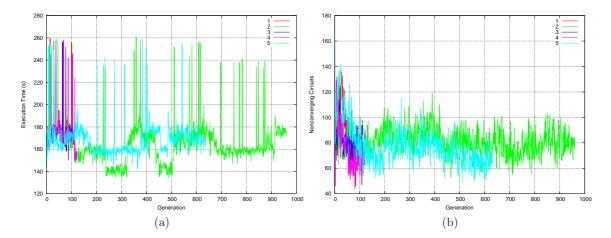

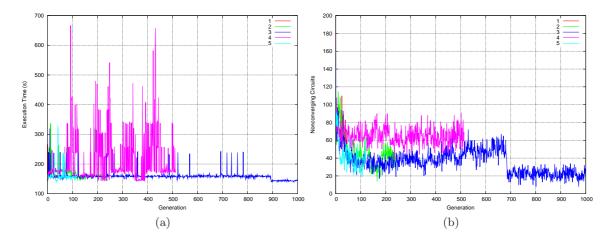

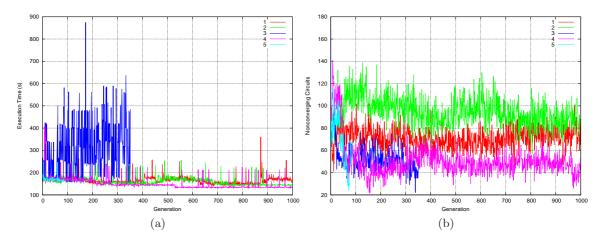

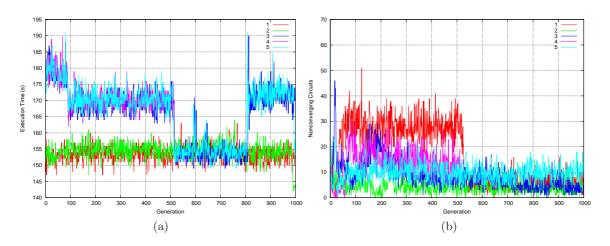

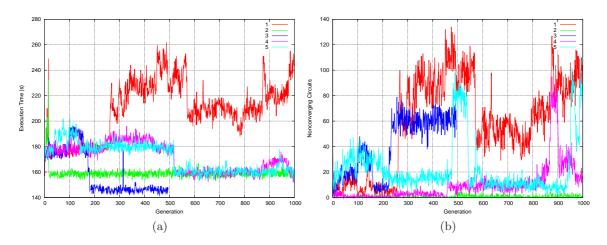

| 7.8  | Time & Non-Convergence Graphs of Five Runs of 4 <sup>th</sup> Order Chebyshev Filter   | 150 |

| 7.9  | Ideal 5th Order Chebyshev                                                                         | 50 |

|------|---------------------------------------------------------------------------------------------------|----|

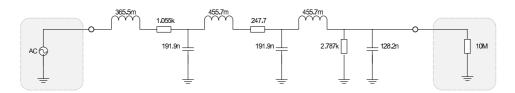

| 7.10 | Target & Evolved Circuit Characteristics Of $5^{\rm th}$ Order Chebyshev Filter 15                | 51 |

| 7.11 | Actual & Equivalent Evolved Circuits                                                              | 51 |

| 7.12 | Encoding Tree Of Evolved Circuit                                                                  | 52 |

| 7.13 | Peak & Average Fitness Graphs of Five Runs of $5^{\rm th}$ Order Chebyshev Filter 15              | 52 |

| 7.14 | Time & Non-Convergence Graphs of Five Runs of $5^{\rm th}$ Order Chebyshev Filter 15              | 53 |

| 7.15 | Ideal 6th Order Chebyshev                                                                         | 53 |

| 7.16 | Target & Evolved Circuit Characteristics Of $6^{\mathrm{th}}$ Order Chebyshev Filter 15           | 54 |

| 7.17 | Evolved Circuit                                                                                   | 54 |

| 7.18 | Encoding Tree Of Evolved Circuit                                                                  | 54 |

| 7.19 | Peak & Average Fitness Graphs of Five Runs of $6^{\mathrm{th}}\mathrm{Order}$ Chebyshev Filter 15 | 55 |

| 7.20 | Time & Non-Convergence Graphs of Five Runs of $6^{\mathrm{th}}\mathrm{Order}$ Chebyshev Filter 15 | 55 |

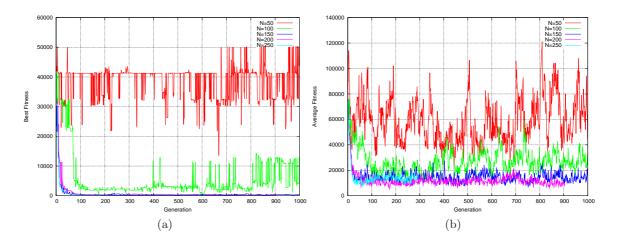

| 7.21 | Peak & Average Fitness Graphs Of Varying Values Of $N$                                            | 61 |

| 7.22 | Peak & Average Fitness Graphs Of Varying Values Of $p_c$                                          | 62 |

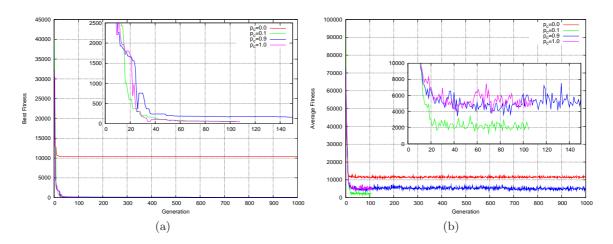

| 7.23 | Peak & Average Fitness Graphs Of Varying Values Of $p_m$                                          | 63 |

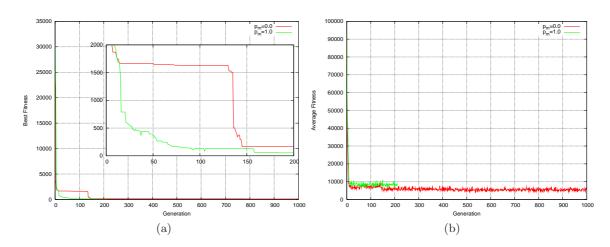

| 7.24 | Peak & Average Fitness Graphs Of Varying Values Of $p_p$                                          | 65 |

| 7.25 | Probability Curves For Different Population Sizes                                                 | 66 |

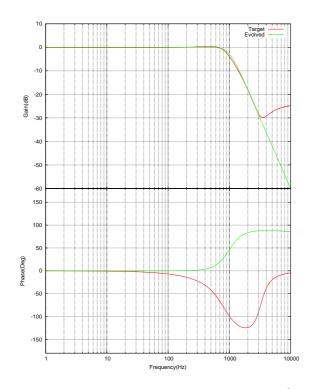

| 7.26 | Target & Evolved Circuit Characteristics Of Shape-Fitted 5 <sup>th</sup> Order Chebyshev  Filter  | 70 |

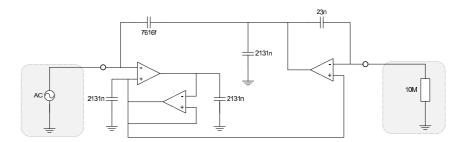

| 7.27 | Evolved Circuit                                                                                   | 70 |

| 7.28 | Encoding Tree Of Evolved Circuit                                                                  | 70 |

| 7.29 | Peak & Average Fitness Graphs of Five Runs                                                                  | 171 |

|------|-------------------------------------------------------------------------------------------------------------|-----|

| 7.30 | Time & Non-Convergence Graphs of Five Runs of Shape-Fitted $5^{\rm th}$ Order Chebyshev Filter              | 171 |

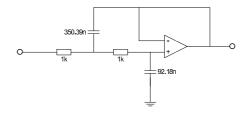

| 7.31 | Sallen-Key Target Circuit                                                                                   | 173 |

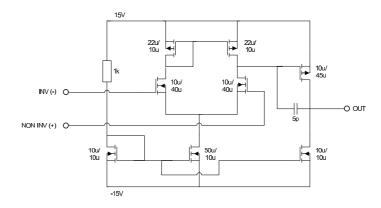

| 7.32 | Two Stage CMOS Operational Amplifier                                                                        | 173 |

| 7.33 | Embryo Circuit                                                                                              | 173 |

| 7.34 | Target & Evolved Circuit Characteristics of $2^{\rm nd}$ Order Sallen-Key                                   | 175 |

| 7.35 | Evolved Circuit                                                                                             | 176 |

| 7.36 | Encoding Tree Of Evolved Circuit                                                                            | 177 |

| 7.37 | Peak & Average Fitness Graphs of Five Runs                                                                  | 178 |

| 7.38 | Time & Non-Convergence Graphs of Five Runs of $2^{\rm nd}{\rm Order~Sallen\text{-}Key}$                     | 178 |

| 7.39 | Target & Evolved Circuit Characteristics of $2^{\rm nd}{\rm Order}$ Sallen-Key $\ \ldots \ \ldots \ \ldots$ | 180 |

| 7.40 | Evolved Circuit                                                                                             | 180 |

| 7.41 | Encoding Tree Of Evolved Circuit                                                                            | 180 |

| 7.42 | Peak & Average Fitness Graphs of Five Runs                                                                  | 181 |

| 7.43 | Time & Non-Convergence Graphs of Five Runs of $2^{\rm nd}{\rm Order}$ Sallen-Key $\ \ldots \ \ldots$        | 181 |

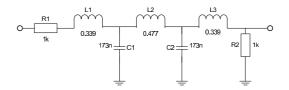

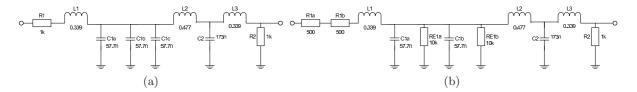

| 7.44 | Filter Circuit                                                                                              | 185 |

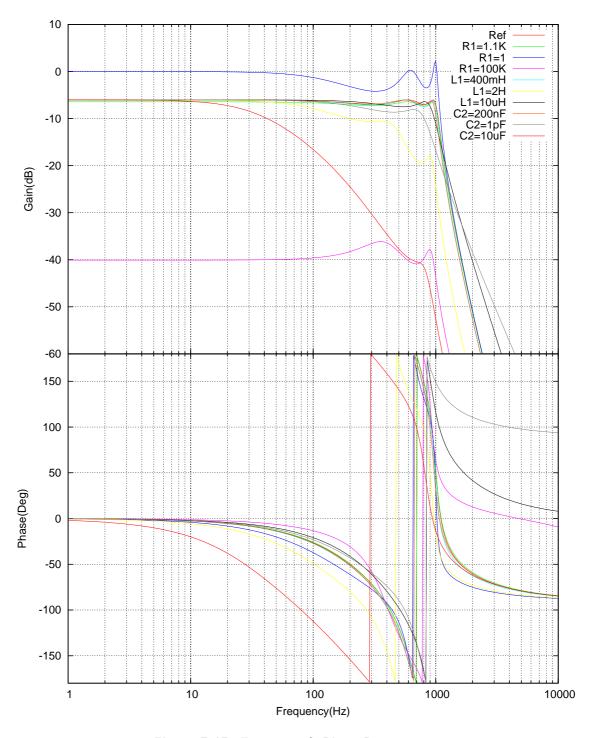

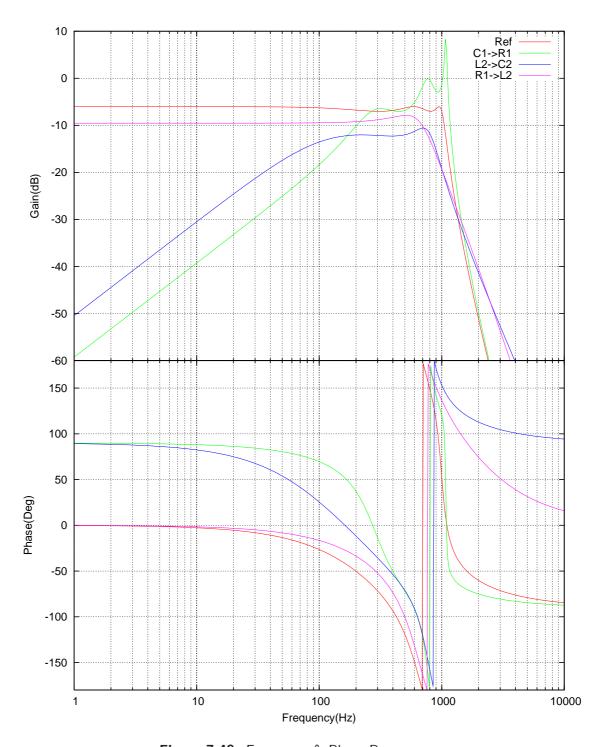

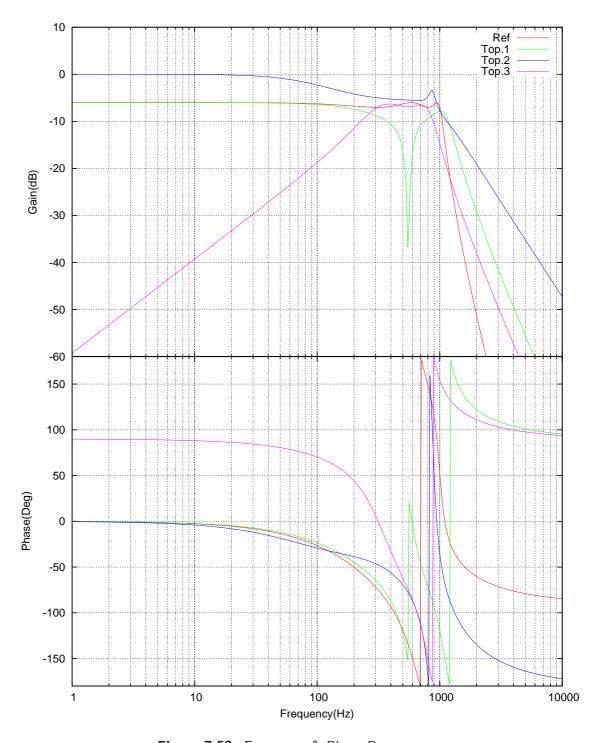

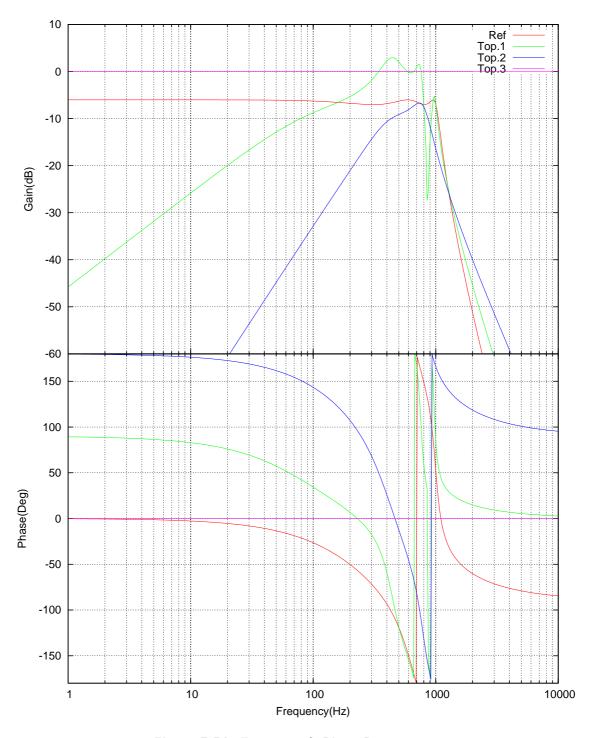

| 7.45 | Frequency & Phase Responses                                                                                 | 188 |

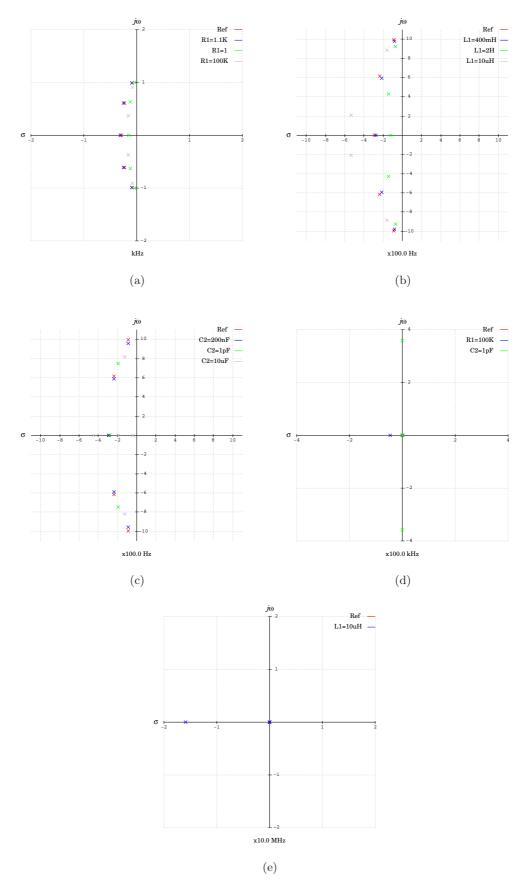

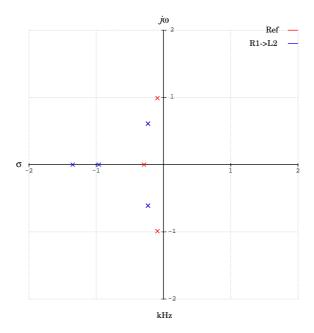

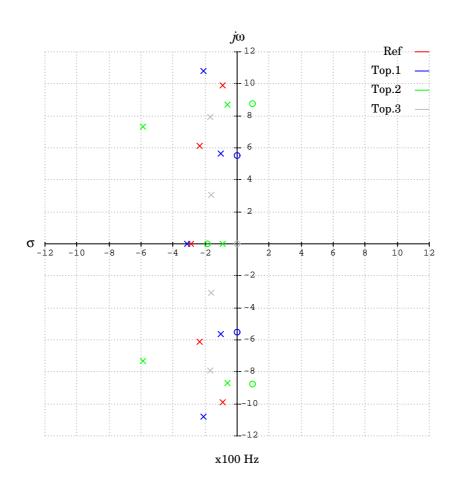

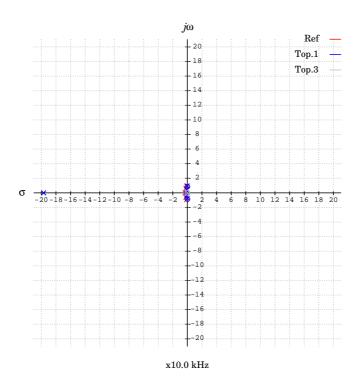

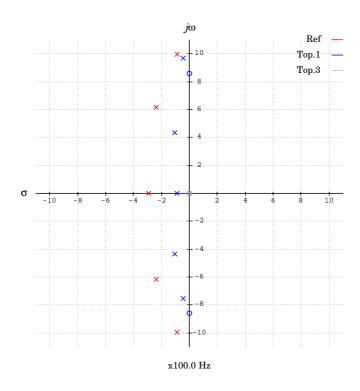

| 7.46 | Pole Zero Plot Of Modified Circuits                                                                         | 189 |

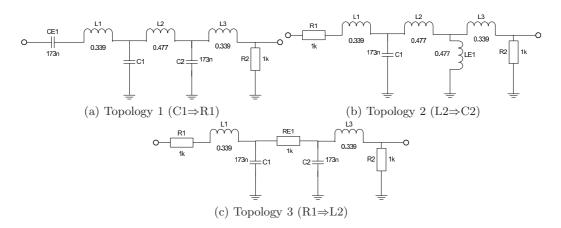

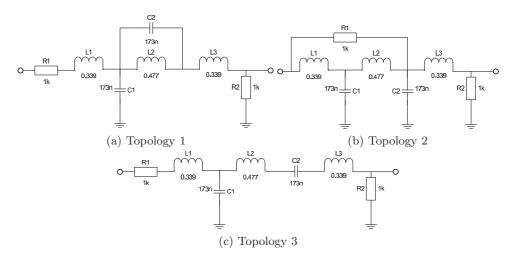

| 7.47 | Circuit Topologies Used in Experiment 12                                                                    | 190 |

| 7 48 | Pole Zero Plot Of Modified Circuits                                                                         | 191 |

| 7.49 | Frequency & Phase Responses              | 192 |

|------|------------------------------------------|-----|

| 7.50 | Circuit Topologies Used in Experiment 13 | 193 |

| 7.51 | Pole Zero Plot Of Modified Circuits      | 193 |

| 7.52 | Frequency & Phase Responses              | 194 |

| 7.53 | Circuit Topologies Used in Experiment 14 | 195 |

| 7.54 | Frequency & Phase Responses              | 196 |

| 7.55 | Pole Zero Plot Of Modified Circuits      | 197 |

| 7.56 | Examples Of Replicated Components        | 200 |

# List of Tables

| 3.1 | Level of Design Automation Achieved by Reviewed SA & GA Methods 51       |

|-----|--------------------------------------------------------------------------|

| 3.2 | Level of Design Automation Achieved by Reviewed Miscellaneous Methods 52 |

| 3.3 | Quality of Results Achieved by Reviewed Methods                          |

| 3.4 | Ability of Reviewed Methods to Discover Novel Circuits                   |

| 3.5 | Circuit Evaluation & Measurement Strategies of Reviewed Methods 62       |

| 4.1 | Example Schemata For Binary Encoding, $L=3$                              |

| 5.1 | Non-Covergence Mechanisms For Common SPICE Analysis Types 102            |

| 6.1 | Recognised Component Types                                               |

| 7.1 | Synthesis Results Summary                                                |

| 7.2 | Synthesis Results Summary                                                |

| 7.3 | Synthesis Results Summary                                                |

| 7.4 | Summary of Population Size Experiment                                    |

| 7.5 | Summary of Crossover Rate Experiment                                     |

| 7.6 | Summary of Mutation Rate Experiment                                      |

| 7.7  | Summary of Predation Rate Experiment                                               |

|------|------------------------------------------------------------------------------------|

| 7.8  | Differences Between $p_{i_{max}}$ & $p_{i_{min}}$ For Varying $N$                  |

| 7.9  | Best fitness values found in population size experiments after 50,000 circuits had |

|      | been trialled. Generation in which circuit was found is shown in brackets 167      |

| 7.10 | Synthesis Results Summary                                                          |

| 7.11 | Synthesis Results Summary                                                          |

| 7.12 | Synthesis Results Summary                                                          |

| 7.13 | Modified Component Values                                                          |

| A 1  |                                                                                    |

| A.1  | Summary of Initial Experiments Run Times                                           |

| A.2  | Summary of Population Size Experiments Run Times                                   |

| A.3  | Summary of Predation Type Experiments Run Times                                    |

| A.4  | Summary of Crossover Experiments Run Times                                         |

| A.5  | Summary of Mutation Experiments Run Times                                          |

| A.6  | Summary of Fitness Function Comparison Experiments Run Times                       |

| A.7  | Summary of Active Filter Experiments Run Times                                     |

## Chapter 1

## INTRODUCTION & MOTIVATION

The modern world is digital. The modern system-on-chip (SoC) application specific integrated circuit (ASIC) has permeated almost every aspect of life. The internet is ubiquitous, and the consumer is now able to choose from a plethora of digital gadgetry: iPods and personal digital music players, digital cameras, satellite navigation systems and portable video game systems are just a few. And, of course, mobile phones continue to merge all of these devices, and more, into one device. Home cinema systems, high definition digital televisions and digital BluRay players are just some of the other digital innovations that consumers now enjoy. Even more every day items like microwaves, washing machines and even cars now rely heavily on digital technology. The modern world is indeed digital.

With the exception, of course, that it is not. Not by any means. It is certainly true that many applications that were once analogue have now been replaced by more efficient, better, faster, smaller and cheaper digital alternatives and it is safe to say that this has brought about a digital revolution of sorts, but analogue systems and circuitry will always be needed. The reason for this is simple: the physical world is analogue. Digital systems must interface to the analogue world, and at its root, everything is analogue in nature. Even digital circuitry itself is in reality analogue circuitry designed to operate in only one of two allowable states. Digital is a simplified approximation of analogue. Without analogue circuits such as phase locked loops (PLLs), digital-to-analogue and analogue-to-digital converters (DACs/ADCs), filters, level shifters, amplifiers and voltage and power regulators, the digital world could not exist.

#### 1.1 The Analogue Design Problem

The first electronic circuits were analogue. Although the concept of digital arithmetic may be traced back at least to the early 1800s<sup>1</sup>, it was analogue circuits that dominated electronic system design during the early 20th century. Since then, approaches to analogue design have changed little, and modern analogue design is still a predominantly manual task that requires a great deal of skill and experience for all the but the most trivial of circuits, just as it did back

<sup>&</sup>lt;sup>1</sup>This is the time when George Boole invented *Boolean Algebra* and Charles Babbage first conceived of the idea of the programmable computer.

then.

#### 1.1.1 The 'Dark Arts'

Analogue engineers are far fewer in number than digital engineers, probably because analogue design is a talent which is far harder to acquire than digital design. It takes many years of experience to really become a proficient and competent analogue designer. Many tend to specialise in specific types of circuits, such as PLLs or filters. Indeed, analogue design is often perceived as something of a 'dark art', as something that is unfathomable to the uninitiated.

Entire careers can be spent becoming an expert in a given class of analogue circuit. Amplifiers are a good example. Over the decades, many different topologies have been developed for a wide variety of different applications. They make use of different techniques and strategies, designed to operate at extremely high frequencies, or dissipate very little power. Others may be designed to introduce very little distortion at audio frequencies. Filters are similar in this regard, and a good designer will gain an intuitive feel for how to tweak the circuits in order to optimise particular characteristics.

Analogue design is certainly a difficult task for the inexperienced, and in some ways it is indeed more like an art. Not only is experience important, but it also relies on intuition and to a certain extent, creativity. Unfortunately this makes it a very difficult process to automate, and is one of the reasons that it is still a predominantly manual process.

#### 1.1.2 Design Automation

The technological domination of the modern world has been made possible in part by the emergence of design automation. Modern digital designs are huge, consisting of tens or hundreds of millions of transistors. The complexity of these chips are far beyond the capacity of any one individual to fully and exhaustively comprehend, the only way they can be designed in reasonable time frames is with the use tools which automate many parts of the design process. The stages involved in the physical design of an integrated circuit are usually referred to collectively as a design flow. The output of one stage forms the input of another.

As the level and sophistication of digital design automation increased, analogue design automation has almost stagnated. The gap between the two has now widened to a great extent, and only serves to highlight how under developed analogue design automation really is. The result is that digital circuits of a given level of functional complexity will typically take far less time to develop than analogue circuits of a similar complexity.

However, as technology has developed, there have certainly been *some* advances in analogue design techniques. New types of circuits have been developed, and the advent of the digital computer has made analogue circuit simulation a reality. This is probably the single most significant development in the field of analogue design automation to date. The first analogue simulator was CANCER<sup>2</sup>, and although modern simulators, types of analysis available and the device models used have all greatly increased in sophistication<sup>3</sup> the fact remains that simulation, is still the only significant type of analogue design automation tool available, with the possible exception of optimisation.

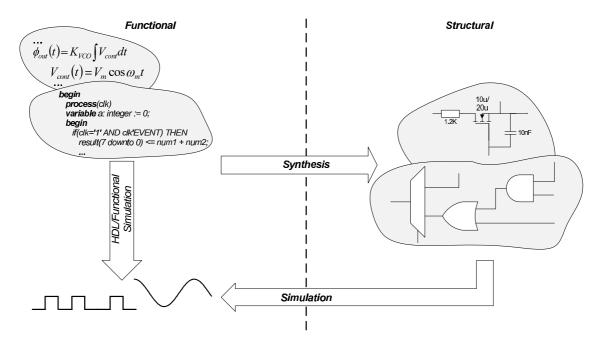

Being able to predict the characteristics and behaviour of a given circuit topology is extremely useful and is no doubt a vital part of the modern analogue design process, which is generally an iterative procedure. However, one of the most significant differences between analogue and digital design automation is the ability to effectively do the opposite; that is, to take a required circuit behaviour and from that generate a suitable circuit topology. This process is circuit synthesis. Figure 1.1 illustrates this.

#### 1.1.3 The Digital/Analogue Split

Analogue circuits and sub-systems are crucial parts of modern Systems-on-Chip (SoCs), whether mixed signal or 'purely' digital. Even digital SoCs will have *some* analogue circuitry, even if it is only to do with clock signal generation or power regulation/control. Purely analogue SoCs are also quite rare.

Mixed signal SoCs, however, are becoming increasingly common as more and more functions

<sup>&</sup>lt;sup>2</sup>CANCER was developed in the 1960s; SPICE1 was in fact a derivative of this.

<sup>&</sup>lt;sup>3</sup>Much of this could not have been possible without the increasing computational power of the digital computer.

Figure 1.1: Relationship between synthesis & simulation

are integrated into modern Application Specific Integrated Circuits (ASICs). However, even SoCs which derive a significant part of their functionality from analogue circuits have a relatively small chip area dedicated to them. Despite this, the design time and effort of the analogue portion of the design is significantly higher than the digital portion [46].

This split is due to two reasons. The first is concerned with required chip area. In terms of number of components, analogue circuits are far, far smaller than digital. This is because analogue circuits tend to exploit the full range of physical properties of the transistors and other components used in them, whereas digital circuits are made up of huge numbers of transistors, with each one acting as a very simple switch. Therefore, a small number of devices can result in very complex behaviour in an analogue circuit, whereas a digital circuit will require many more devices to exhibit a similar level of functional complexity.

The second reason, to do with design time and effort, is that digital design automation is in a considerably more advanced state than analogue design automation. Analogue designs will usually absorb many more man-hours of design time than a comparable digital design.

#### 1.1.4 Circuit Topology, Sizing & Layout

In the digital design flow, the function of the circuit is usually expressed in a highly abstracted form, and a hardware description language (HDL) is most often used as the medium. There are two clearly identifiable steps in converting the abstracted functional definition into a circuit layout ready to be manufactured. It is first synthesised in order to produce a *netlist*, and then that netlist is *laid out*; it goes through a *place and route* process.

In contrast, none of these steps exist for analogue in an automated capacity. There is, however, a possible exception to this in the form of circuit optimisation. Analogue circuits must be sized, the components must be given suitable values and any transistors must be given suitable dimensions. Optimisation tools do exist for analogue circuits. They usually require an initial guess of the component sizes to be provided. A search is then performed to find values that result in a closer fit to the specified circuit characteristics or behaviours. There are many such characteristics that may be optimised. This may include design centering, where components are sized such that the performance of the analogue circuit is centered in an allowable range, reducing the likelihood that variations in component value will push the circuit out of specification.

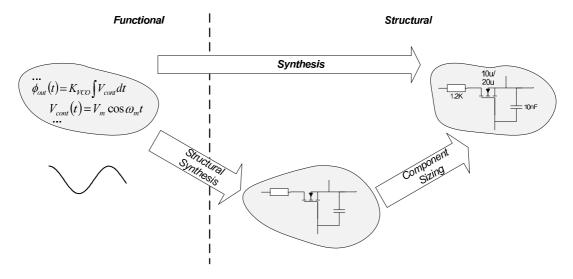

**Figure 1.2:** Component sizing can be considered to be part of the synthesis process for analogue circuits

There is no real digital equivalent to circuit sizing primarily because digital synthesis produces a netlist of predesigned *cells*. The component values in an analogue circuit have a direct impact on its functionality. An unsized netlist, which contains no component values would

therefore be considered to be incomplete. In that sense it would seem natural to include circuit sizing as a part of the synthesis process, as shown in figure 1.2.

The only automated tools exist that assist in some aspect of the *design* of analogue circuits, then, are optimisation tools of various kinds. While useful, this leaves out the majority of the design process which must still be done manually. Simulation, while vital, assists with *verification* of a circuit rather than directly with its design.

#### 1.2 The Analogue Synthesis Problem

No commercially available mature analogue circuit synthesis tools currently exist, despite digital circuit synthesis tools being ubiquitous in the modern design flow. Clearly, such a tool would be extremely useful, so there must be a good reason why this is so.

There have been a number of attempts at tackling this problem, with a range of different strategies being employed. However, to date the problem of analogue circuit synthesis has resisted all attempts to develop a satisfactory solution. The absence of any real form of synthesis from the modern analogue design flow and the corresponding lack of a commercial supply of such tools is clear evidence of this. Because synthesis is highly desirable from an engineering view point, there would be a significant market for a usable, reliable and robust analogue circuit synthesis tool. Analogue synthesis is difficult. *Extremely* difficult.

The existence of digital synthesis plays a role in creating the desire for an analogue counterpart. The success of digital design automation tools make analogue design automation conspicuous by its absence. The problems faced by the two tasks differ considerably. Digital synthesis tools use predefined rules to break down the specified digital behaviour into a collection of primitive digital operations which can be mapped directly onto digital cells [18]. These cells are sub-circuits which have a precisely defined functionality. The process of digital synthesis produces a topology of interconnected cells which is logically identical to the specified circuit function.

This approach is simply not applicable to analogue circuits. While digital behaviour is

usually specified with the use a suitable HDL, there is no commonly used equivalent in the analogue world (although such HDLs do exist [10]). Even if there were, such complex behaviour cannot easily be broken down into simpler operations or behaviours. Analogue sub-circuits can never have such precisely defined behaviour as digital cells do, and there is no guarantee that any given collection of analogue sub-circuits would be able to produce the required functionality of the original specification. This means that any truly universal analogue synthesis tool would need to build a netlist not out of cells or sub-circuits, but out of transistors and other primitive components. This is another key difference between analogue and digital synthesis.

#### 1.2.1 Previous Research

Due to the lack of any obvious best or systematic way to perform analogue synthesis, a variety of approaches have been employed in experimental synthesis systems. Some methods attempt to mimic the digital synthesis process as far as possible, some methods are search based and others try to mimic human behaviour when designing a circuit. The following summary is by no means exhaustive. All that have been tried, however, share at best limited success.

Search algorithms are the most common approach. This usually involves the repetition of a 'generate-and-test' sequence. Trial circuits are generated, measured in some way to determine how suitable a solution it is, and then those results are used to guide the search from that point. This is of course in sharp contrast to the inner workings of a digital synthesis tool.

Two popular generate-and-test search algorithms that have been applied to this problem are simulated annealing (SA) [25] and genetic algorithms (GA) [20]. These are two very different approaches to searching through a 'solution space' of possible circuits, although the overall structure of both algorithms is the same. Both typically require a great number of iterations and both will trial a great number of unsuitable circuits. The difference lies in how the search is guided, or in other words, how a new solution point is selected for evaluation and how the results of each circuit measurement influence this. There is a strong element of probabilistic decision making in both.

HDL-based approaches try to mimic digital synthesis tools to an extent, and accept analogue

behavioural specification in the form of an analogue HDL. This HDL source code is then parsed. Structure is derived from the resulting parse tree and a high level topology of interconnected analogue cells is formed. These analogue cells are then mapped onto predefined transistor level netlists, and various optimisation algorithms are then applied to size these subcircuits. There is usually an optimisation step required in order to size the analogue cells. Also, only a small subset of the HDL used is usually accepted as synthesisable.

Artificial intelligence based approaches have also been applied to this problem in the form of expert systems. The idea behind this is to try to mimic the mental process a human analogue circuit designer uses and try to attack the problem hierarchically. A knowledge base of predefined sub-circuit topologies is used by these systems, which mimics the analogue knowledge an experienced designer would have.

Almost all of the experimental solutions, however, are in various ways really quite restricted, as discussed in section 3.2.2. They tend to have the ability to deal with a small number of topologies or behaviours. Most are either inherently limited, or are bound by their implementation and do not allow complete freedom in topology generation.

#### 1.3 Research Overview

As presented in Chapter 3, the majority of previous research has been rather limited in scope. With a few notable exceptions [30][50][36], none of it has investigated the generation of topologies with complete freedom. Most research has focused on synthesis methods which require the circuit topology to be provided, either implicitly or explicitly (see section 3.2). Essentially, they just perform circuit sizing and there is little real difference between these approaches and optimisation. Other methods have the ability to perform limited topology synthesis, but only at a high level. They arrange interconnections of subcircuits with predefined transistor-level topologies. They typically also size these subcircuits, but they are still inherently limited by the range and quality of these predefined subtopologies. Section 3.2.2 covers these methods in more detail.

The systems which genuinely allow significant freedom in topology generation are those

based on fairly complex implementations of genetic algorithms, many of which are based on genetic programming (GP) [30] [50]. Section 3.2.2 presents examples of GP and GA-based synthesis systems. GP allows the generation of a circuit of unrestricted size, within limits, which is something that more traditional genetic algorithms do not allow. Other, non-GP GA implementations [36] also allow this level of freedom. Therefore, the research previously conducted would suggest that only certain GA implementations have the potential to fill the topology-generation gap in the analogue design flow illustrated in figure 1.2. Chapter 4 presents GAs and GP in detail.

#### 1.3.1 Research Objectives

Despite a number of experimental analogue synthesis systems being developed, as already discussed, commercial tools are still not a reality. Analogue synthesis is still not a real, commonly used and accepted part of the modern design flow and analogue design remains a manually intensive task. Clearly, all previous experimental systems have been in some way unsatisfactory. It seems reasonable that any genuinely useful synthesis system would need satisfy the following criteria:

Automation. There is a minimum level of automation required in order to reduce a significant amount of human design effort. Identifiable levels of analogue design automation are rather coarse, and beyond the 'finishing off' step of circuit sizing (optimisation) which can already be automated, the most significant remaining task is topology generation, as shown in figure 1.2. Any useful synthesis system must automate topology generation, and ideally it must also perform circuit sizing.

Robustness. Digital synthesis tools reliably produce a netlist of cells. In general, they only fail to do this when fed with badly written HDL source code. Provided that a good quality behavioural specification is input, a corresponding netlist is produced. The digital design flow would become much more difficult to use if this were not the case. Analogue synthesis tools must achieve a similar level of reliability, they must be *robust*. Much of the previous research has produced experimental tools which are not guaranteed to produce any useful circuit at all. Not only can two separate runs using the same inputs produce quite different circuits, but they

may produce no circuit at all.

Scope/Generality. Any tool which is restricted to only a very narrow range of circuits would obviously be of limited use. Digital synthesis tools can cope with virtually any required functionality. A useful analogue synthesis tool must be able to cope with as wide a range of circuit behaviours as possible.

**Execution time.** One of the primary goals of automation is reduce the required time to perform a particular task. While this is not the only benefit of automation, it is an important one. A synthesis tool would ultimately be of little practical use if it took significantly longer to produce a given circuit than a human designer.

Given the above criteria, the objectives of this research are, having implemented a genetic algorithm which achieves a high level of automation and generality, to:

- Investigate the robustness of a genetic algorithm in terms of its sensitivity to its control parameters and its corresponding ability to reliably generate a useful circuit.

- Identify any obvious weaknesses or issues in genetic algorithms which may prevent them from satisfying the above criteria.

- Determine whether genetic algorithms have the potential to form the basis of a *realistically* usable design tool.

In particular, a realistically usable design tool would be able to synthesise analogue circuits which may be found on a typical modern analogue SoC. Active and passive filters and amplifiers, operating at frequencies of a few KHz up to hundreds of MHz. Such a system would ideally also be able to synthesise more complex circuits such as PLLs, and the analogue portions of digital-to-analogue, and analogue-to-digital converters.

#### 1.4 Thesis Contributions

1. An investigation into how *practically useful* Genetic Algorithms are for analogue circuit design. Some important characteristics which have a direct impact on this, of both analogue

- circuits and Genetic Algorithms, are identified.

- 2. Developed a Genetic Algorithm implementation, using a tree encoding method similar to that used by Genetic Programming, specifically tailored for analogue synthesis. Unlike Genetic Programming, this implementation does not involve the overhead of parsing and executing LISP programs.

- 3. Developed a Genetic Algorithm implementation, specifically tailored for analogue synthesis, which can accept an arbitrary amount of predefined knowledge and can process arbitrarily constrained problems.

- 4. Developed a novel Genetic Algorithm fitness function based on pole-zero analysis.

- 5. An investigation into the mutability of both the topology and sizing of analogue circuits.

- 6. Developed a set of tools for analysing the applicability of SPICE in the role of circuit evaluator for Genetic Algorithm fitness functions.

#### 1.5 Thesis Structure

- Chapter 2 Electronic Design Automation: A Brief Introduction. This chapter provides an introduction to Electronic Design Automation (EDA), and includes a history of how it developed and explains why the state of the art is as it is. Digital and analogue EDA are compared and significant differences are highlighted.

- Chapter 3 Approaches to Analogue Synthesis: Attempts At Solving The Problem. A look at previous attempts at creating an analogue synthesis tool. A comparison of the wide variety of approaches which have been employed in an attempt to tackle this difficult problem is presented. Includes a short survey of the literature.

- Chapter 4 Genetic Algorithms. This chapter examines some of the finer details of Genetic Algorithms, and also takes a look at Genetic Programming.

- Chapter 5 SPICE Simulation & Other GA Issues. SPICE is a well known simulation tool, something of an 'industry standard'. It is also a very common element of many Genetic Algorithms which have been designed for analogue circuit synthesis. It is capable

of producing highly accurate circuit simulations, but there are many hurdles which may prevent this. This chapter examines some of these hurdles, and what effect they may have on Genetic Algorithms. Issues related to circuit encoding are also considered.

- Chapter 6 A Genetic Algorithm System For Analogue Synthesis. A detailed presentation of an analogue synthesis system based on Genetic Algorithms. A novel fitness function based on pole-zero analysis is also presented.

- Chapter 7 Case Studies. This chapter contains the results of a series of experiments, including the synthesis of some analogue filters, the effect of varying control parameters of the Genetic Algorithm. Finally, an investigation is presented into the sensitivity of analogue circuits to changes in their sizing and topology.

- Chapter 8 Conclusions. The central conclusions of this thesis are presented, and interesting directions of possible future work are discussed.

## Chapter 2

# ELECTRONIC DESIGN AUTOMATION: A BRIEF INTRODUCTION

Since the first integrated circuit (IC) was produced in 1958, development of ICs has come a long way. Their complexity, as measured by the number of transistors placed on a single die has increased by a factor of a million over the last forty years and is still increasing. From the early Intel 4004 containing just 2,300 transistors [1] to the Intel Itanium Tukwila containing a staggering 2 billion [2], the challenges associated with IC design have changed beyond all recognition. It simply would not be possible to produce modern ICs without heavily automating the design process, and as a result of the ever increasing difficulties associated with ASIC design the field of Electronic Design Automation (EDA) came into being.

This chapter discusses what EDA is, how and why it developed and examines the current state of the art. While this text is focused on high level analogue circuit synthesis, it is also useful to briefly examine digital EDA to serve as a reference point. Indeed, the question of analogue synthesis exists precisely because such a process exists for digital systems and has proved to be indispensable.

#### 2.1 Introduction to EDA

Electronic Design Automation tools are anything that assists with the design specification, simulation, verification or realisation of integrated circuits, field programmable gate arrays (FPGAs), printed circuit boards or electronic systems. A modern design flow for electronic systems consists of a series of EDA stages. Such a flow takes a human-defined specification of some kind and ultimately produces a circuit representation that is suitable for direct implementation or manufacture.

A brief summary of design automation, focused mainly on tools for ICs is presented here. Not only has the development of ICs provided the main driving force in the development of EDA, this is also the area that EDA is most needed. The summary is divided into four parts. Section 2.1.1 explains the role of circuit abstraction in EDA, section 2.1.2 defines more concisely what EDA is, and gives some examples of EDA tools and the roles they perform. Sections 2.1.3 and 2.1.4 describe typical modern design methods and procedures for analogue and digital circuits, to serve as a comparison between the two.

#### 2.1.1 Circuit Abstraction

Circuit abstraction is an important part of EDA. It allows circuit designs to be captured and represented in forms suitable for use at various stages in the design process. This includes the initial, human-input point of design capture, and also intermediate design representations at various stages in the design process.

Human designers can only cope with so much design complexity, and so when dealing with all but the most trivial of circuits it is necessary to abstract the design in some way. The amount of detail in a given level of abstraction is roughly inversely proportional to the size of the design, or portion of design being considered. The highest levels of abstraction are typically used for giving an overview at the top level of a design, maybe when describing the functionality of a complete SoC or microprocessor. Minute detail is not needed here and would be indigestible on such a large scale. Very low levels of abstraction, such as describing individual transistors is useful when designing a standard cell such as a logic gate or a flip-flop.

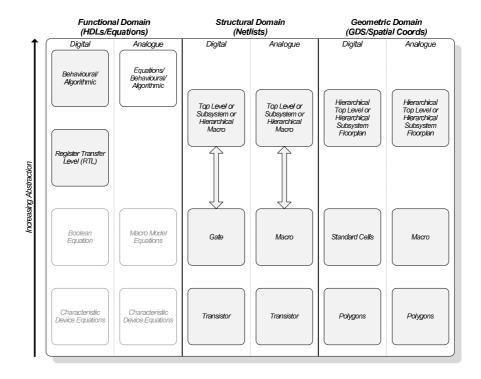

However, it is not only levels of abstraction that are of interest. Ashenden [11] also identifies three domains of abstraction - functional, structural and geometric (physical). Each domain has its own levels of abstraction. Abstraction in the functional domain describes the function and operations performed by the system. The structural domain is concerned with how the system is partitioned and connected between its partitions. The geometric domain describes how the circuit is implemented and physically laid out.

Figure 2.1 shows levels of abstraction used in a typical design flow. A behavioural system model usually specifies what is to be done, but not how it is to be done. Algorithms may often be used in a behavioural model. Register Transfer Level (RTL) modeling describes the system in terms of data storage elements, or registers. Data is transferred between registers through sections of digital logic which transform the data in some way. The next two lower levels of abstraction are in the structural domain. Gate/macro abstraction describes the design in terms of a list of sub-circuits or cells and their interconnections. The transistor level is similar, except that individual components are listed.

Despite the fact analogue and digital circuits often require different modeling techniques,

Figure 2.1: Levels of Circuit Abstraction

different abstraction levels are generally applicable to both, and will look very similar. Even a behavioural abstraction that might describe circuit function in terms of an algorithm, will allow both analogue and digital circuits to be modeled. It is important to note that there is no analogue equivalent of digital RTL abstraction. This has important implications for analogue EDA, as RTL bridges a wide gap between behavioural and gate level abstractions for digital systems.

#### 2.1.2 EDA Concepts

Most EDA tools may be considered as belonging to one of two groups: some which perform *verification* of a circuit design, and others which perform *translation* of a circuit design.

The need for translation results from the ability, and often the necessity, to capture designs at a high level of abstraction. As discussed in section 2.1.1, highly abstracted design representations deliberately lack fine detail. This allows human designers to cope with bigger designs. However a circuit must ultimately be manufactured or implemented in some way - that is, it must be realised. The design must be translated to a level of abstraction suitable for direct

implementation.

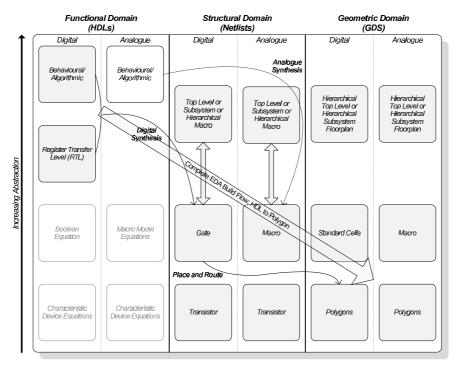

There are two important translation stages used in the design of modern ICs and FPGAs. Synthesis is the process of translating from the highest levels of abstraction to the macro, gate, or netlist level. An important feature of synthesis is that it not only translates to a lower abstraction level, it also translates between abstraction domains. The input is a high level functional description. The output is a lower level structural description. While this contains much more detail about how the circuit will be finally realised, it still cannot be directly implemented as it contains no physical or spatial information.

Figure 2.2: EDA Translation

Place and route (PNR), is the next translation stage, and translates from the netlist level into the polygon level (in the case of ASICs), or a configuration bit stream (in the case of an FPGA). It takes a list of cells and/or macros, and arranges them in physical space (the act of placing them). The design must then be routed, which connects the placed cells together in the manner described in the input netlist. Like synthesis, PNR translates between abstraction domains. In this case, from the structural to the geometric domain.

Translators provide the means to automatically convert a manually generated, highly abstracted circuit design into a form which can be directly implemented. In the case of modern

digital ICs these tools are indispensable due to the sheer size of these designs. However, the correctness of these designs must also be guaranteed. This is especially important for ICs using modern fabrication processes, as the financial overhead of producing a mask set is typically in the millions of dollars for 65nm and 45nm processes. Correcting mistakes in the design, whether physical or functional, is therefore a very expensive and time consuming task. Verification forms an extremely important part of EDA.

Different abstraction domains and levels have different verification requirements, since each abstraction domain is concerned with different aspects of the design. The checkers and verifiers introduced in this section are elaborated on in sections 2.1.3 and 2.1.4. HDL simulators are used to help verify the functionality of the design. Most HDLs have features which allow test benches to be written. This allows tests to be written. Specific stimuli can be generated, and resulting outputs from the HDL code can be captured and evaluated. Sometimes programming languages can be used in conjunction with the HDL to allow more sophisticated tests to be written. There are often entire teams dedicated to verifying the functionality of a large design.

Figure 2.3: EDA Verification

There are many different checks which need to be carried out in the geometric domain, and these are generally relevant only to ICs. Physical checks include analysis of the physical layout to check that the design rules published by the foundry are adhered to. Power simulations are also sometimes carried out to identify any areas of significant power dissipation or voltage drop within a circuit.

However, many checks are concerned with more than one abstraction domain. In digital designs, for example, logical equivalence checkers, compare representations of a design in the functional and structural domains to catch any errors that have been introduced during synthesis. A similar check, known as 'layout-versus-schematic' (LVS) compares the geometric and structural domains to catch any errors introduced during PNR.

#### 2.1.3 A Typical Design Flow For Digital ICs

The design process, or *design flow* for digital systems is very well developed. Every stage of a typical digital design flow is capable of handling modern digital systems which often contain tens or even hundreds of millions of logic gates.

One of the first stages in designing a large digital system, after specifying what the design should do, is partitioning it into a number of subsystems or blocks, in order to make the design more manageable. There are different ways to accomplish this. The design may be partitioned with regards to the functionality of each subsystem, this may make the high level or frontend part of the design process easier. However, preference instead may be given to possibly important physical constraints and subsystems defined which will be easier to layout. When a system is partitioned, it is being abstracted at a high level in the structural domain. Therefore, the overall view of the system, (also known as the system's top level), contains instantiations of these subsystems but they are only empty black boxes at this level.

After the system has been partitioned, the exact functionality of each subsystem is defined with the use of an HDL - each subsystem is abstracted at a high level in the functional domain. Human designers write HDL code, usually RTL, which precisely defines what each block does. Functional verification goes hand in hand with this process, although the tasks of writing the RTL and verifying it are usually given to different engineers. These engineers will write test benches, often in a combination of the same HDL that the RTL was written with, and common

programming languages like C++. These test benches specify logical stimuli for the HDL code, for use in logic simulation. They are also usually concerned with capturing and evaluating the output of these tests. These simulations must test the functionality defined in the RTL and show up any errors or unanticipated issues. At this point in the design cycle, the design exists in both high level structural and functional forms, but only the functional form must be verified. The partitioning of the system, or its structural form, cannot be said to be right or wrong, merely good or bad.

After the RTL has been completed and there is a reasonable level of confidence that it is correct, the frontend work is finished and the design cycle enters the *backend* stage, the target of which is to produce a *GDS database* (Graphic Data System). This is a database of polygons which a foundry will use to manufacture an integrated circuit.

The backend digital design flow makes use of pre-designed building blocks. These building blocks are usually classified as either *standard cells* or *macros*. Standard cells consist of basic logical units such as logic gates, flip flops, latches and so on. A typical cell library will not only contain cells of different functions, but a specific *type* of cell (which performs a specific function) will be further subdivided into versions of the cell which have different *drive strengths*. Macros refer to bigger, more complex cells such as memories, phase locked loops (PLLs) and digital to analogue, and analogue to digital convertors (DACs and ADCs). A library of standard cells and specialised macros will already have been designed and will be available to the tools used in a typical digital design flow.

Synthesis is performed automatically with the use of a dedicated tool - the RTL is translated into a netlist of standard cells and macros. Once this is done, the result is often verified by using a logical equivalence checker to confirm that no errors have been introduced during synthesis and the netlist represents exactly the same design as the source RTL.

The netlist must then be transformed into a GDS database, and so a PNR tool is used. The netlist specifies instances of standard cells and macros and also specifies how these are connected, so this is taken as an input by the PNR tool. The process is usually automated, although there is scope for the designer to manually specify the location of some (or, in small subsystems, all) of the standard cells, macros and the wire interconnects. In fact, it is quite

common to manually specify the location of macros as these are not only usually much bigger than the standard cells, there are often far fewer of them. Manually placing standard cells will usually only be required for high performance designs, where specific sections of the design are required to have particularly low clock skew or low propagation times. An experienced human designer will usually make a better job of this than an automated tool, but at the cost of taking considerably more time and having a much lower capacity for coping with design size.

PNR usually produces a second, final netlist in addition to the GDS database. Additional buffers may be inserted into the design during PNR, and it is important to have an updated netlist for verification purposes. Additional logical equivalence checks are often carried out between the final netlist and the original RTL to once again prove that the functionality of the design has not been unintentionally altered during the digital design flow.

Once the GDS database is obtained, further checks must be carried out to ensure that other aspects of the design are correct. LVS is performed by comparing the GDS database to the final netlist, to prove that the correct design has been laid out - it is important here to first prove that the final netlist is correct (which has already been taken care of by the logical equivalence checks).

Much of the verification and design effort of laying out a digital system is concerned with timing. Digital signals take a finite time to propagate through standard cells and macros, and balancing the arrival times of signals and clock edges is crucial. Timing analysers will trace every logical path through the subsystem and check the propagation time against predefined, or automatically calculated constraints. The propagation time of a digital signal will depend on the number and type of cells it propagates through, the drive strengths of each of those cells, and the parasitic resistance and capacitance of the metal interconnects between them. It may also be affected by signal activity on other, capacitively coupled wires which are nearby. The parasitic resistance and capacitances of each metal wire, or net of a circuit layout is calculated by an extraction tool.

The activity of signals on nearby wires has the potential to not only cause additional timing delays, but it may actually corrupt a digital signal. Excessive noise injected from other wires may flip logic bits and lead to data corruption. Signal integrity analysers are designed to recognise

situations where there is a risk of this happening.

A silicon foundry will have particular requirements and physical design rules which must be adhered to if the design is to be manufactured. These are physical layout rules, and define things like minimum wire width, maximum and minimum metal density, wire spacing rules and so on. These rules are becoming more complex with ever decreasing process geometries. Tools are available which check adherence to these rules. A rule deck is read in by the tool which describes how to check for the rules published by the foundry. This process is known by the rather vague term physical verification, although this could just as easily apply to any of the checks applied to the final layout.

Ideally, the PNR tool should produce a design which passes all these checks first time. Unfortunately, that is rarely the case for all but the simplest of designs. Human intervention is usually required, even if only to tweak the settings of the PNR tool. However, more direct intervention is usually required. Timing violations may be fixed by the human designer investigating the problem and picking new strengths or manually inserting buffers into violating paths. Signal integrity violations might require manual manipulation of specific wires, as might layout rule violations. Each time a change is made to the final layout, all of these checks are commonly run through again, to check that no new violations have been created by the changes. This process of fixing problems, and then re-checking the design is known as an engineering change order (ECO) loop.

#### 2.1.4 A Typical Design Flow For Analogue & Mixed Signal ICs

The typical design process for analogue circuits is very different to that of digital. It is much less structured and less automated, and relies much more on human experience and intuition. Analogue circuits tend to be much smaller in terms of the number of components used, and it is quite rare to find an integrated circuit which is entirely analogue. It is far more usual for analogue circuits to form subsystems within a mixed-signal SOC. Typically, analogue systems will be designed by human designers who have extensive experience with particular types of analogue circuits.

As discussed in section 2.1.3, digital design flows can be roughly divided into *frontend* and *backend* processes, with the frontend tasks being primarily concerned with the functionality of the system and high level design abstractions, whereas the backend design process is concerned more with the physical implementation of the design and low level design abstractions.

This frontend/backend split is much less applicable to analogue circuits. When forming part of a mixed signal SOC, the design and functionality of any analogue subsystems it may contain are generally regarded as backend tasks.

When considering an analogue system or subsystem as a whole, there is very little which may be defined as being equivalent to the digital notion of a frontend design cycle. The functionality of the system must be specified - this usually takes the form of a simple list of requirements that the human designer will work to. The requirements of the circuit are simply stated, and no formal method or technique is generally used to capture circuit behaviour at a high level. Analogue circuits are not usually described using a high level HDL, and although this is possible there is currently no reliable way to automatically translate between the high level behavioural HDL description and a lower level structural netlist. This is discussed in more detail in 2.3. Analogue circuits cannot yet be automatically synthesised. There is little to no high level verification to do here, other than ensuring that the specified performance requirements are sufficient for the intended application.

The analogue design cycle really begins with the human designer creating a schematic of the circuit, based on knowledge and previous experience of the circuit type in question. Essentially what is happening is that netlist, a low level structural abstraction of the circuit, is created directly by the human designer. This netlist may be a combination of transistor and macro level abstractions. Put another way, it will likely contain individual, primitive components such as transistors but if a large system is being designed then the netlist may also contain analogue macros such as operational amplifiers or current mirrors. These may be considered analogous to digital cells.

Schematic capture tools are available that allow a transistor and/or macro level netlist to be captured graphically. However, for small systems a netlist may be manually written.