# LOW POWER HIGH FAULT COVERAGE TEST TECHNIQUES FOR DIGITAL VLSI CIRCUITS

By

Abdallatif S. Abuissa

A thesis submitted to

The University of Birmingham

for the Degree of

#### **Doctor of Philosophy**

School of Electronic, Electrical and Computer Engineering College of Engineering and Physical Sciences The University of Birmingham

September 2009

#### UNIVERSITY<sup>OF</sup> BIRMINGHAM

#### **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

#### LOW POWER HIGH FAULT COVERAGE TEST TECHNIQUES FOR DIGITAL VLSI CIRCUITS

#### ABSTRACT

**T**esting of digital VLSI circuits entails many challenges as a consequence of rapid growth of semiconductor manufacturing technology and the unprecedented levels of design complexity and the gigahertz range of operating frequencies. These challenges include keeping the average and peak power dissipation and test application time within acceptable limits.

This dissertation proposes techniques to addresses these challenges during test. The first proposed technique, called bit-swapping LFSR (BS-LFSR), uses new observations concerning the output sequence of an LFSR to design a low-transition test-pattern-generator (TPG) for test-per-clock built-in self-test (BIST) to achieve reduction in the overall switching activity in the circuit-under-test (CUT). The obtained results show up to 28% power reduction for the proposed design, and up-to 63% when it is combined with another established technique. The proposed BS-LFSR is then extended for use in test-per-scan BIST. The results obtained while scanning in test vectors show up to 60% reduction in average power consumption. The BS-LFSR is then extended further to act as a multi-degree smoother for test patterns generated by conventional LFSRs before applying them to the CUT. Experimental results show up to 55% reduction in average power.

Another technique that aims to reduce peak power in scan-based BIST is presented. The new technique uses a two-phase scan-chain ordering algorithm to reduce average and peak power in scan and capture cycles. Experimental results show up to 65% and 55% reduction in average and peak power, respectively.

Finally, a technique that aims to significantly increase the fault coverage in test-perscan BIST, while keeping the test-application time short, is proposed. The results obtained show a significant improvement in fault coverage and test application time compared with other techniques.

To my mother Zuhria and my wife Bayan

To all people who love and support me

Thank you very much for everything

#### **ACKNOWLEDGMENTS**

First of all, I would like to thank my supervisor Dr. Steven F. Quigley for his support and guidance throughout this PhD. I am grateful for his invaluable help during the preparation of this thesis and several conference and journal papers. Dr. Quigley was not only a supervisor, but also a friend who gave me advice, help, counsel, and constant support during my stay in the UK.

I wish to thank Mrs Mary Winkles, the EECE postgraduate secretary, for her support and help in many occasions during the last 5 years I spent in the School of Electronic and Computer Engineering as an MSc and PhD Student.

During the period of my PhD, I met many people, either in the university or in the house. I would like to thank all of them for making life in Birmingham more enjoyable.

Last but certainly not least, I would like to thank my mother for her patience and constant prayers and my wife for her support. Also, I would like to thank my cousin Mohammed Abu-Issa, the main sponsor for my undergraduate studies, and Hani Qaddoumi Scholarship Foundation (HQSF), the main sponsor for my MSc studies. Special thanks to my cousin and friend Ayed Abu-Issa and all of my brothers, sisters, nephews, nieces and other relatives in my village Al-Jalamah – Jenin, Palestine and in Jordan.

This work was funded by Dorothy Hodgkin's Postgraduate Award (DHPA) and the School of Electronic, Electrical and Computer Engineering at the University of Birmingham, for which I am very grateful.

The viva for this thesis was held on 09/09/09. Dr Gordon Russell (University of Newcastle) was the external examiner and Mr Phil Atkins was the internal examiner. I would like to thank both of them for their constructive comments and suggestions to improve this thesis

#### **Contents**

| 1 | Intr | oduction                                                        | 1     |

|---|------|-----------------------------------------------------------------|-------|

|   | 1.1  | Automatic Test Equipment (ATE)                                  | 2     |

|   | 1.2  | Built-In Self-Test (BIST)                                       | 3     |

|   | 1.3  | Test-per-Clock and Test-per-Scan BIST                           | 4     |

|   | 1.4  | Fault Modelling and Fault Coverage                              | 5     |

|   | 1.5  | Fault Simulation                                                | 6     |

|   | 1.6  | Automatic Test Pattern Generator (ATPG)                         | 6     |

|   | 1.7  | Test Vector Generation in Scan-Based Circuits                   | 7     |

|   | 1.8  | Phase Shifters                                                  | 9     |

|   | 1.9  | Power Dissipation in Digital VLSI Circuits                      | 9     |

|   | 1.10 | Terminology Relating to Energy and Power                        | 11    |

|   | 1.11 | WSA and WT Modelling                                            | 12    |

|   | 1.12 | Average and Peak Power                                          | 13    |

|   | 1.13 | Motivation for Low Power consumption and High Fault Coverage Te | sting |

|   |      | 14                                                              |       |

|   | 1.14 | Thesis Organisation and Contribution                            | 15    |

| 2 | Prev | vious Work                                                      | 17    |

|   | 2.1  | Previous Work in Low Power Testing                              | 18    |

|   | 2.1. | 1 Low Transition TPGs                                           | 18    |

|   | 2.1. | 2 Test Vectors Reordering                                       | 20    |

|   | 2.1. | 3 Scan Cells Reordering Techniques                              | 21    |

|   | 2.1. | 4 X-Filling Techniques of Test Cubes                            | 22    |

|   | 2.1. | 5 Vector Filtering Techniques                                   | 23    |

|   | 2.1. | 6 Shift Control Techniques                                      | 23    |

|   | 2.1. | 7 Selection of LFSR Parameters                                  | 24    |

|   | 2.1. | 8 Low Power Test Vector Compaction                              | 24    |

|   | 2.1. | 9 Scan Architecture Modification                                | 25    |

|   | 2.1. | 10 Scan Clock Splitting                                         | 26    |

|   | 2.1. | 11 LFSR Reseeding and Test Data Compression Techniques          | 26    |

|   | 2.1. | 12 Low Power ATPG Algorithms                                    | 27    |

|   | 2.1.          | 13 Summary of Previous Low Power Testing Techniques                 | 28  |

|---|---------------|---------------------------------------------------------------------|-----|

|   | 2.2           | Testing for High Fault Coverage with Short Test Time (Test Energy   |     |

|   | Minimisation) |                                                                     |     |

|   | 2.3           | Contribution of the Work Presented in this Thesis                   | 31  |

| 3 | BS-           | LFSR as a Low Transition TPG for Test-per-Clock BIST                | 35  |

|   | 3.1           | The Proposed Approach to reducing the Transition Count              | 36  |

|   | 3.2           | Design of the BS-LFSR                                               | 41  |

|   | 3.3           | Randomness of the New Set of Test Vectors                           | 42  |

|   | 3.4           | Combining the BS-LFSR with other Low Power Test Techniques          | 43  |

|   | 3.5           | Experimental Results                                                | 45  |

|   | 3.6           | Conclusion                                                          | 48  |

| 4 | BS-           | LFSR as a Low Transition TPG for Test-per-Scan BIST                 | 49  |

|   | 4.1           | The Proposed Approach to Design the BS-LFSR for Scan-Based BIST     | 50  |

|   | 4.2           | Architecture of the Proposed TPG for Scan-Based BIST                | 59  |

|   | 4.3           | Experimental Results                                                | 60  |

|   | 4.4           | Conclusion                                                          | 63  |

| 5 | RLF           | FSR as a Multi-Degree Smoother for Test-per-Scan BIST               | 64  |

|   | 5.1           | Key Ideas to Reduce the Transitions at the Output Sequences of LFSR | 65  |

|   | 5.2           | Extending the Design for Multiple Scan-Chain BIST                   | 72  |

|   | 5.3           | Key Properties of the Proposed Design                               | 74  |

|   | 5.4           | Experimental Results                                                | 76  |

|   | 5.5           | Conclusion                                                          | 78  |

| 6 | Two           | o-Phase Scan-Chain Ordering Algorithm                               | 79  |

|   | 6.1           | Sources of Peak Power Violation in Scan Testing                     | 80  |

|   | 6.2           | Phase 1 of Scan-Chain Ordering Algorithm                            | 83  |

|   | 6.3           | Phase 2 of Scan Ordering Algorithm                                  | 86  |

|   | 6.4           | Experimental Results                                                | 92  |

|   | 6.5           | Conclusions                                                         | 94  |

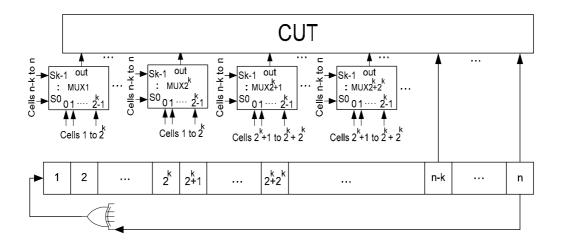

| 7 | АН            | igh Fault Coverage Technique for Test-per-Scan BIST                 | 96  |

|   | 7.1           | Key Features of the Proposed Design                                 | 97  |

|   | 7.1.          | 1 Key Idea                                                          | 97  |

|   | 7.1.          |                                                                     | he  |

|   | LFS           |                                                                     |     |

|   | 7.2           | The Proposed Design and Algorithm                                   | 102 |

|   | 7.2.1     | Identify the Hard to Detect Faults                             | 102   |

|---|-----------|----------------------------------------------------------------|-------|

|   | 7.2.2     | Selection of Minimum Number of Outputs that Achieves High Fa   | ıult  |

|   | Coverage  | e 103                                                          |       |

|   | 7.2.3     | Selection of Best Multiplexer and Best Selection Lines         | 103   |

|   | 7.2.4     | Determination of the Final Fault Coverage for the New Design   | 105   |

|   | 7.3 Exp   | erimental Results                                              | 108   |

|   | 7.4 Con   | clusion                                                        | 110   |

| 3 | Conclusi  | ons and Future Work                                            | 111   |

|   | 8.1 Sun   | nmary of Thesis Contribution and Main Conclusions              | 112   |

|   | 8.1.1     | Average Power Minimisation in Test-per-Clock BIST using Low    |       |

|   | Transitio | n LFSR                                                         | 112   |

|   | 8.1.2     | Average Power Minimisation in Test-per-Scan BIST using Low     |       |

|   | Transitio | n LFSR                                                         | 112   |

|   | 8.1.3     | Scan and Capture Peak Power Minimisation in Scan-Based BIST    | using |

|   | BS-LFSI   | R, and 2-Phase Scan-Chain Ordering Algorithm                   | 113   |

|   | 8.1.4     | Increasing Fault Coverage in Scan-Based BIST using a Multi-Out | tput  |

|   | LFSR      | 114                                                            |       |

|   | 8.2 Sug   | gestions for Future Work                                       | 115   |

|   | 8.2.1     | Investigation of LFSRS' Properties                             | 115   |

|   | 8.2.2     | Low Power Delay Test                                           | 115   |

|   | 8.2.3     | System-on-a-Chip (SOC) Test                                    | 115   |

|   | 8.2.4     | Random Access Memory (RAM) Test                                | 116   |

| A | ppendix A |                                                                | 117   |

| D | afarancas |                                                                | 120   |

#### **List of Figures**

| Fig. 1.1      | External testing using ATE                                                         | 2   |

|---------------|------------------------------------------------------------------------------------|-----|

| Fig. 1.2      | External (a) and Internal (b) LFSRs that implement characteristic                  |     |

| polynom       | nial 4                                                                             |     |

| Fig. 1.3      | Test-per-clock configuration.                                                      | 4   |

| Fig. 1.4      | Test-per-scan configuration.                                                       | 5   |

| Fig. 1.5      | (a) Scan D flip-flop (b) Scan-chain connection                                     | 8   |

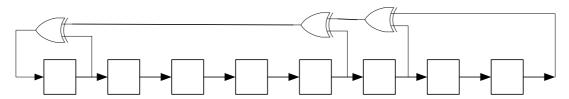

| Fig. 1.6      | Multiple scan-chain design with the LFSR as a two-dimensional TPG                  | 8   |

| Fig. 1.7      | Multiple scan-chains with the presence of phase shifter to remove                  |     |

| correlati     | on                                                                                 | 9   |

| Fig. 1.8      | Dynamic power dissipation in CMOS circuits [17].                                   | .11 |

| Fig 2.1 7     | Taxonomy of the techniques used for low power testing                              | .18 |

| Fig. 2.2      | DS-LFSR proposed in [26]                                                           | .19 |

| Fig. 2.3      | LT-RTPG as proposed in [42]                                                        | .20 |

| Fig. 2.4      | Effect of cell ordering in the number of transitions. (a) Original order and (     | b)  |

| Cells aft     | er reordering                                                                      | .22 |

| Fig. 3.1      | 5-Bit Maximal Length LFSR                                                          | .40 |

|               | General appearance of the proposed BS-LFSR                                         |     |

| Fig. 3.3      | DS-LFSR as Proposed in [26].                                                       | .45 |

| Fig. 4.1      | Swapping arrangement for a LFSR.                                                   | .51 |

| Fig. 4.2      | External LFSR that implements prime polynomial xn+x+1 and the propose              | d   |

| swappin       | g arrangement.                                                                     | .53 |

| Fig. 4.3      | Internal LFSR that implements prime polynomial x <sup>n</sup> +x+1 and the propose | ed  |

| swappin       | g arrangement.                                                                     | .55 |

| Fig. 4.4      | (a) External and (b) Internal LFSRs that implement prime polynomial                |     |

| $x^4 + x + 1$ |                                                                                    | .56 |

| Fig. 4.5      | External LFSR that implements prime polynomial $x^n+x^{n-1}+1$ and the             |     |

| proposed      | d swapping arrangement                                                             | .57 |

| Fig. 4.6      | Internal LFSR that implements prime polynomial $x^n+x^{n-1}+1$ and the proposition | sed |

| swappin       | g arrangement                                                                      | .57 |

| Fig. 4.7 External LFSR that implements prime polynomial $x^n+x^2+1$ and the proposed         |

|----------------------------------------------------------------------------------------------|

| swapping arrangement                                                                         |

| Fig. 4.8 Internal LFSR that implements prime polynomial $x^n + x^{n-2} + 1$ and the proposed |

| swapping arrangement                                                                         |

| Fig. 4.9 External LFSR that implements prime polynomial $x^n + x^{ym} + + x^{y2} + x^{y1} +$ |

| x +1 and the proposed swapping arrangement58                                                 |

| Fig. 4.10 BS-LFSR for test-per-scan BIST59                                                   |

| Fig. 5.1. Conventional scan-based BIST where one cell directly feeds the scan-chain          |

| 66                                                                                           |

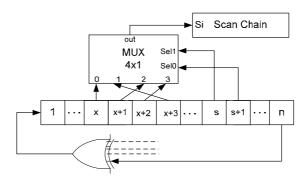

| Fig. 5.2. Smoothing degree $k = 1$ , where 2 cells feed the scan-chain through a             |

| multiplexer66                                                                                |

| Fig. 5.3. Smoothing degree $k = 2$ , where 4 cells feed the scan-chain through a             |

| multiplexer67                                                                                |

| Fig. 5.4 7-bit internal LFSR with $4x1$ multiplexer to get a smoothing degree $k = 2.72$     |

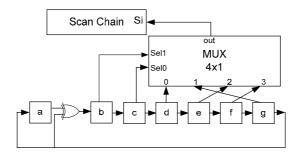

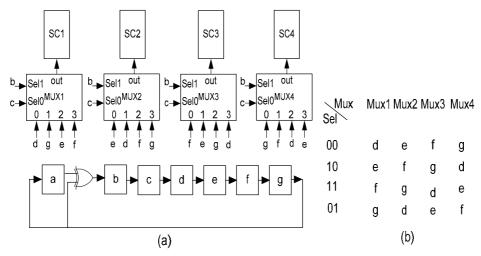

| Fig. 5.5 (a) Extending the smoothing technique for multiple scan-chains, (b) the             |

| rotational property of the proposed design                                                   |

| Fig. 5.6 The Architecture of the RLFSR for test-per-clock BIST75                             |

| Fig. 5.7 The mapping from LFSR to RLFSR is one-to-one                                        |

| Fig. 6.1 Example of phase 1 of the scan-chain ordering algorithm85                           |

| Fig. 6.2 Example of phase 2 of scan-chain ordering algorithm                                 |

| Fig. 6.3 Part of s838 ISCAS'89 benchmark circuit.                                            |

| Fig. 7.1 5-bit LFSR where bit 5 feeds the scan chain                                         |

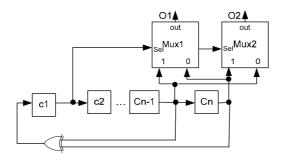

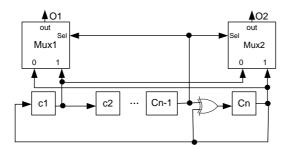

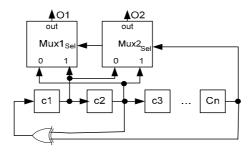

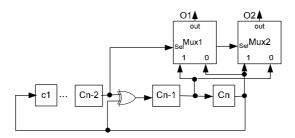

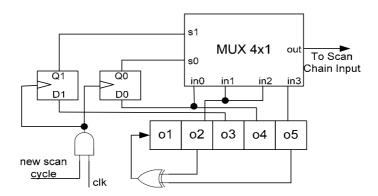

| Fig. 7.2 Suggested design of MO-LFSR                                                         |

#### **List of Tables**

| Table 2.1 Summary of the low power testing techniques with their                                     |

|------------------------------------------------------------------------------------------------------|

| ADVANTAGES AND DISADVANTAGES                                                                         |

| Table 3.1 Exhaustive list of possible transitions for a pair of bits in a                            |

| STANDARD LFSR AND IN THE PROPOSED BS-LFSR                                                            |

| TABLE 3.2 OUTPUT SEQUENCE GENERATED BY A 5-BIT MAXIMAL LENGTH LFSR AND                               |

| THE CORRESPONDING SWAPPED SEQUENCE WHEN BIT $E=0$ 40                                                 |

| TABLE 3.3 RESULTS OF THE EQUIDISTRIBUTION TEST. A VALUE OF V2/V1 OF 1                                |

| INDICATES THAT THE EQUIDISTRIBUTION PROPERTIES OF THE BS-LFSR MATCH THOSE                            |

| OF THE CONVENTIONAL LFSR44                                                                           |

| TABLE 3.4 LENGTH OF TEST VECTOR SEQUENCE REQUIRED IN ORDER ACHIEVING A                               |

| GIVEN LEVEL OF FAULT COVERAGE FOR THE CONVENTIONAL LFSR AND THE PROPOSED                             |

| BS-LFSR45                                                                                            |

| Table 3.5a Evaluation of fault coverage and savings in transitions for the                           |

| BS-LFSR COMPARED TO A CONVENTIONAL LFSR                                                              |

| TABLE 3.6 COMPARISON OF THE SAVINGS IN NUMBER OF TRANSITIONS ACHIEVED BY                             |

| THE PROPOSED $\operatorname{BS-LFSR}$ WITH THOSE IN [26] AND THE COMBINED SAVINGS48                  |

| TABLE 4.1 EXHAUSTIVE ENUMERATION OF POSSIBLE STATES AND SUBSEQUENT                                   |

| STATES FOR BITS M, $M+1$ , AND X (SEE Fig. 4.1).                                                     |

| TABLE 4.2 Possible States and Subsequent States for Cells C1, C2, and Cn                             |

| (SEE Fig. 4.2)53                                                                                     |

| Table 4.3. Possible States and Subsequent States for Cells $C_1,C_{\scriptscriptstyle N},$ and $C_2$ |

| (SEE FIG. 4.3)55                                                                                     |

| Table 4.4. Demonstration of Lemma $4.3A$ and $4.3B$ for External and Internal                        |

| LFSR56                                                                                               |

| TABLE 4.5. LFSRS THAT SATISFY ONE OR MORE OF LEMMAS 3 TO 1060                                        |

| TABLE 4.6. TEST LENGTH NEEDED TO GET TARGET FAULT COVERAGE FOR LFSR AND                              |

| BS-LFSR62                                                                                            |

| TABLE 4.7. EXPERIMENTAL RESULTS OF AVERAGE POWER REDUCTION OBTAINED BY                               |

| USING THE PROPOSED TECHNIQUES. 62                                                                    |

| TABLE 4.8 COMPARISON WITH RESULTS OBTAINED IN [42]                                                   |

| TABLE 5.1. CONNECTIONS BETWEEN LFSR CELLS AND INPUT LINES OF MULTIPLEXER                   |

|--------------------------------------------------------------------------------------------|

| FOR DIFFERENT VALUES OF K                                                                  |

| TABLE 5.2: CORRELATION TEST FOR THE RLFSR WHEN USED IN MULTIPLE SCAN-                      |

| CHAINS BIST74                                                                              |

| Table 5.3. Experimental Results of the Proposed Design for $\kappa=3$ and $\kappa=477$     |

| Table 5.4: Comparison between the Results Obtained by the Proposed Design                  |

| AND RESULTS FOUND IN [42]                                                                  |

| TABLE 6.1. SOURCES OF PEAK POWER IN SCAN-BASED BIST                                        |

| Table 6.2 Truth table for the circuit shown in Fig. 6.3 where the next value $\frac{1}{2}$ |

| OF G11 (I.E. G11+) IS THE OUTPUT90                                                         |

| TABLE 6.3 EXPERIMENTAL RESULTS OF AVERAGE AND PEAK POWER REDUCTION                         |

| OBTAINED BY USING THE PROPOSED TECHNIQUES. 93                                              |

| Table 6.4 Comparison with results obtained in [50]94                                       |

| Table 6.5 Comparison of Peak Power Reductions with results in [73]94                       |

| Table 7.1 Test Patterns that Detect Hard-to-Detect Faults                                  |

| Table 7.2 5-Bit LFSR States                                                                |

| Table 7.3 Test Patterns Fed into Scan Chain using LFSR in Fig. 398                         |

| Table 7.4 First 6 Test Patterns of All LFSR Outputs                                        |

| Table 7.5 L for Different Values of M and N                                                |

| TABLE 7.6: FAULTS DETECTED BY EACH OUTPUT                                                  |

| Table 7.7 Searching for the $2^{\text{ND}}$ best output                                    |

| Table 7.8 Finding the best outputs to detect all the required faults $106$                 |

| TABLE 7.9 OUTPUT D FAULTS AND LFSR INITIAL VALUES                                          |

| Table 7.10 Number of Data lines that will be reserved for output D for                     |

| DIFFERENT COMBINATIONS                                                                     |

| Table 7.11 Initial values of LFSR for outputs F, A, and C $\dots$ 108                      |

| TABLE 7.12 EXPERIMENTAL RESULTS ON ISCAS'89 BENCHMARK CIRCUITS USING                       |

| THE MO-LFSR 109                                                                            |

| Table 7.13 Comparing MO-LFSR Results with Those Obtained By [128]110                       |

#### LIST OF ABBREVIATIONS

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generator

BIST Built-In Self-Test

BS-LFSR Bit-Swapping LFSR

CMOS Complementary Metal Oxide Semiconductor

CUT Circuit-Under-Test

DF Detected Faults

DS-LFSR Dual-Speed LFSR

EFC Effective Fault Coverage

FC Fault Coverage

FF Flip-Flop

IC Integrated Circuit

ISCAS International Symposium of Circuits And Systems

LFSR Linear Feedback Shift Register

LT-RTPG Low Transition Random Test Pattern Generator

MISR Multiple-Input Signature Register

MO-LFSR Multi-Output LFSR

MT-Filling Minimum Transition Filling

MUX Multiplexer

PI Primary Inputs

PO Primary Outputs

PODEM Path Oriented DEcision Making

RAM Random Access Memory

RF Redundant Faults

RLFSR Rotational LFSR

ROM Read Only Memory

RPR Random Pattern Resistant

s-a-0 Stuck-At-0

s-a-1 Stuck-At-1

SA Signature Analyser

SC Scan Chain

SOC System-On-Chip

TF Total Faults

T-FF Toggle FF

TL Test Length

TPG Test Pattern Generator

VLSI Very Large Scale Integration

WSA Weighted Switching Activity

WT Weighted Transition

CHAPTER 1

#### Introduction

In recent years, with the advance of semiconductor manufacturing technology, the requirements of digital very-large-scale-integrated (VLSI) circuits, which are composed of tens to hundreds of millions of gates, have led to many challenges during manufacturing test. Moreover, the unprecedented levels of design complexity and the gigahertz range of operating frequencies make the testing of nanometre system-on-chip (SOC) designs a most demanding challenge. This is because the large and complex chips require a huge amount of test data and dissipate a substantial amount of power during test, which greatly increases the system cost. There are many test parameters that should be improved in order to reduce the test cost. These parameters include the test power, test length (test application time), test fault coverage, and test hardware area overhead.

This thesis addresses the problem of reducing power consumption during off-line test (i.e. when the circuit is switched to test mode and stopped from carrying out its normal operation) and the problem of keeping the test application time moderate without incurring unacceptably low fault coverage. The main objectives of this dissertation are

- 1. To introduce novel techniques that improve the power consumption during test with minimum effect in test length, fault coverage, or hardware area overhead.

- 2. To introduce novel techniques to achieve high fault coverage in the circuit under test (CUT) with an acceptable test length and small hardware area overhead.

3. To combine these new techniques with already existing techniques in order to obtain further reduction in power consumption.

This chapter introduces some important concepts in testing of digital VLSI circuits and the importance of minimising power consumption during test. It then provides the motivation for this study and briefly summarises the organisation and contribution of this dissertation.

#### 1.1 Automatic Test Equipment (ATE)

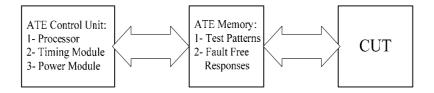

Automatic test equipment (ATE) is instrumentation that is used in external testing to apply test patterns to the CUT, to analyse the responses from the CUT, and to mark the CUT as good or bad according to the analysed responses [1, 2]. Fig. 1.1 shows a basic diagram for external testing using ATE with its three basic components:

- 1. The CUT: this is the integrated circuit (IC) part which is tested for manufacturing defects.

- 2. The ATE control unit: this unit includes the control processor, the timing module, and the power module.

- 3. The ATE memory: this memory contains test patterns that will be supplied to the CUT and the expected fault free responses which are compared with the actual responses obtained from the CUT to determine whether the CUT is faulty or not.

Fig. 1.1 External testing using ATE.

External testing using ATE has a serious disadvantage since the ATE (control unit and memory) is extremely expensive and its cost is expected to grow in the future as the number of chip pins increases [2].

#### 1.2 Built-In Self-Test (BIST)

As the complexity of modern chips increases, external testing with ATE becomes extremely expensive. Instead, built-in self-test (BIST) [3-6] is becoming more common in the testing of digital VLSI circuits since it overcomes the problems of external testing using ATE. BIST test patterns are not generated externally as in case of ATE; instead they are generated internally using some parts of the circuit, also the responses are analysed using other parts of the circuit. When the circuit is in test mode, test patterns generators (TPGs) generate patterns that are applied to the CUT, while the signature analyser (SA) evaluates the CUT responses. One of the most common TPGs for exhaustive, pseudo-exhaustive, and pseudorandom TPG is the linear feedback shift register (LFSR) [4, 7]. LFSRs are used as TPGs for BIST circuits because, with little overhead in hardware area, a normal register can be configured to work as a test generator, and with an appropriate choice of the location of the XOR gates, the LFSR can generate all possible output test vectors (with the exception of the Os-vector, since this will lock the LFSR). The pseudorandom properties of LFSRs lead to high fault coverage when a set of test vectors is applied to the CUT compared with the fault coverage obtained using normal counters as TPGs. Also LFSRs can be configured to act as signature analysers for the responses obtained from the CUT. Despite their simple appearance, LFSRs are based on complex mathematical theory that helps explain their behaviour as TPGs or SAs [4, 7].

The characteristic polynomial of an LFSR determines which flip-flop locations of the LFSR feed the inputs of the XOR gates in the feedback path<sup>1</sup> [4, 8]. If the characteristic polynomial of an LFSR is primitive, then the LFSR will generate the maximum length non-repeating sequence, which is called an m-sequence. LFSRs can be divided into two main categories: external-XOR LFSR (simply external LFSR) and internal-XOR LFSR (simply internal LFSR). These are distinguished by the way in which XOR gates are inserted into the system. In an external LFSR the XORs appear only in the feedback, while in the internal LFSR the XORs appear between flip-flops[4]. As a simple example, the characteristic polynomial  $p(x) = x^3 + x + 1$  is a primitive polynomial of degree 3 (i.e. 3 flip-flops are needed for implementation).

-

<sup>&</sup>lt;sup>1</sup> See appendix A for more details

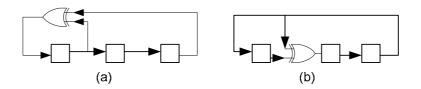

Fig. 1.2(a) shows the external LFSR implementation of this polynomial, while Fig. 1.2(b) shows the internal LFSR implementation.

Fig. 1.2 External (a) and Internal (b) LFSRs that implement characteristic polynomial  $p(x) = x^3 + x + 1 \label{eq:polynomial}$

#### 1.3 Test-per-Clock and Test-per-Scan BIST

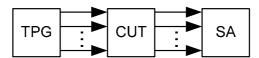

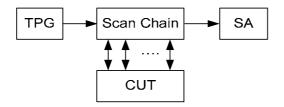

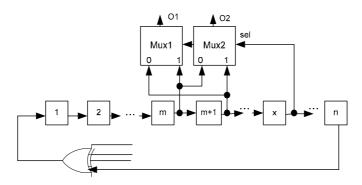

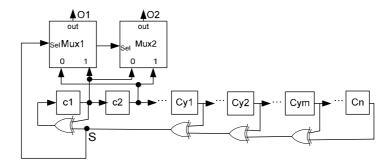

The BIST design methodology has been widely adopted in the design of VLSI circuits in order to enable the chip to test itself and to evaluate its response with an acceptable cost [5, 7]. BIST schemes can be divided into two main types according to the way in which test patterns are applied to the CUT [1, 5]. The first scheme is test-per-clock, in which the outputs of a TPG directly feed the inputs of the CUT, and the outputs of the CUT are directly connected to an SA. In this scheme a test vector is applied to the CUT, and a response is captured from the CUT on each clock cycle. Fig. 1.3 shows a test-per-clock configuration.

Fig. 1.3 Test-per-clock configuration.

The second scheme is test-per-scan, in which a scan path is used to shift test patterns into a CUT. A full scan cycle requires m+1 clock cycles, where m is the number of flip-flops in the scan chain. The response to an applied test pattern is captured into a scan chain and scanned out in the next scan cycle in parallel with scanning in another test pattern. The main advantage of this scheme over the former one is its lower hardware area overhead while the main disadvantage is in the test application time. Fig. 1.4 shows one of many possible configurations for test-per-scan schemes.

Fig. 1.4 Test-per-scan configuration.

#### 1.4 Fault Modelling and Fault Coverage

A fault model can be defined as a description of the behaviour of, and assumptions about, how components (nodes, gates...etc.) in a faulty circuit behave. In this way, a high percentage of the faults that may occur in a circuit can be modelled. One of the most popular and common fault models at the logic level of abstraction is the stuckat-fault model (single and multiple stuck at faults). It makes the assumption that a node under consideration is permanently connected with ground, called stuck-at-0 (s-a-0), or permanently connected with  $V_{dd}$ , called stuck-at-1 (s-a-1). This fault model is considered to be the most common model in logic circuits [9]. This fault model is the target fault model used throughout this thesis due to its popularity.

In addition to the stuck-at fault model, there are other fault models which include stuck-at-open, transition delay, path delay, and bridging fault models [9, 10].

A commonly used metric to represent the percentage of faults detected using a fault model is the fault coverage (FC). The FC can be represented as in equation (1.1)

$$FC = \frac{DF}{TF} \tag{1.1}$$

Where DF represents the number of detected faults, TF represents the total number of faults in the CUT. However, most CUTs contain redundant faults (RF) that are not detectable due to the presence of redundant hardware in the circuit, hence another way to represent the effective fault coverage (EFC) is given by equation (1.2)

$$EFC = \frac{DF}{TF - RF} \tag{1.2}$$

#### 1.5 Fault Simulation

In order to determine the fault coverage for a specified set of test vectors applied to a CUT, fault simulation is carried out. For each fault expected in the CUT (excluding redundant faults), the output produced when a test vector is applied to a faulty circuit differs from the output produced in a fault-free circuit. Thus, fault simulation produces a list of detected faults for each test vector. There are many fault simulators that can be used for this purpose, some commercial and others academic. The fault simulator that is predominantly used within this thesis is an academic tool called FSIM [11] which is based on parallel pattern single fault propagation for stuck-at faults defects.

#### 1.6 Automatic Test Pattern Generator (ATPG)

The automatic test pattern generator (ATPG) is software dedicated to the generation of test vectors that are used to detect the modelled faults in a CUT. Since in many cases the generated vectors do not achieve 100% fault coverage, the ATPG gives statistics about the FC achieved, the percentage of redundant faults, and the aborted faults (which will therefore not be detected) for these test vectors.

ATPG tools can be divided into two types: combinational ATPG and sequential ATPG. The combinational ATPG is dedicated to generating test sets for combinational circuits, or scan-based sequential circuits where all of the state elements can be accessed directly through the scan-chain. This ATPG, if it is well-designed, can generate test vectors that achieve high fault coverage. Most of the combinational ATPGs depends on random and deterministic phases in the generation of test vectors [1, 3]. In the random phase, the ATPG applies pseudo-random vectors to inputs of the CUT and then performs fault simulation to check the fault coverage and the faults remaining undetected. Normally, most of the faults are detected in this phase. In the deterministic phase, the ATPG generates test vectors for specific faults (that are hard to detect by pseudorandom means) and normally uses algorithms such as the path sensitisation method for this purpose.

The sequential ATPG, which is dedicated to the generation of test vectors for sequential circuits, is more complicated as a result of the timing signals and memory elements present in the circuit. In general, two test vectors are needed to test a fault (or group of faults). The first test vector is used to initialise the memory elements to a specified state, and then the next is used to detect the presence of the fault(s). One of the aims of design for testability techniques is to reduce the complexity of test generation for sequential circuits. One common technique to achieve this is to change the sequential circuit to a scan-based circuit.

The aim of this thesis is to reduce the test power in combinational circuits and scanbased sequential circuits where a scan-path is present and memory elements are accessible through this path. Thus, a combinational ATPG was used through this thesis. The ATPG that is mostly used in this thesis is an academic tool called ATALANTA [12] which is used to generate test vectors for stuck-at faults in combinational and scan-based sequential circuits.

#### 1.7 Test Vector Generation in Scan-Based Circuits

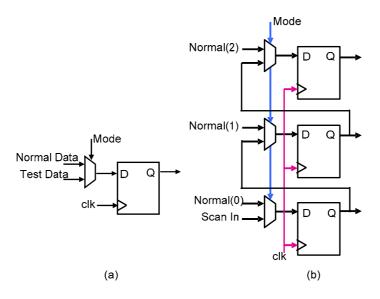

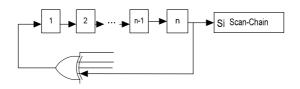

Internal scan design is one of the most efficient design-for-testability techniques to increase controllability and observability in sequential circuits. In scan design, the D flip-flops in the circuit are modified as in Fig. 1.5(a) to act as a scan D flip-flop. A group of scan D flip-flops are connected in such a way that in addition to their normal operation in normal mode, in test mode each flip-flop output is connected with the input of the successive one to form a full scan-chain as shown in Fig. 1.5(b). The first flip-flop input is connected with an external input to feed the scan-chain with patterns, and the last flip-flop output is connected to a signature analyser to check the response. In the multiple scan-chains, the flip-flops are divided into groups; each group forms its own scan-chain.

When the LFSR is used to generate test patterns for full scan-chain sequential circuits, one of its flip-flop outputs is connected with the scan-chain input. In this case the LFSR will be considered as a one-dimensional TPG. The main problem of this configuration is the long time needed to scan-in a test vector which is equivalent to the number of flip-flops in the scan-chain.

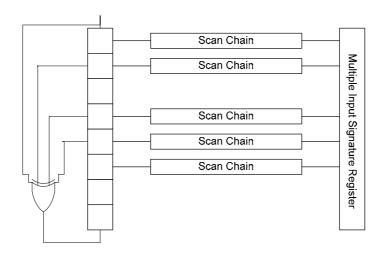

Fig. 1.5 (a) Scan D flip-flop (b) Scan-chain connection

In order to speed-up the scanning of test vectors (i.e. reducing test application time), the flip flops in the circuit can be divided into groups, and each group forms a separate scan-chain. This approach is called multiple scan-chains. In this case a two-dimensional TPG should be used to scan-in test vectors in the multiple scan-chains in parallel. The LFSR can be used for this purpose, where different flip-flops outputs can be connected with the different scan-chain inputs and the outputs of the scan-chains are connected with a multiple input signature register (MISR) as shown in Fig. 1.6 [13].

Fig. 1.6 Multiple scan-chain design with the LFSR as a two-dimensional TPG.

#### 1.8 Phase Shifters

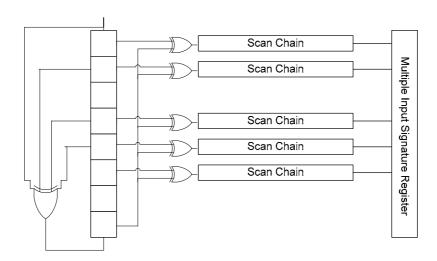

In the case of multiple scan-chains with the LFSR as a two-dimensional TPG as shown in Fig. 1.6, the fault coverage in such an environment is often unsatisfactory due to structural dependencies introduced by the test generator [7, 8]. Furthermore, if the scan-chains are fed directly from adjacent cells of the LFSR, then this will cause the neighbouring scan-chains to contain test patterns which are exactly the same with one clock shift. Thus, the test vectors seen by the CUT will no longer be pseudorandom patterns, which can adversely affect the fault coverage. In order to overcome this problem, while still using a short LFSR to feed many scan-chains in the CUT, extra logic is inserted between the LFSR and the scan inputs of the scan-chains. This logic is called a phase shifter [14].

A typical phase shifter consists of a network of XOR gates as shown in Fig. 1.7. The presence of the XOR gates breaks the structural dependencies and generates test sequences with the desired separation.

Fig. 1.7 Multiple scan-chains with the presence of phase shifter to remove correlation.

#### 1.9 Power Dissipation in Digital VLSI Circuits

With the development of portable devices and wireless communication systems, design for low power has become an important issue. Minimising power dissipation in VLSI circuits increases battery lifetime and the reliability of the circuit [15, 16]. In general, the power dissipation of complementary metal oxide semiconductors

(CMOS) circuits can be divided into two main categories: static power and dynamic power [16].

Static power is the power dissipated by a gate when it is inactive, i.e. when it is not switching. A significant fraction of static power is caused by the reduced threshold voltage used in modern CMOS technology that prevents the gate from completely turning off, thus causing source to drain leakage. All the components of static power dissipation have a minor contribution to the total power dissipation, and can be minimised for well-designed circuits.

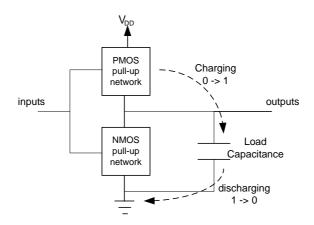

On the other hand, dynamic power dissipation, which is the dominant source of power dissipation in CMOS circuits, occurs while the circuit is switching [15]. The circuit is active when the applied voltage to an input of a cell changes, resulting in a logic transition in one or more of the outputs of the circuit at the transistor level. Hence, charging/discharging of the load capacitances of transistors is the main source of dynamic power dissipation.

The energy that is consumed over a given time T can be expressed as given by equation (1.3) [17]

$$\int_{0}^{T} P(t)dt = \int_{0}^{T} i(t)V_{DD}dt$$

(1.3)

where P(t) is the instantaneous power,  $V_{DD}$  is the supply voltage and i(t) is the current drawn from the voltage source. As the dynamic power is predominantly caused by the current required for charging/discharging the load capacitance through the pull-up and pull down networks as shown in Fig. 1.8, the energy consumed from the source for charging the output from 0 to 1 is given by equation (1.4) [17]

$$E_{0\to 1} = V_{DD} \int_{0}^{T} i(t)dt = V_{DD} \int_{0}^{V_{DD}} C_{i}dV = C_{i}V_{DD}^{2}$$

(1.4)

where C<sub>i</sub> is the load capacitance. Only half of this energy is stored in the capacitor, while the other half is converted into heat [17, 18]. In the same manner, when the

output switches from 1 to 0 the capacitor discharges through the pull down network and the same amount of energy is dissipated as a heat.

Fig. 1.8 Dynamic power dissipation in CMOS circuits [17].

Therefore, the rate at which the outputs change their value determines the average dynamic power dissipation. This is mainly dependant on the circuit activity, which can be particularly problematic during test for reasons that will be explained in section 1.13.

#### 1.10 Terminology Relating to Energy and Power

This section defines some terms related to power consumption measures in low power testing (as defined in [19, 20]). These terms are used throughout this thesis:

- Energy: represents the total switching activity generated during the application of the complete test sequence. The increase of energy consumption during test has a direct effect on the battery lifetime in portable devices.

- Average Power: equals the total energy consumed during test divided by the test time in order to represent the average rate of energy consumption. If the average power is high this will cause a temperature increase in the CUT.

- Instantaneous Power: corresponds to the power consumed at any given instant during testing. This normally happens after applying a rising (or falling) edge of the system clock.

- Peak Power: corresponds to the highest value of instantaneous power measured during testing. The peak power generally determines the thermal and electrical limits of the circuit and the system package requirements.

#### 1.11 WSA and WT Modelling

The energy dissipated at node i per switching event is given by equation (1.5) [19]

$$E_{d} = \frac{1}{2} \times C_{i} \times V_{DD}^{2} \tag{1.5}$$

where  $C_i$  is the load capacitance and  $V_{DD}$  is the supply voltage. Thus, the total energy consumed in a period T is given by equation (1.6) [19]

$$E_{T} = \frac{1}{2} \times C_{i} \times V^{2}_{DD} \times S_{i}$$

(1.6)

where  $S_i$  is the total number of switching events at node i for the period T [19]. Capacitance  $C_i$  is assumed to be proportional to the fan-out  $F_i$  of node i [21]. Thus an estimate of consumed energy  $E_i$  at node i can be given by equation (1.7).

$$E_{i} = \frac{1}{2} \times c_{o} \times F_{i} \times V_{DD}^{2} \times S_{i}$$

(1.7)

where  $c_o$  is the output load capacitance for a fan-out of one. In equation (1.7)  $c_o$  and  $V_{DD}$  are constants for all nodes in the circuit, while  $F_i$  and  $S_i$  vary between nodes. The product "Si×Fi" is named the weighted switching activity (WSA) of node i and is used as a metric for the energy consumption at that node [22]. Finally, the total WSA produced by a CUT after applying all required test vectors is the summation of WSA for each node for each applied test vector. Thus,  $E_{total}$  equals  $\frac{1}{2} \times c_o \times V^2_{DD} \times WSA_{total}$  and the average power equals  $E_{total}/T_{cycles}$ , where  $T_{cycles}$  is the time needed to apply the test vectors.

Alternatively, in scan-based testing, a good way to estimate the power dissipated during scan-in of test vectors or scan-out of captured responses is the weighted transition (WT) metric [23]. The weighted transition metric states that the power consumed in scan-based testing depends not only on the number of transitions in the scanned-in vector (or scanned out response), but also on the positions of the transitions. For example, for a test vector  $V_1 = b_1b_2b_3b_4b_5 = 10000$ , where  $b_5$  is scanned into the scan-chain first, then vector  $V_1$  (which has one transition between  $b_2$  and  $b_1$ ) will cause one transition in a scan-chain of length 5 (assuming that the scan-chain initial value is 00000). By contrast,  $V_2 = 00001$  (which has one transition between  $b_5$  and  $b_4$ ) will cause 4 transitions in the scan-chain. The WT calculation is given by equation (1.8) [23]

$$WT = \sum [(Size \ of \ Scan-Chain) - (Position \ of \ Transition)]$$

(1.8)

It is important to note that the position of a transition in equation (1.8) is counted from right to left in scanned-in vectors, and from left to right in the scanned-out response (e.g. in  $V_1 = b_1b_2b_3b_4b_5 = 10000$ , the transition is in position 4, hence WT = 1. But if the response is R1 =  $b_1b_2b_3b_4b_5 = 10000$ , then the transition is in position 1, hence WT = 4).

#### 1.12 Average and Peak Power

The power consumption in VLSI circuits can be analysed from two different perspectives: average power and peak power. The average power consumption is used to refer to the average power consumed in the circuit during its period of operation or during a large number of clock cycles. The instantaneous power consumption refers to the power consumed in an instant of time after a rising (or falling) edge of clock. The maximum instantaneous power during the whole period of operation is called the peak power.

Excessive average and peak power consumption during test can lead to many serious problems [24, 25]. High average power consumption (which means high power consumption sustained for long period of time) will shorten the battery lifetime in portable devices. Also, the high temperature during test and the heat dissipation produced in CMOS circuits is proportional to the average power consumption [21, 26, 27]; hence a circuit may malfunction if the temperature is too high or it can be permanently damaged as a result of excessive heat dissipation [28, 29]. Furthermore, high average power consumption speeds-up electro-migration and increases the circuit temperature, which can lead to reliability problems [16, 30].

On the other hand, a high value of peak power also cause a high rate of current flowing in the power and ground lines leading to excessive noise in these lines. This noise can erroneously change the logic state of circuit lines leading to incorrect operation of circuit gates causing some good dies to fail the test. Also, high power can lead to a drop in power supply voltage, called voltage drop or IR drop. IR drop reduces noise margins of cells and increases the probability of failure due to crosstalk noise [31].

### 1.13 Motivation for Low Power consumption and High Fault Coverage Testing

In recent years, with the fast growth of personal mobile communication and portable computing systems, design for low power has become one of the greatest challenges in high performance VLSI design. As a consequence, many techniques have been introduced to minimise the power consumption of new VLSI systems. However, most of these methods focus on the power consumption during normal mode operation (functional operation), whilst test mode operation has not normally been a predominant concern. However, it has been found that the power consumed during test mode operation is often much higher than normal mode operation because of the high switching activity in the nodes of the CUT during test [24, 29, 32-34].

The main motivation for considering low power testing is that a circuit consumes much more power during test than during normal mode operation. In [24] it has been shown that the power consumed in test mode can be more than twice the power consumed in normal mode. The main reasons for this increase in test power [19, 20] are as follows:

- Modern ATPG tools tend to generate test patterns with a high toggle rate in order to reduce pattern count which leads to a shorter test application time. Thus, the node switching activity in the CUT in test mode is much higher than normal operation mode.

- In normal operation mode, if the system contains several blocks, then it is likely

that only one or few of the blocks will be active at the same time, hence reducing

the power consumption. By contrast, in test mode parallel testing is often used to

reduce test application time. This parallelism inevitably increases power

dissipation during testing.

- The design for testability circuitry inserted in the circuit will probably be idle

during normal mode but may be used intensively during test mode, hence

increasing the power consumption.

- The correlation between the successive functional input vectors during normal

operation is considered to be high compared with the correlation of test vectors in

the test mode. For example, in the circuits that process digital and video signals,

the inputs to most modules change relatively slowly, hence, successive inputs are

highly correlated. However, for the test vectors generated by a TPG such as LFSR, there is no definite correlation; this will increase the switching activity in the circuit.

As the excessive switching activity causes many problems (as mentioned in section 1.12), low power testing has become a very important issue to be considered in order to avoid reliability problems and manufacturing yield loss due to high power dissipation during test in VLSI circuits.

On the other hand, in order to make the test cost acceptable, the test should run for a short period of time. However, with conventional TPGs, running a test for a short period of time will lead to loss of fault coverage. Furthermore, running the test for a longer time, will not only increase the test cost, but also will increase the total energy consumed during test, hence decreasing the battery lifetime. Thus, it is important to develop techniques that significantly improve the fault coverage within a restricted test length and with an acceptable hardware area overhead.

#### 1.14 Thesis Organisation and Contribution

This thesis presents new techniques for low power testing of combinational and scanbased sequential circuits. Also it presents a new technique to achieve high fault coverage in scan-based sequential circuits with an acceptable test application time.

Chapter 2 of this dissertation summarises the literature on previous work on low power testing and high fault coverage. Also, it summarises – in greater detail than this chapter – the contribution of this thesis.

Chapter 3 introduces a new technique for low power testing of combinational circuits. The technique presented is based on some new observations about the output sequences of a conventional LFSR. It modifies the conventional LFSR by using a simple bit swapping technique. In chapter 4, the technique presented in chapter 3 is extended and applied to scan-based sequential circuits. In chapter 5, the proposed

design is generalised from a two-bit swapping technique to a rotational technique for a group of bits.

A new technique for implementing a cell ordering algorithm is presented in chapter 6. The algorithm aims to reduce both average and peak power in scan-based circuits through a two-phase scan-chain ordering algorithm.

Chapter 7 presents a new technique for attaining high fault coverage in scan based sequential circuits. The proposed technique is based on using more than one cell of the LFSR to feed the same scan-chain.

Finally, the conclusions and suggestions for future work are presented in chapter 8.

The algorithms presented in chapters 3 to 8 have resulted in original work published in [35-38]. In addition to that, another two papers are under preparation for submission.

## CHAPTER 2

#### **Previous Work**

The organization of this chapter is almost similar to a previously published survey about the techniques of low power testing [20]. This chapters approximately uses the same way of categorizing the published techniques but with more references than [20]. Also this chapter concentrates more on the previous techniques fall in the same category as the techniques proposed on this thesis in order to provide comparison with them in the next chapters.

With the development of wireless communication technology and high-performance portable computing devices, design for low power has become a major objective in system design. Power dissipation is not only a critical parameter in the design procedure, but also during manufacturing test and power-on test, as the system may consume much more power during test than during normal (functional) operation [24, 28, 29, 32-34]. Thus, low power test of digital VLSI systems has become a major issue of research in recent years. One direct technique to reduce power consumption during test is testing with a reduced operating frequency [39, 40]. This solution needs no extra hardware. However, although it reduces the average power, it has no effect in reducing the energy since the test time will increase. Also this technique cannot reduce the peak power. Furthermore, timing faults may not be detected using this technique. Another direct technique is by partitioning the CUT into blocks with appropriate test planning [39]. This technique, although it reduces the power consumption, increases test application time because it reduces test concurrency.

This chapter presents a short survey of the techniques used in previous work in the field of low power testing of digital VLSI circuits (section 2.1). Then it briefly describes some techniques that exist in the literature in order to attain high fault coverage with short test application time (section 2.2). Finally, section 2.3 summarises the new techniques presented in this thesis for low power testing and high fault-coverage, and their contributions to the field of digital VLSI testing.

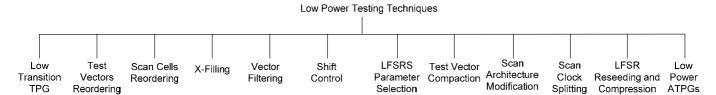

#### 2.1 Previous Work in Low Power Testing

Several techniques have been proposed to reduce power consumption during test. These techniques can be categorised according to their method of application, such as external testing techniques or BIST techniques (test-per-clock techniques and test-per-scan techniques). Also they can be categorised according to their purpose, such as average power reduction techniques, and peak power reduction techniques (scan peak power and capture peak power in scan testing). Finally, they can be categorised according to the general idea and algorithm on which these techniques are based as will be done in the following subsections where many of the fundamental algorithms for low power techniques will be briefly described. Fig. 2.1 shows a taxonomy diagram that summarises the categories of the published low power testing techniques.

Fig 2.1 Taxonomy of the techniques used for low power testing.

#### 2.1.1 Low Transition TPGs

One common technique to reduce test power consumption is the design of low transition TPGs [26, 41-50]. Most of these techniques modify the design of the LFSR (or other forms of TPGs such as cellular automata) in such a way as to reduce the transitions in the primary inputs of the CUT for test-per-clock BIST or inside the scan-chain for scan-based BIST.

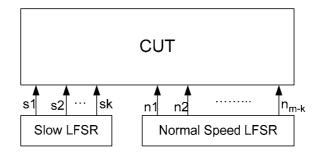

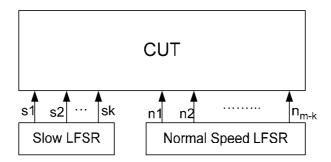

An example of the low transition TPG for test-per-clock schemes is the approach presented in [26]. This approach, called Dual-Speed LFSR (DS-LFSR), is based on the use of two LFSRs working at two different speeds (a normal speed LFSR and a slow LFSR, see Fig. 2.2). The average power can be reduced by connecting the slow LFSR with the CUT inputs that cause high transition densities in the CUT. The remaining, inputs of the CUT are connected to the normal speed LFSR. The main drawbacks of this technique is that it is applicable only for test-per-clock BIST, and it needs a long sequence of test vectors to get an acceptable fault coverage. The approach presented in [46] is mostly similar to one presented in [26] but the power dissipation is reduced not only in the CUT but also in the clock tree feeding the CUT. The method presented in [47] uses weighted random TPG to reduce power consumption while keeping high fault coverage. This is done by inserting extra logic between the LFSR and the CUT.

Fig. 2.2 DS-LFSR proposed in [26]

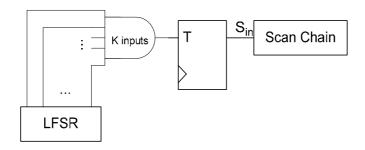

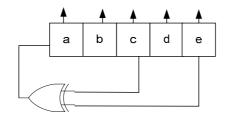

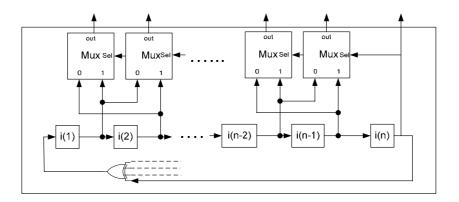

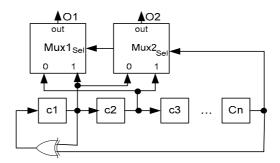

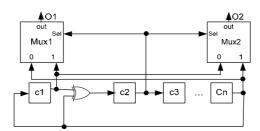

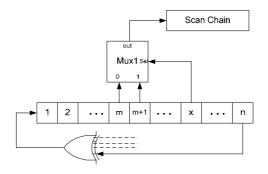

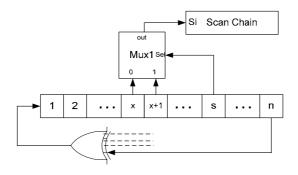

On the other hand, a TPG for low power consumption in scan-based BIST (test-per-scan BIST) is presented in [42]. The proposed design, called low transition random test pattern generator (LT-RTPG), is composed from an LFSR, a k-input AND gate, and a toggle flip-flop T-FF (see Fig 2.3). Some cells of the LFSR are connected with the inputs of the k-input AND gate, the output of the AND gate is connected with the input of the T-FF, and the output of the T-FF is connected with the scan-chain input (S<sub>in</sub>). Since the output of the AND gate (input of the T-FF) is 0 in most of the cases, the T-FF output will not toggle in most of the clock cycles, and hence, neighbouring cells will have the same value in most cases. Thus the transition probability in the CUT will decrease. The main drawback of this system is that it reduces the average power while scanning-in a test vector not while scanning out the captured response. Also, in order to get a high fault-coverage, a long test sequence is needed.

Fig. 2.3 LT-RTPG as proposed in [42]

#### 2.1.2 Test Vectors Reordering

The test vectors reordering techniques aim to reduce the switching activity by modifying the order in which the tester applies the test vectors to the CUT. Normally these techniques can be used in external testing and deterministic BIST. In general, if the number of transitions between two consecutive vectors is reduced (i.e. the Hamming distance between two consecutive vectors is minimum), then the WSA will be reduced in the whole CUT [51]. The techniques presented in [51-57] aim to reorder the test vectors in such a way to reduce the number of transitions between the consecutive vectors before applying them to the CUT's primary inputs.

As a simple example to show how test vector ordering can reduce the number of transitions in the CUT, assume that we have a deterministic test patterns to test a CUT with 4 primary inputs in a test-per-clock scheme. These vectors are V1 = 0000, V2 = 1111, V3 = 0101, and V4 = 1010. If these vectors are applied to the CUT in the order V1, V2, V3, and V4, then they will cause a total number of transitions in the primary inputs of the CUT equal to 10. By contrast, if these vectors are applied in the order V1, V3, V2, and V4 then they will cause a total number of transitions in CUT's primary input equal to 6. Reducing the number of transitions in the primary inputs will reduce the overall switching activity in the CUT. This example is for illustration only, since in real cases more complex and advanced algorithms are proposed to order the test vectors to reach the optimal case of power reduction.

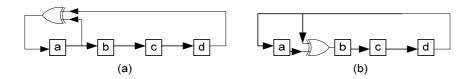

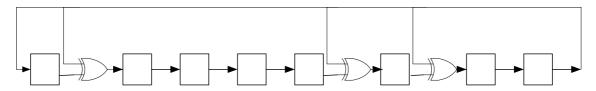

#### 2.1.3 Scan Cells Reordering Techniques

Another category of techniques used to reduce the power consumption in scan-based BIST is the use of scan-chain cells ordering techniques [57-66]. Changing the order of the scan cells in each scan-chain can reduce the switching activity, and hence power dissipation, in scan designs. In the case of a deterministic set of test patterns, the best order of cells is the one that gives the best compromise between reducing the transitions in the scan cells both while scanning in test patterns and while scanning out captured responses. Scan-chain ordering is one of the most popular algorithms to reduce the power consumption in scan-based BIST because it has many advantages. For example, it does not require additional hardware, it has no effect on fault coverage or test application time, and its impact on design flow is low [20]. However, its main drawback is routing congestion problems during scan routing. Also, most of the techniques of scan-chain ordering aim to reduce the average power consumption during scanning in of test vectors and scanning out of captured responses by arranging the scan cells which cause more internal circuit transitions to the positions with low transition weights in the scan chain.

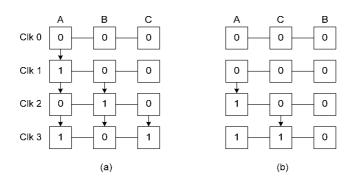

As a simple example to demonstrate how cell ordering algorithms reduce the number of transitions in the scan-chain, assume that there is a scan-chain with 3 flip-flops: A, B, and C with initial values of "000" as shown in Fig. 2.4. Assume that the deterministic test vector 101 is to be scanned into the scan chain (i.e. ABC = 101). Fig. 2.4(a) shows the scan shift with each clock. Since there are 3 flip-flops then 3 clock cycles are needed to scan in the test vector. The arrows in Fig. 2.4 indicate that a transition has occurred in a particular cell in between two adjacent clock cycles. In Fig. 2.4(a) it is clear that scanning in this vector produces 6 transitions in the scanchain. Fig. 2.4(b) shows the scan-chain with the new order ACB (i.e. the test pattern will be ACB = 110), this will reduce the number of transitions in the scan-chain to 2 instead of 6 as shown in Fig. 2.4(b).

Fig. 2.4 Effect of cell ordering in the number of transitions. (a) Original order and (b) Cells after reordering

Although these algorithms mainly aim to reduce average power consumption, they can reduce the peak power that may occur in the CUT during the scanning cycles, but not the capture power that may result during the test cycle (i.e. between launch and capture). However, some of the ordering algorithms aim to order the scan-chain cells in order to minimise the peak power that may arise during the test cycle (capture power) [64]. But these algorithms for reducing capture power are orthogonal with the algorithms that aim to reduce the scan power. None of the techniques in the surveyed literature tried to find a compromise between these algorithms or to merge the two techniques together in order to minimise the overall peak power.

#### 2.1.4 X-Filling Techniques of Test Cubes

Test cubes are test vectors where the values of some bits are left unspecified as X's (don't care bits); for example 1X00X1 is a test cube. In scan-based BIST, a test vector that detects many targeted faults may contain many don't care bits (X). In conventional scan ATPG, each X bit is filled with a 0 or 1 randomly since this will not affect the fault coverage. In fact, the number of X bits in each test cube is typically high [17, 67, 68]. In order to reduce the power consumption while scanning in a test vector, a power-aware X-filling technique is used to properly assign logic values to X-bits in a test cube. The main aim of such techniques is to assign a value to the X bits in the test cube so that the number of the transitions in the scan cells is minimised, hence reducing the transitions in the scan-cells, which leads to a reduction in the overall switching activity in the CUT during shift cycles [69-73]. The non-random X-filling techniques can be divided into 3 approaches in order to reduce shift power:

Minimum transition filling technique (MT-filling), also called adjacent filling, where the most recent non-X bit is used to fill successive X values until a non-X bit is reached.

• 0-Filling. Set 0 to all X-bits.

• 1-Filling. Set 1 to all X-bits.

As a simple example, Consider the test cube [0XX1X0X1XX1X0X]. By applying the above filling techniques the resulting vectors and the number of transitions will be

• MT-Filling: 00011001111100 (4 transitions)

• 0-Filling: 00010001001000 (6 transitions)

• 1-Filling: 01111011111101 (5 transitions)

There are also a few X-filling techniques that aim to reduce the capture peak power by minimising the distance between a test vector and its response [74-78].

### 2.1.5 Vector Filtering Techniques

The test vectors that are generated by TPGs such as LFSRs are pseudorandom vectors. The fault detection capability of these vectors quickly reaches diminishing returns. Hence, after running a sequence of test vectors and detecting many faults, then only a few of the subsequent test vectors can still detect new faults. The vectors that do not detect new faults, but do consume power when applied to the CUT, can be filtered or inhibited from being applied to the CUT [22, 79-81]. These algorithms, in general, use extra logic (e.g. decoder circuitry). Using prior knowledge of the sequences of test vectors generated by TPGs such as the LFSR, they can prevent some sequences from being transmitted to the CUT by knowing the first and last vectors in this sequence. Thus they reduce the power consumption in the CUT.

### 2.1.6 Shift Control Techniques

In scan-based BIST, during scan shifting of test vectors, the combinational part of the CUT will have many transitions although the test vector is not yet applied. There are many techniques that try to eliminate the switching activity in the combinational part of the CUT during scan shifting cycles [28, 82-84]. This can be achieved by identifying a test vector, called input control or shift control, which is applied to the

CUT's primary inputs during scan, thereby minimising or eliminating switching activity in the combinational part of the CUT.

As a simple example, consider the case of a 2-input AND gate in the CUT, with one of its inputs directly accessible through a primary input, and the second input coming from the output of D flip-flop in the scan chain. If the primary input is set to logic 0, then the scanning of a test vector will not affect the output of this gate; the output of the AND gate is an input to other parts of the CUT, and hence, a reduction to the switching activity in the CUT is achieved.

#### 2.1.7 Selection of LFSR Parameters

Some parameters of the LFSR may affect the power consumption of the CUT, namely the seed and the characteristic polynomial of the LFSR. In [85] it is found that the WSA obtained for a given primitive polynomial of the LFSR strongly depends on the seed (the difference in the WSA count between the best and worst seeds is significant). On the other hand, WSA count is almost independent of the primitive polynomial selection for the LFSR [85, 86]. Hence, it is more critical to select the best seed than to select the best characteristic polynomial. Furthermore, since the characteristic polynomial is not critical regarding the power consumption in the CUT, it is recommended in [86] to use the LFSR that needs the minimum number of XOR gates in its feedback since this will reduce area overhead and reduce the power consumption in the LFSR itself.

### **2.1.8** Low Power Test Vector Compaction

In scan-based circuits, in order to reduce the test data volume, compacting techniques are introduced to merge several test cubes. However, compacting test vectors greatly increases the power dissipation (it could be several times higher). Thus, low power test vector compaction techniques have been introduced to minimise the number of test cubes generated by the ATPG tool by merging test cubes that are compatibles in all bit positions under a power constraint [23, 87, 88]. In [23], it has been shown that by carefully merging the test cubes in a specific manner, the number of transitions in the scan-chain can be minimised. Thus, a greedy heuristic procedure was used to

merge test cubes in a way that minimises the number of transitions. Significant reductions in average and peak power consumption can be obtained by using this approach.

As a simple example to demonstrate how compaction can significantly affect the power consumption, assume that there are three test cubes in a system:  $C_1 = 0X0X0X$ ,  $C_2 = X1X1X1$ , and  $C_3 = 0XXX11$ . By using the MT-filling technique described previously in section 2.1.4, the number of transitions in  $C_1$  is 0 (no transitions), in  $C_2$  is 0, and in  $C_3$  is 1. However, using this method, all the test vectors after MT-filling must be applied to the scan-based CUT one by one, which is time-consuming. Instead, merging test cubes together is a good way to reduce test data and test application time. Thus,  $C_1$  can be merged with  $C_2$ ; since they are compatibles in all bit positions, they will produce the test cube  $C_4 = 010101$ . However,  $C_4$  cannot be merged with  $C_3$  since they are not compatible.

Now only two test vectors need to be applied to the CUT:  $C_3$  and  $C_4$ . This is good from the point of view of test application time. However,  $C_4$  has 5 transitions which significantly increases the average and peak power in the CUT, so this merging of  $C_1$  and  $C_2$  is risky from the point of view of power reduction, and is not recommended. On the other hand, from the original test cubes:  $C_1$ ,  $C_2$ , and  $C_3$ , the test cubes  $C_2$  and  $C_3$  are compatible with each other (they have no conflict in any bit position). Thus they can be merged together to produce test cube  $C_5 = 01X111$ . However  $C_5$  cannot be merged with  $C_1$  since they are not compatible. So, we still have 2 test cubes ( $C_1$  and  $C_5$ );  $C_5$  has one transition which is good regarding power consumption compared with the previous scenario of compaction.

#### 2.1.9 Scan Architecture Modification

This technique involves modifying the scan architecture by inserting new elements and partitioning the scan-chain into segments. In [89] the scan-chain is partitioned into N segments where only one segment is active at a time. This technique reduces the average power consumption in the CUT, but it will not affect the power consumption in the clock tree feeding the circuit. This problem has been addressed in [40], where separate clock trees are used for each scan segment. The scan segments

will be enabled by using the gated clock trees instead of scan enable signals as was used in the previous technique.

A similar approach can be used to reduce both peak and average power consumption as described in [90] where mutually exclusive scan segment activation signals are used in the scan architecture to get high reductions in peak power consumption. Other techniques based on scan architecture modifications are described in [91-96].

### 2.1.10 Scan Clock Splitting

This technique modifies the scan clock in order to reduce the power consumption during scan testing [97-99]. In [97] a technique based on scan clock splitting is presented. It involves reducing the operating frequency of the scan cells during scan shifting without modifying the total test time. In this technique, two clocks have been used; each of them is at half the frequency of the system clock, and is used to activate half of the scan cells in the scan-chain. The use of such a system reduces the average and peak power consumption without increasing test time. Another technique that uses a staggered clock scheme to reduce the peak power consumption during scan testing is presented in [98].

### 2.1.11 LFSR Reseeding and Test Data Compression Techniques

Considering together the problems of test data compression and low power test is very important. A long sequence of test vectors needs more time to be applied to the CUT, which also means high energy consumption since the total energy is a function of time. Hence, compression of test data leads to reduction to the total energy. Furthermore, using clever techniques for the compression will also reduce the average and peak power consumption.

The low power test data compression techniques can be divided into three main categories [100]: coding-based techniques, linear-decompression-based techniques (LFSR reseeding techniques) and broadcast-scan-based techniques.

Examples of coding-based techniques of low power test data compression can be found in [101-105]. In [101], the test cubes generated by ATPG are encoded using Golomb codes which are developed from run-length codes. All don't care (X) bits are mapped to 0 and the Golomb code is used to encode runs of 0s. This technique is efficient to compress the runs of 0s but inefficient to encode the runs of 1s and the test storage may increase if there are many runs of 1s in the test cubes. The technique presented in [102] based on alternating run-length coding overcomes this problem.

On the other hand, LFSR reseeding techniques for test data compression are considered to be an efficient approach to compression since only 1% to 5% of the bits in a test vector are considered to be specified (all remaining bits are don't care). The basic idea of LFSR reseeding is to generate deterministic test cubes by expanding seeds. A seed is an initial state of the LFSR that is expanded to a test vector by running the LFSR. Given a deterministic test cube and characteristic polynomial of the LFSR, the seed can be computed by solving a set of linear equations. The main advantage of this is that the seed is normally much shorter than the test cube [106].

In [107] a method that uses dual LFSR reseeding technique is used to reduce total power by masking some bits in the test vector by using AND and OR gates, thus reducing the transition probability. However, the method needs a hardware area overhead and increases test storage since there are two LFSRs used in the technique. In [108] the authors present a scheme that uses a LFSR reseeding technique to reduce the number of transitions in the scan-chain with an acceptable area overhead and good test power reduction.

Finally, the broadcast-scan-based-schemes of low power test data compression are based on broadcasting the same value to multiple scan chains when the scan chain is split into multiple segments, thus allowing the same data to be loaded into all compatible segments [109, 110].

### 2.1.12 Low Power ATPG Algorithms

Many new ATPGs have been proposed in order to reduce the power consumption while still achieving the main objectives of classical ATPGs such as fault coverage

and test length [111-114]. For example, in [111] the authors propose a new version of the path oriented decision making (PODEM) algorithm where the clever assignment of don't care bits minimises the number of transitions at the CUT's primary input. This algorithm is extended to scan-based circuits in [114]. The algorithm described in [113] is dedicated to reducing the capture power during scan testing by generating test cubes that will reduce the power in the capture cycle.

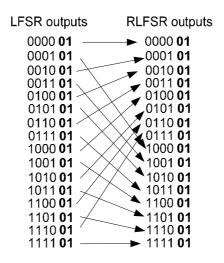

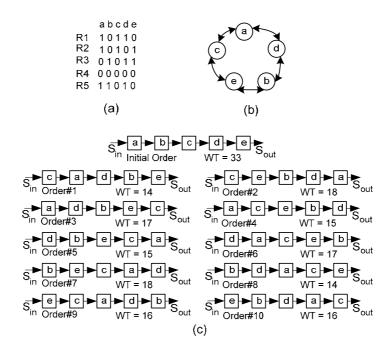

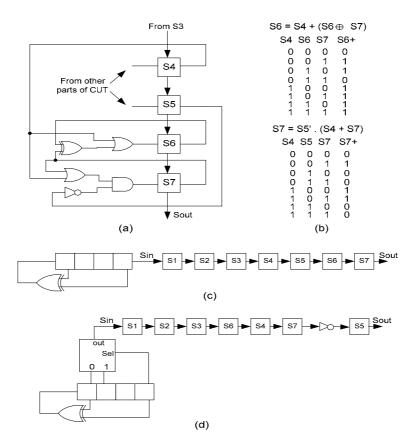

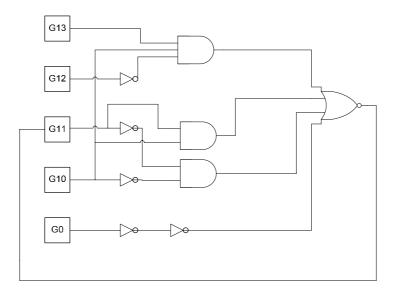

### 2.1.13 Summary of Previous Low Power Testing Techniques