# Modular Multilevel Converter with Full-bridge Submodules for Flexible Medium Voltage DC Electric Railway Systems

by

Sina Sharifi

# A thesis submitted to the University of Birmingham for the degree of DOCTOR OF PHILOSOPHY

Department of Electronic, Electrical and Systems Engineering School of Engineering University of Birmingham December 2022

### UNIVERSITY<sup>OF</sup> BIRMINGHAM

#### **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

#### **Abstract**

The idea of using DC railway electrification systems operating at medium voltage levels has been proposed in the literature. The Medium-voltage DC (MVDC) railway electrification systems are suitable options for the mainline and high-speed electric railways and have a wide range of advantages over the traditional AC and DC electrification systems. The benefits include but are not limited to less voltage drop, less impact on the public AC networks and possibility of connection to the low-voltage AC distribution networks, simple power supply diagram, and possibility of forming DC microgrids with the MVDC railway feeder as the main part.

Despite the advantages and due to practical challenges, MVDC railways have not been implemented in the railway industry. In particular, designing AC-DC power converters for the MVDC TPSs is one of the challenges towards developing the MVDC railways. In this research, a 25 kV DC railway electrification system for the high-speed lines has been proposed. For the MVDC TPSs, a modular multilevel converter with full bridge submodules (MMC-FB) has been designed and a suitable control and modulation scheme for the MMC-FB has been developed. In the next step, the performance of the

Finally, the technical feasibility of the proposed control and modulation scheme has been investigated using a small-scale lab demonstrator of an MVDC TPS. Similar to the simulation results, the experimental results show the appropriateness of the MMC-FBs for the MVDC TPSs.

proposed MMC-FB and its controller has been evaluated by the MVDC railway

simulation models in various operating scenarios.

## Acknowledgements

First, I would like to thank my parents and brothers for all their love, understanding and patience. Special thanks to Dr Soroosh Sharifi, Dr Narges Mahpeykar and Dr Delaram Sharifi for their great support from the beginning of my PhD studies and specifically during the dark days of the COVID-19 lockdowns.

My sincere thanks go to Dr Pietro Tricoli and Professor Clive Roberts for supervising my PhD project and their valuable helps, and Dr Stuart Hillmansen for assessing the annual progress reports.

I would also like to thank the friendly people at Birmingham Centre for Railway Research and Education (BCRRE), particularly Dr Tamer Kamel, Dr Tabish Mir, Dr Edward Stewart, Dr Paul Weston, Dr Mani Entezami and Mr Adnan Zentani. I would like to also thank Dr Ivan Krastev for his helps with the lab prototype.

This project has received funding from the Shift2Rail Joint Undertaking (JU) under grant agreement No 826238. The JU receives support from the European Union's Horizon 2020 research and innovation programme and the Shift2Rail JU members other than the Union.

# **Table of Contents**

| 1   | INTRO               | ODUCTION                                                        | 1  |

|-----|---------------------|-----------------------------------------------------------------|----|

| 1.1 | Research objectives |                                                                 |    |

| 1.2 | Publications        |                                                                 |    |

| 1.3 | Thes                | sis outline                                                     | 5  |

| 2   | LITE                | RATURE REVIEW                                                   | 7  |

| 2.1 | Con                 | ventional railway electrification systems                       | 7  |

|     | 2.1.1               | Low-voltage DC systems                                          |    |

|     | 2.1.2               | Single-phase AC systems with low frequency                      | 9  |

|     | 2.1.3               | Single-phase AC systems operating at mains frequency            | 11 |

|     | 2.1.4               | Three-phase AC systems with low frequency                       | 15 |

| 2.2 | Prop                | osed feeding arrangements for MVDC railways                     | 16 |

| 2.3 | Con                 | verter topologies suitable for the MVDC TPSs                    | 19 |

| 3   | MODI                | ELLING THE PROPOSED MVDC ELECTRIC RAILWAY                       |    |

| SY  | STEM A              | AND MODULAR MULTILEVEL CONVERTER                                | 20 |

| 3.1 | Spec                | rifications of the proposed MVDC railway electrification system | 20 |

| 3.2 | Mod                 | el of the MVDC railway                                          | 23 |

| 3.3 | MM                  | C-FB model                                                      | 25 |

|     | 3.3.1               | Power circuit                                                   | 25 |

|     | 3.3.2               | Control scheme                                                  | 28 |

|     | 3.3.3               | Modulation and sorting scheme                                   | 30 |

|     | 3.3.4               | DC short-circuit current controller                             | 37 |

| 3.4 | MM                  | C loss modelling                                                | 39 |

| 3.5 | Sum                 | mary                                                            | 40 |

| 4   | SIMU                | LATION ANALYSIS OF MVDC RAILWAYS                                | 42 |

| 4.1 | Case                | e 1: An individual MVDC TPS in normal operation                 | 42 |

| 4.2 | Case                | 2: An individual MVDC TPS during regenerative braking           | 52 |

| 4.3 | Case                | e 3: An individual MVDC TPS during a voltage dip on the AC side | 54 |

| 4.4 | Case                | 4: An individual MVDC TPS during DC short-circuit               | 56 |

| 4.5 | Case                | 5: Double end-fed MVDC railways                                 | 60 |

|     | 4.5.1               | Case 5-1: Integration of renewable power sources                | 60 |

|     | 4.5.2               | Case 5-2: Higher penetration of renewable sources               | 65 |

|     | 4.5.3               | Case 5-3: Power sharing between the TPSs                        | 66 |

| 4.6 | Case                | e 6: MVDC railways with multiple TPSs                           | 71 |

| 4.7         | Case                                | 7: Loss analysis of MMC-FB in an individual MVDC TPS                                                                                 | 73  |

|-------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.8         | Summary                             |                                                                                                                                      | 75  |

| 5           | EXPERIMENTAL SETUP OF AN MVDC TPS76 |                                                                                                                                      | 76  |

| 5.1         | Hardy                               | ware design                                                                                                                          | 77  |

|             | 5.1.1                               | Overall arrangement                                                                                                                  |     |

|             | 5.1.2                               | Power circuit and control circuitries of the MMC-FB                                                                                  | 78  |

|             | 5.1.3                               | MMC-FB control unit                                                                                                                  | 82  |

| 5.2         | Softw                               | vare design                                                                                                                          | 82  |

|             | 5.2.1                               | FPGA program                                                                                                                         | 82  |

|             | 5.2.2                               | RT target program                                                                                                                    | 88  |

| 5.3         | MMC                                 | C-FB operation                                                                                                                       | 90  |

| 5.4         | Sumn                                | nary                                                                                                                                 | 92  |

| 6           |                                     | IMENTAL RESULTS                                                                                                                      |     |

| 6.1         | Perfo                               | rmance analysis in constant DC load                                                                                                  | 93  |

|             | 6.1.1                               | No-load condition (IDC = 0)                                                                                                          | 93  |

|             | 6.1.2                               | Half-load condition ( <i>IDC</i> = 0.5 A)                                                                                            | 95  |

|             | 6.1.3                               | Full-load condition ( <i>IDC</i> = 1 A)                                                                                              | 102 |

| 6.2         | Perfo                               | rmance analysis for DC load change                                                                                                   | 104 |

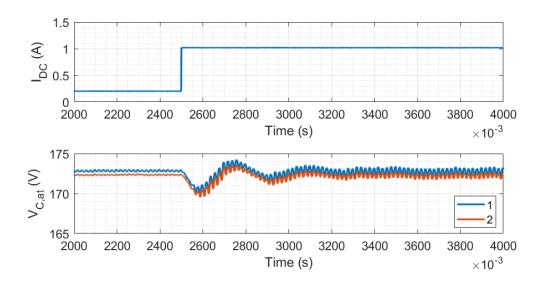

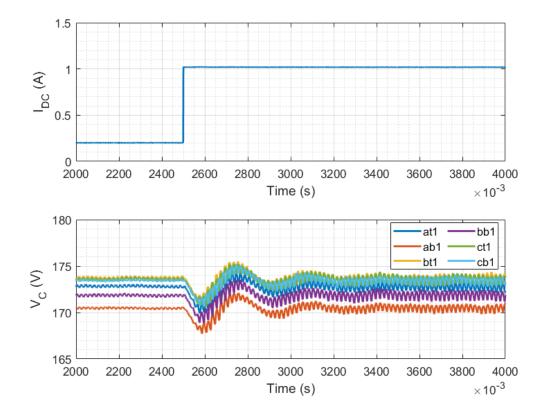

|             | 6.2.1                               | Low-load to full-load condition                                                                                                      |     |

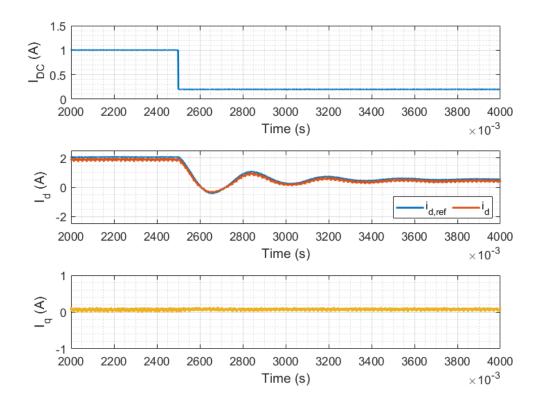

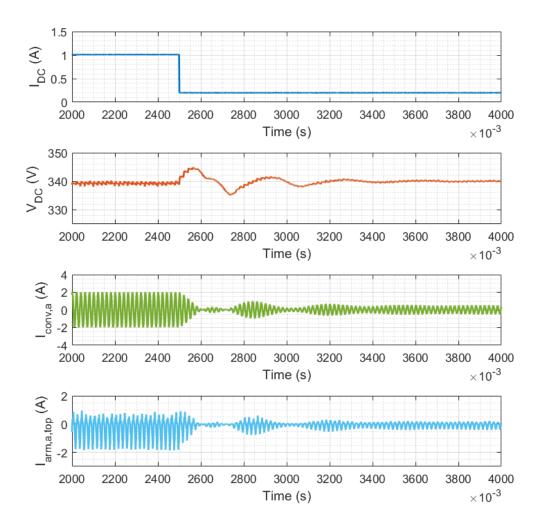

|             | 6.2.2                               | Full-load to low-load condition                                                                                                      | 108 |

| 6.3         | DC-si                               | ide short-circuit test                                                                                                               | 111 |

| 6.4         | Sumn                                | nary                                                                                                                                 | 115 |

| 7           | CONCLUSION AND FUTURE WORK116       |                                                                                                                                      | 116 |

| 7.1         | Concl                               | lusion                                                                                                                               | 116 |

| 7.2         | Future                              | e work                                                                                                                               | 120 |

|             | 7.2.1                               | Research areas                                                                                                                       | 120 |

|             | 7.2.2                               | Industrial implementation                                                                                                            | 121 |

| 8           | APPEN                               | DICES                                                                                                                                | 123 |

| 8.1<br>feed |                                     | ndix A: The paper "Medium-voltage DC electric railway systems: A review gements and power converter topologies"                      |     |

| 8.2<br>Proj | • •                                 | ndix B: The overall schematic of the proposed control system and the Integral (PI) controller gains used in the MVDC TPS simulations | 157 |

| 8.3         | Appe                                | ndix C: Derivation of Equations 3-5 and 3-6                                                                                          | 159 |

| 8.4<br>sim  | • •                                 | ndix D: PI Controller gains used for the short-circuit current controller in the                                                     |     |

| 8.5         |                                     | ndix E: PI Controller gains used for the controllers in the experimental setu                                                        |     |

| 9           | Referen                             | ices                                                                                                                                 | 163 |

# **List of Figures**

| Figure 1.1 - MVDC railways as a part of a microgrid                                  |

|--------------------------------------------------------------------------------------|

| Figure 2.1 - Commonly used railway electrification systems                           |

| Figure 2.2 - low-frequency AC railways - Distributed form [4]11                      |

| Figure 2.3 - A typical 25 kV, 50 (60) Hz supply system [15]                          |

| Figure 2.4 - Various configurations for 25 kV, 50 (60) Hz railways [15]: a) Direct   |

| connection via a transformer b) Direct connection via a transformer and a return     |

| conductor                                                                            |

| Figure 2.5 - 25 kV, 50 (60) Hz railways with (a) Booster transformer (b) Booster     |

| transformer and a return conductor [15]                                              |

| Figure 2.6 - Implementation of autotransformers in 25 kV, 50 (60) Hz railways [15]14 |

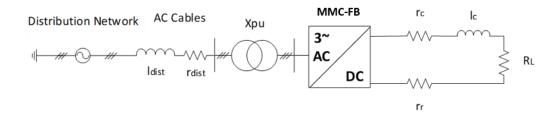

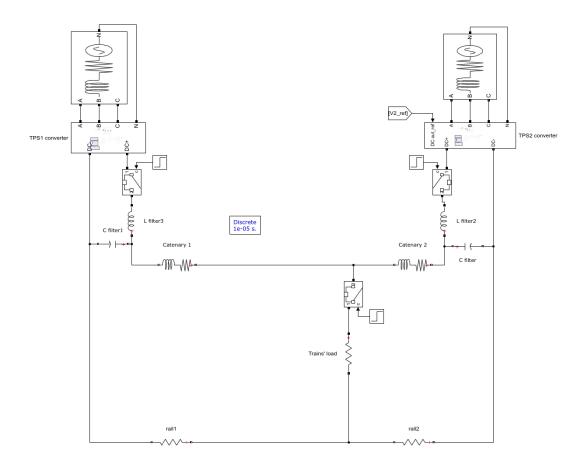

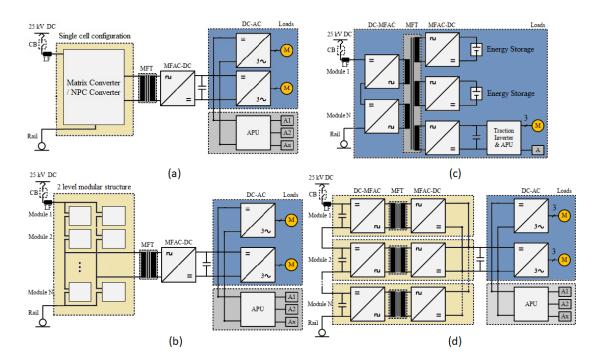

| Figure 3.1 - The proposed MVDC railway electrification system21                      |

| Figure 3.2 - The MVDC TPS model                                                      |

| Figure 3.3 - Power circuit of the MMC-FB                                             |

| Figure 3.4 - The MVDC TPS modelled in Matlab/Simulink                                |

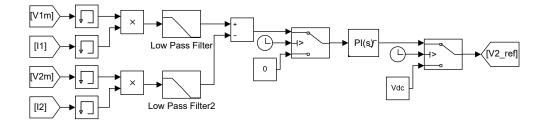

| Figure 3.5 - The proposed controller for the MMC-FB                                  |

| Figure 3.6 - Block diagram of the modulation and sorting scheme used for the MMC-    |

| FB31                                                                                 |

| Figure 3.7 - The DC index generator block                                            |

| Figure 3.8 - The AC index generator block                                            |

| Figure 3.9 - Logic implemented in the sorting blocks                               | .35 |

|------------------------------------------------------------------------------------|-----|

| Figure 3.10 - The logic of gate signal generator blocks                            | .36 |

| Figure 3.11 - DC short-circuit current controller                                  | .37 |

| Figure 3.12 - DC fault modelling in the Matlab/Simulink simulations                | .38 |

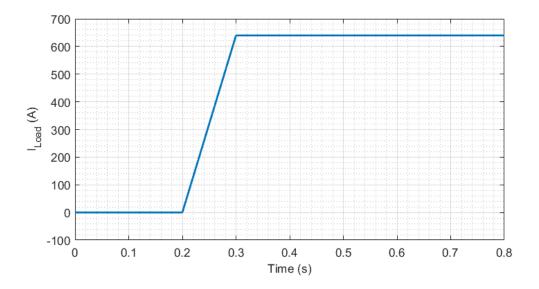

| Figure 4.1 - DC load current profile - case 1                                      | .43 |

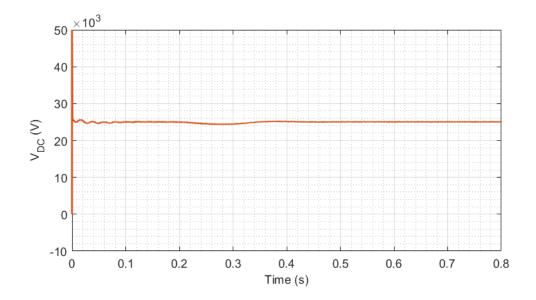

| Figure 4.2 - DC-side voltage - case 1                                              | .44 |

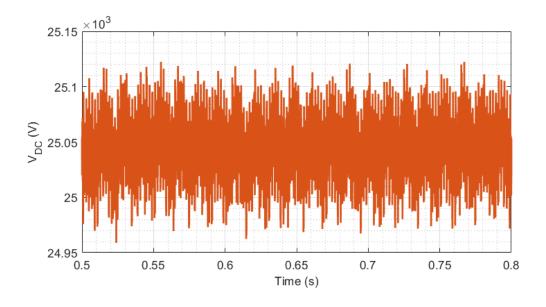

| Figure 4.3 - DC-side voltage between $t = 0.5$ s and $t = 0.8$ s - case 1          | .44 |

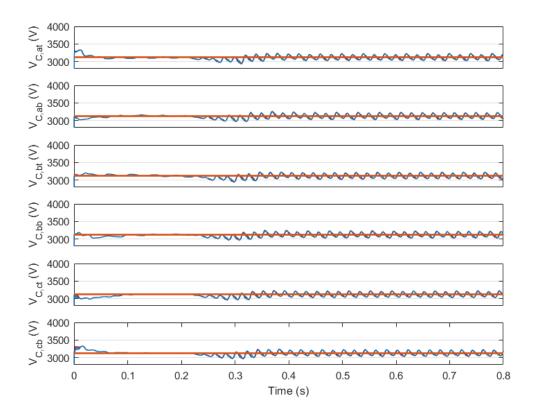

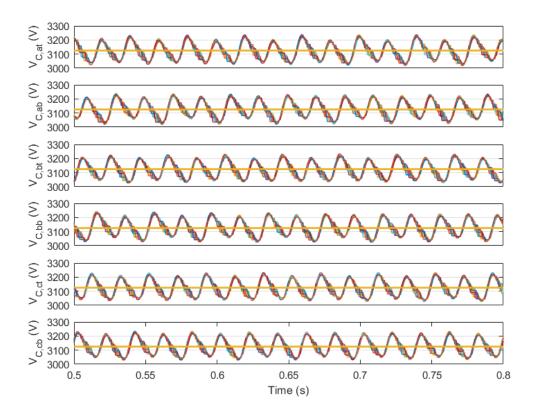

| Figure 4.4 - MMC-FB capacitor voltages - case 1                                    | .45 |

| Figure 4.5 - Magnified capacitor voltages - case 1                                 | .46 |

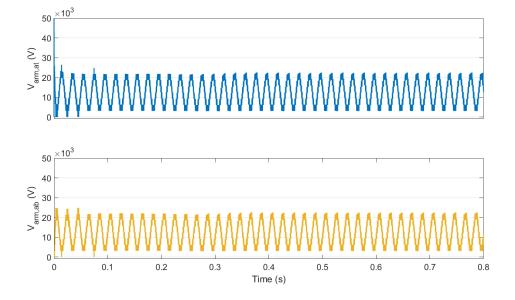

| Figure 4.6 - Arm voltages in phase 'a' of MMC-FB - case 1                          | .47 |

| Figure 4.7 - Voltage drops on the arm inductors of phase 'a' - case 1              | .47 |

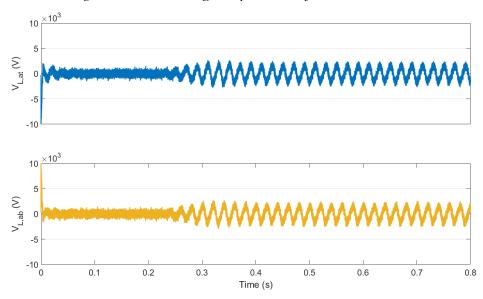

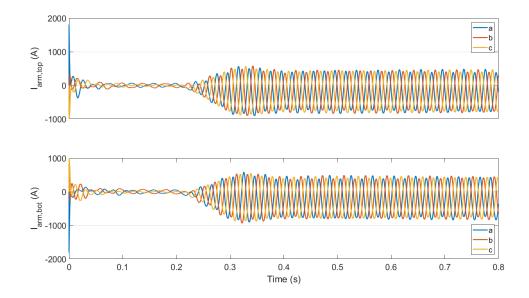

| Figure 4.8 - Arm currents in the MMC-FB - case 1                                   | .48 |

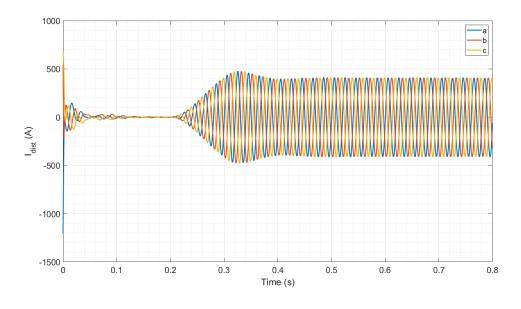

| Figure 4.9 - AC currents in 33 kV distribution network - case 1                    | .48 |

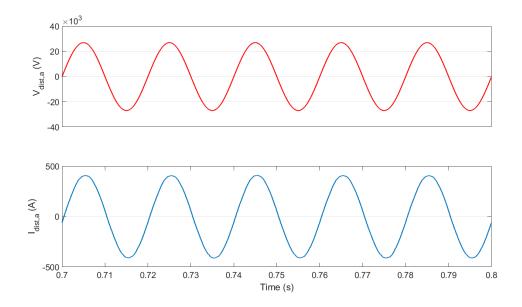

| Figure 4.10 - Voltage and current of phase 'a' in 33 kV distribution network - cas | e 1 |

|                                                                                    | .49 |

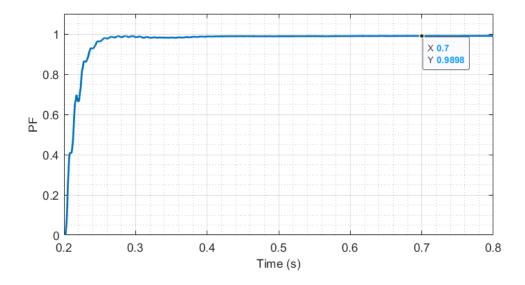

| Figure 4.11 - Power factor in 33 kV distribution network (full load) - case 1      | .50 |

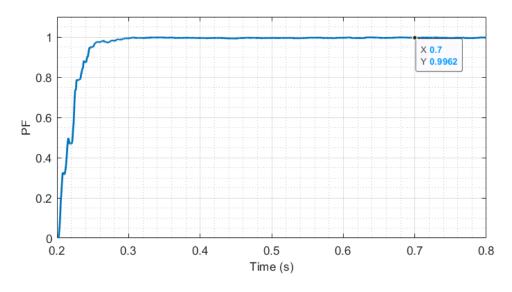

| Figure 4.12 - Power factor in 33 kV distribution network (low load) - case 1       | .50 |

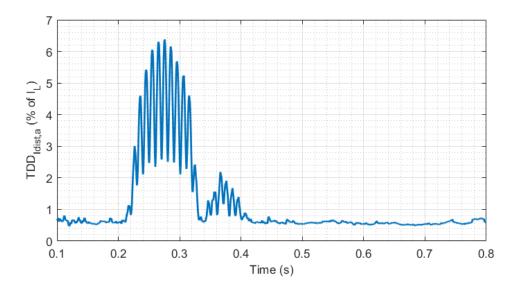

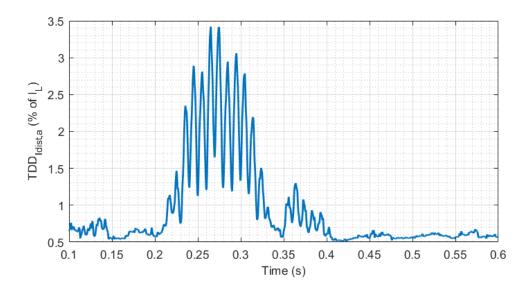

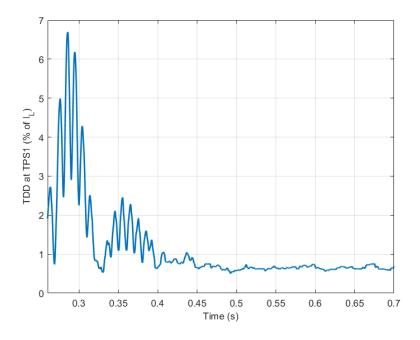

| Figure 4.13 - TDD of phase current 'a' in 33 kV network - case 1                   | .52 |

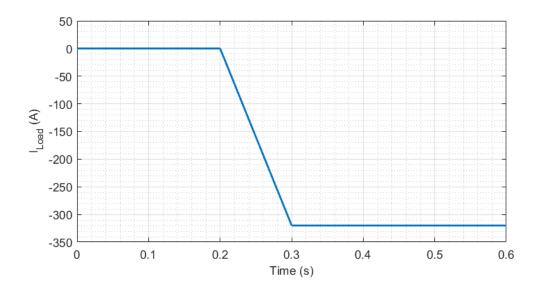

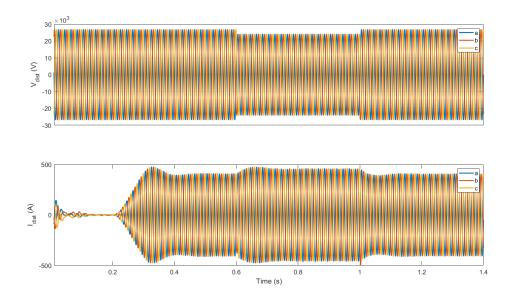

| Figure 4.14 - Load profile - case 2                                                | .53 |

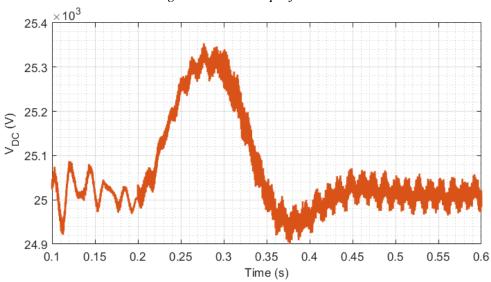

| Figure 4.15 - DC-side voltage - case 2                                             | .53 |

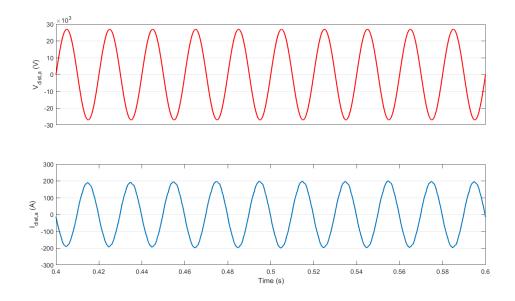

| Figure 4.16 - Voltage and current of phase 'a' in 33 kV distribution network - case 2  |

|----------------------------------------------------------------------------------------|

| 54                                                                                     |

| Figure 4.17 - TDD of phase current 'a' - case 2                                        |

| Figure 4.18 - Voltages and currents of 33 kV network - case 3                          |

| Figure 4.19 - Capacitor voltages in phase 'a' of the MMC-FB - case 356                 |

| Figure 4.20 - DC-side voltage - case 3                                                 |

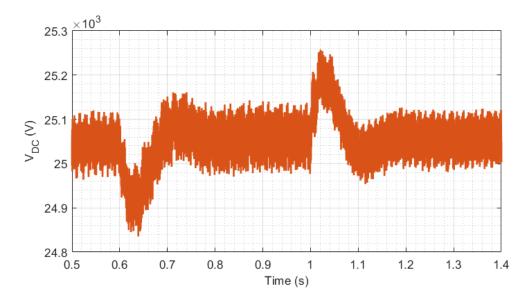

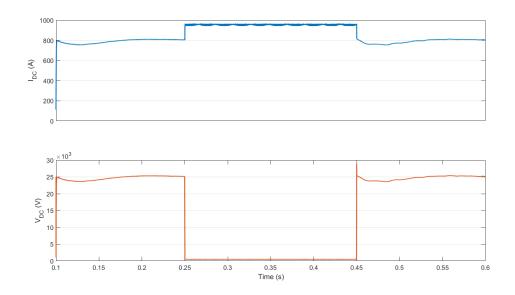

| Figure 4.21 - DC-side current and voltage - case 4                                     |

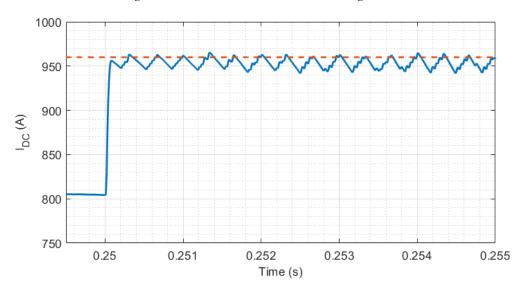

| Figure 4.22 - DC current (magnified) - case 4                                          |

| Figure 4.23 - Arm voltages of phase 'a' in the MMC-FB - case 459                       |

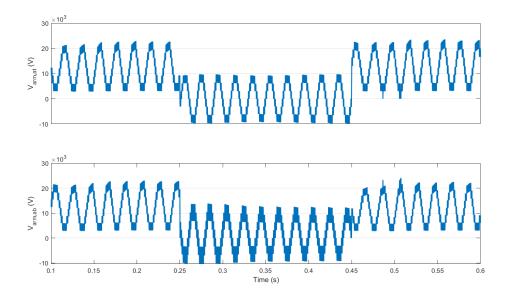

| Figure 4.24 - Voltages and currents of 33 kV network - case 4                          |

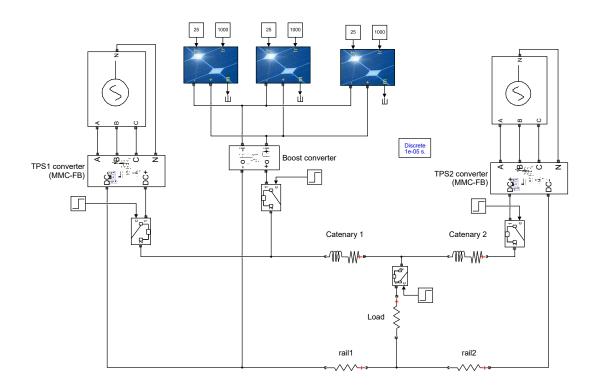

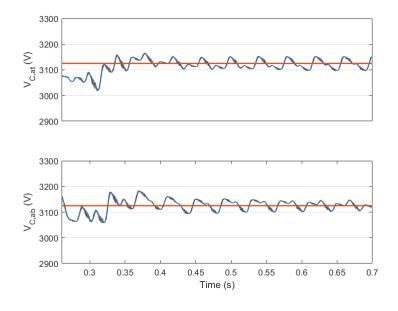

| Figure 4.25 - MVDC railway network in double-end feeding arrangement and in the        |

| presence of a PV farm - case 5-1                                                       |

| Figure 4.26 - Simulated boost converter - case 5-1                                     |

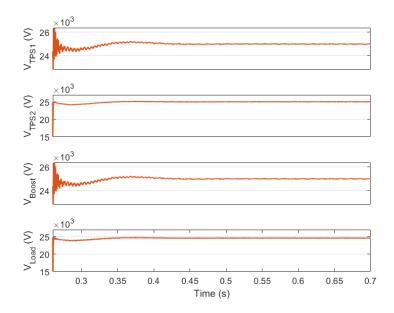

| Figure 4.27 - DC-side voltage at TPS 1, TPS 2, boost converter and load voltage - case |

| 5-1                                                                                    |

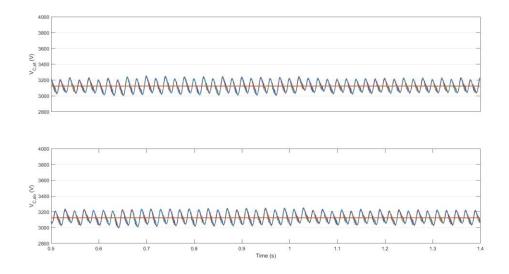

| Figure 4.28 - Capacitor voltages of phase 'a' of the MMC-FB in TPS 1 - case 5-1 63     |

| Figure 4.29 - TDD at TPS 1 (33 kV network side) - case 5-164                           |

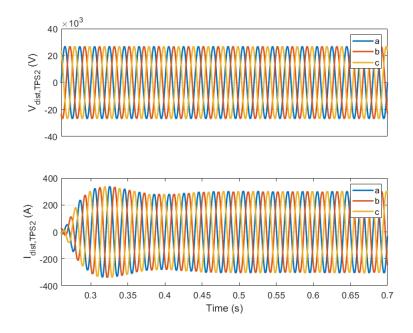

| Figure 4.30 - Voltages and currents at TPS 2 (33 kV network side) - case 5-164         |

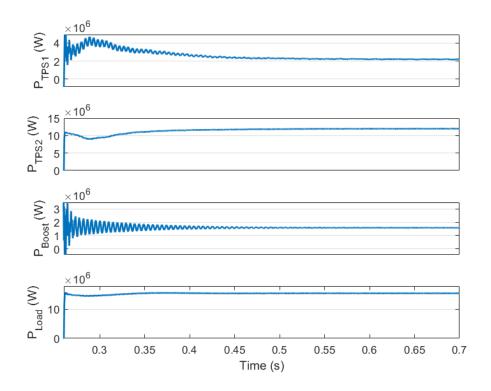

| Figure 4.31 - Power of the TPSs, boost converter (PV farm) and load - case 5-165       |

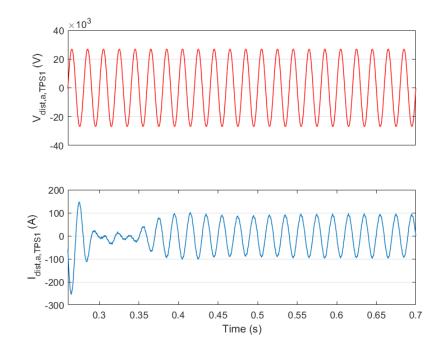

| Figure 4.32 - Voltage and current of phase 'a' at TPS 1 (33 kV network side) - case 5- |

| 2                                                                                      |

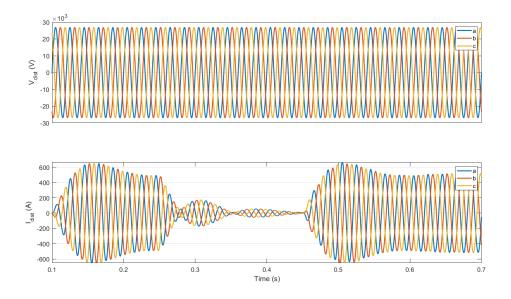

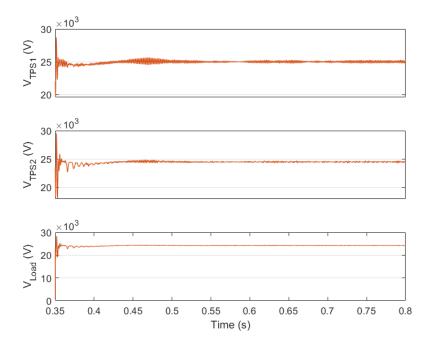

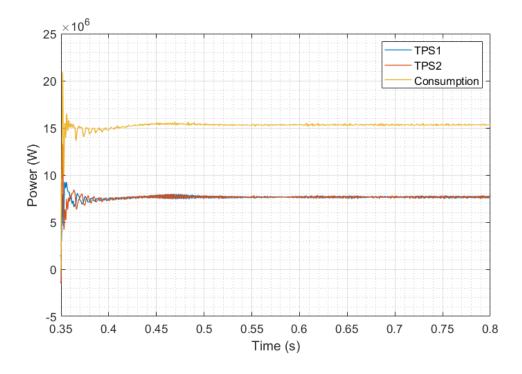

| Figure 4.33 - MVDC railway network - case 5-3                                   | 67         |

|---------------------------------------------------------------------------------|------------|

| Figure 4.34 - Central controller of the MVDC network - case 5-3                 | 68         |

| Figure 4.35 - DC voltage at TPS 1, TPS 2 and across the load - case 5-3         | 69         |

| Figure 4.36 - Power of TPS 1 and TPS 2 (DC side), and power consumed by         | the load   |

| and MVDC railway network - case 5-3                                             | 70         |

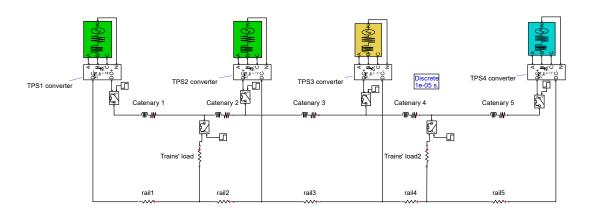

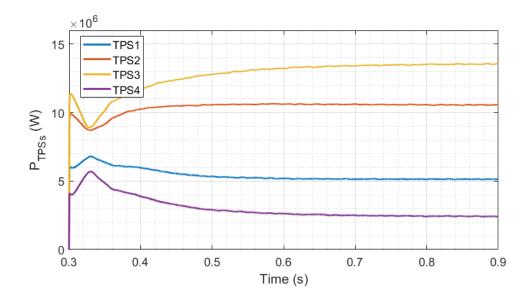

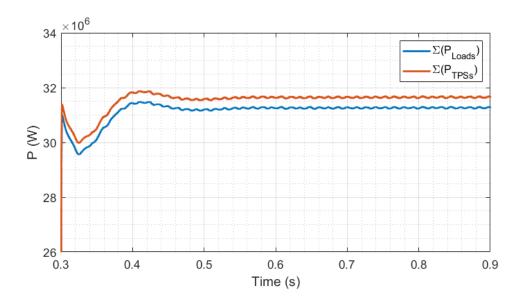

| Figure 4.37 - MVDC railways with multiple TPSs - case 6                         | 71         |

| Figure 4.38 - Power of TPSs on the DC side - case 6                             | 72         |

| Figure 4.39 - Sum of the power provided by the TPSs and consumed by the loa     | ads - case |

| 6                                                                               | 73         |

| Figure 4.40 - MMC-FB efficiency evaluated under different loads - case 7        | 74         |

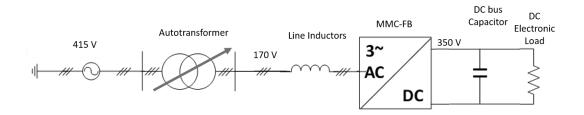

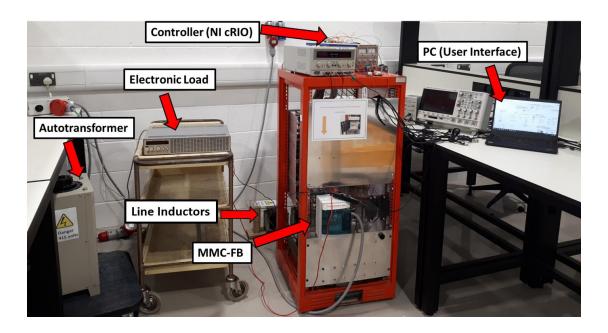

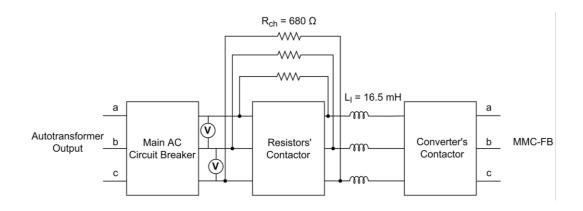

| Figure 5.1 - Schematic diagram of the TPS experimental setup                    | 77         |

| Figure 5.2 - The TPS experimental setup                                         | 78         |

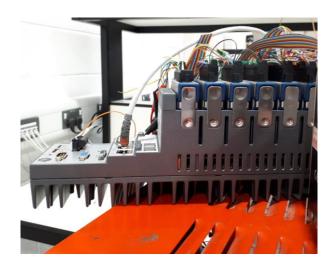

| Figure 5.3 - Full-bridge submodule                                              | 79         |

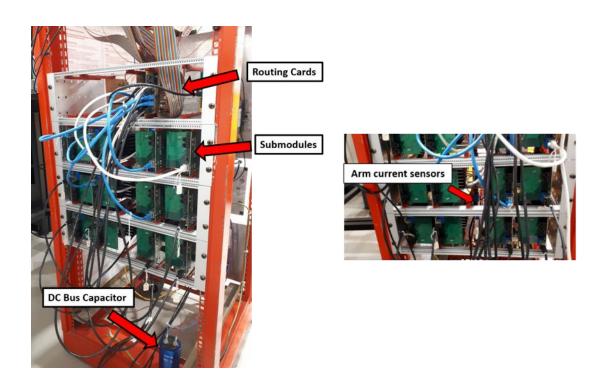

| Figure 5.4 - MMC-FB experimental setup                                          | 79         |

| Figure 5.5 - MMC-FB experimental setup                                          | 80         |

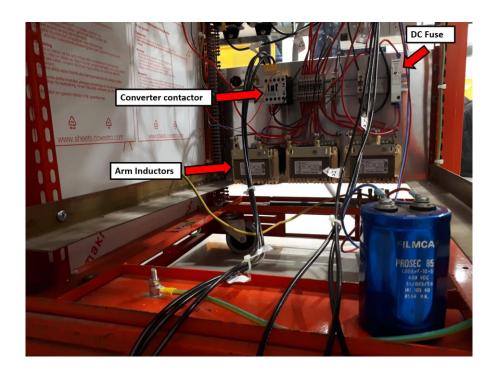

| Figure 5.6 - Diagram of connected contactors on the AC side of MMC-FB           | 81         |

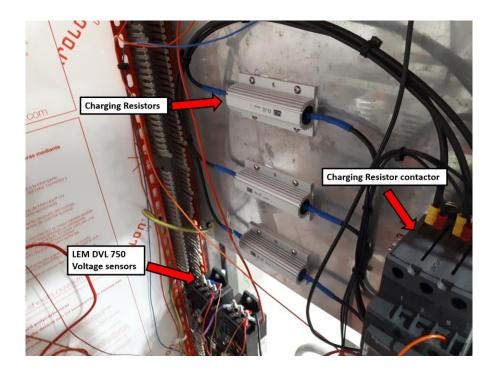

| Figure 5.7 - Charging resistors and voltage transducers on the AC side of the M | ИМС-FВ     |

|                                                                                 | 81         |

| Figure 5.8 - MMC-FB control unit: NI cRIO-9082                                  | 82         |

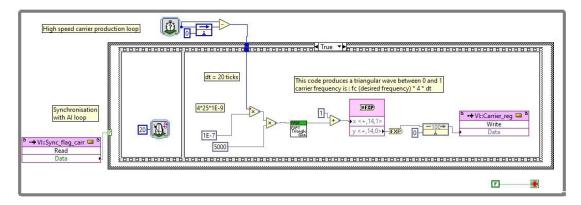

| Figure 5.9 - Carrier production loop - FPGA program                             | 83         |

| Figure 5.10 - The second loop - FPGA program                                    | 84         |

| Figure 5.11 - The second loop, part A - FPGA program84                                          |

|-------------------------------------------------------------------------------------------------|

| Figure 5.12 - The second loop, part B - FPGA program85                                          |

| Figure 5.13 - The second loop, part C - FPGA program86                                          |

| Figure 5.14 - The second loop, part D - FPGA program: (a) True case (b) False case86            |

| Figure 5.15 - The third loop - FPGA program                                                     |

| Figure 5.16 - Block diagram of the RT program                                                   |

| Figure 5.17 - Front panel of the RT program90                                                   |

| Figure 5.18 - The procedure for start-up and shut-down of the experimental setup91              |

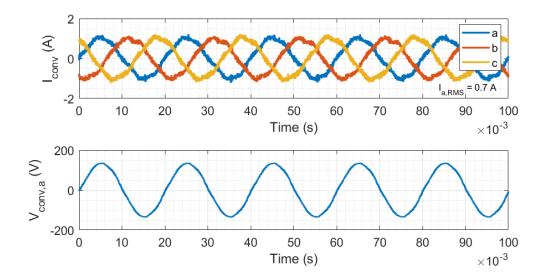

| Figure 6.1 - AC references and voltage of phase 'a' on the converter side - $IDC = 0.94$        |

| Figure 6.2 - DC bus voltage - $IDC = 0$ 94                                                      |

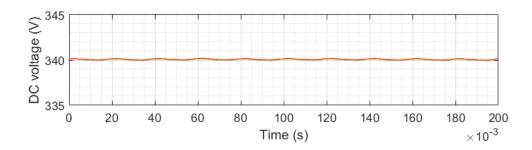

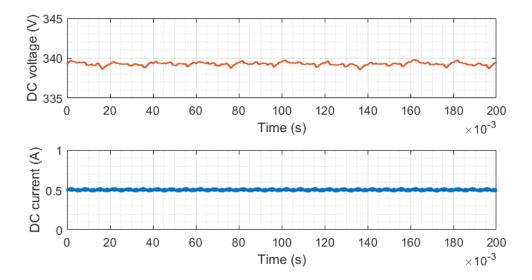

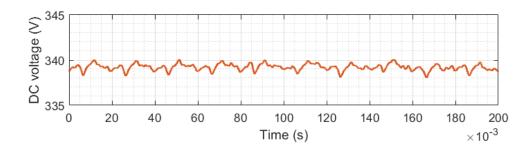

| Figure 6.3 - DC voltage and current - $IDC = 0.5 \text{ A}$                                     |

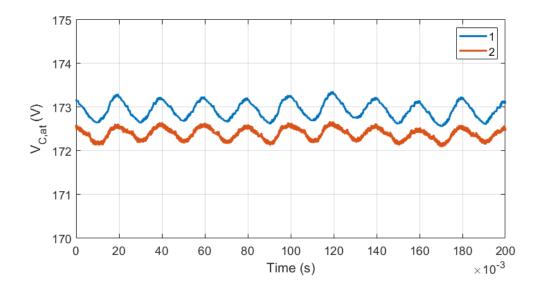

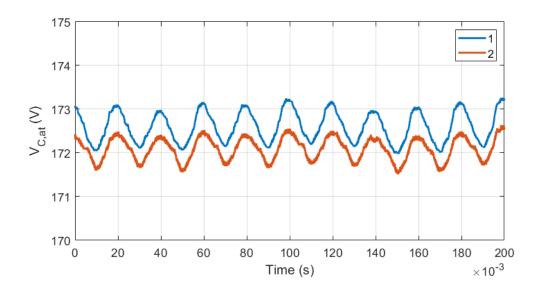

| Figure 6.4 - Capacitor voltages in the top arm of phase 'a' of the MMC-FB - $IDC = 0.5$         |

| A96                                                                                             |

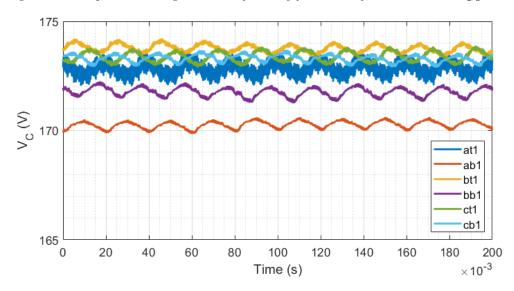

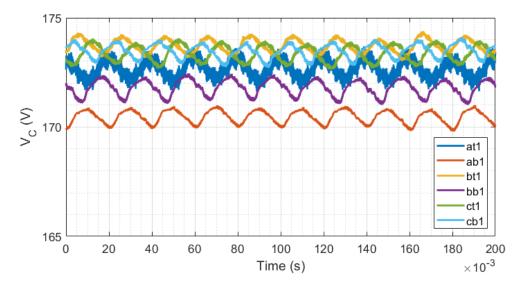

| Figure 6.5 - Capacitor voltages of the first submodule in each arm of the MMC-FB -              |

| IDC = 0.5  A96                                                                                  |

| Figure 6.6 - Phase currents and voltage of phase 'a' on the converter side - $IDC = 0.5$        |

| A97                                                                                             |

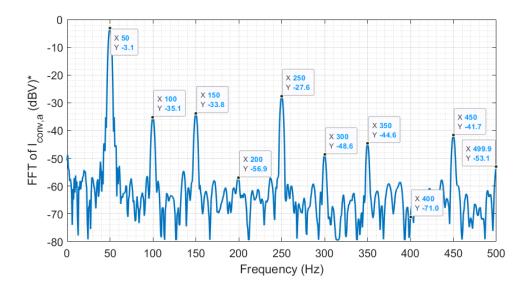

| Figure 6.7 - FFT analysis of the phase current (phase 'a') on the converter side - <i>IDC</i> = |

| 0.5 A                                                                                           |

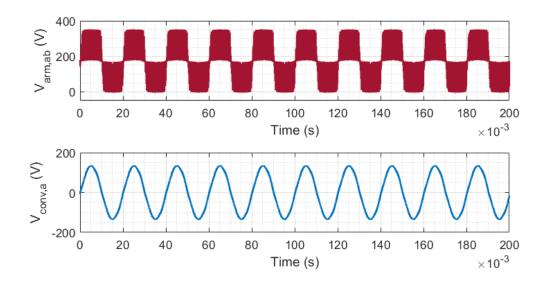

| Figure 6.8 - Voltage of the bottom arm in phase 'a' of the MMC-FB and voltage of                |

| phase 'a' on the converter side - $IDC = 0.5 \text{ A}$                                         |

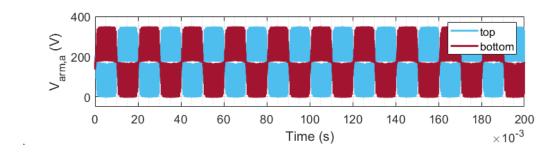

| Figure 6.9 - Voltage of the top and bottom arms in phase 'a' of the MMC-FB - <i>IDC</i> =     |

|-----------------------------------------------------------------------------------------------|

| 0.5 A99                                                                                       |

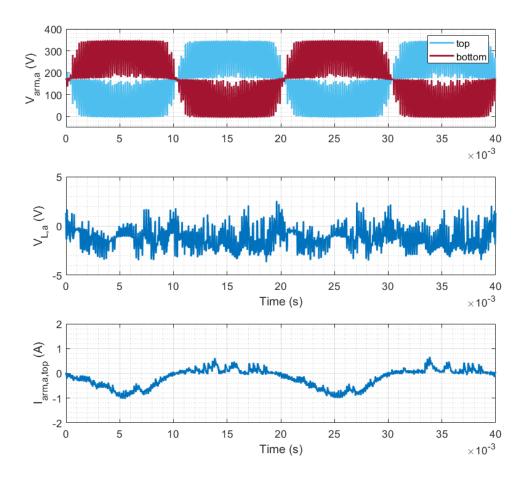

| Figure 6.10 - The arm voltages, arm inductor voltage and top arm current in phase 'a          |

| of the MMC-FB - $IDC = 0.5 \text{ A}$                                                         |

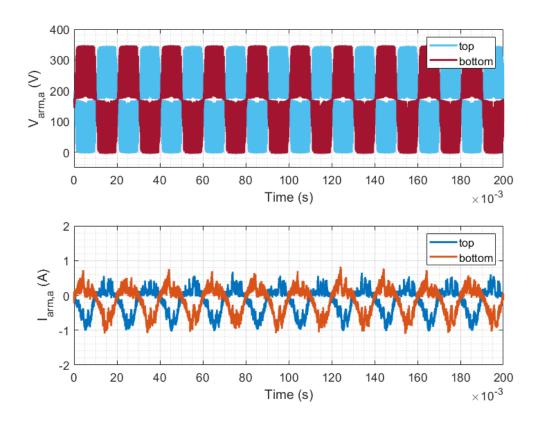

| Figure 6.11 - The arm voltages and currents in phase 'a' of the MMC-FB - $IDC = 0.5$          |

| A101                                                                                          |

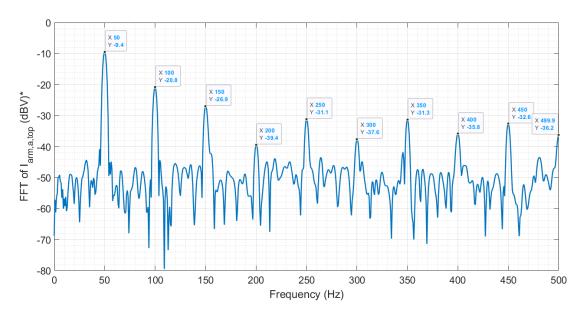

| Figure 6.12 – FFT analysis of the top arm current in phase 'a' of the MMC-FB - <i>IDC</i> =   |

| 0.5 A                                                                                         |

| Figure 6.13 - DC bus voltage - <i>IDC</i> = 1 A102                                            |

| Figure 6.14 - Capacitor voltages in the top arm of phase 'a' of the MMC-FB - $IDC = 1$        |

| A                                                                                             |

| Figure 6.15 - Capacitor voltages of the first submodule in each arm of the MMC-FB             |

| <i>IDC</i> = 1 A                                                                              |

| Figure 6.16 - Phase currents and voltage of phase 'a' on the converter side - $IDC = 1$ A     |

|                                                                                               |

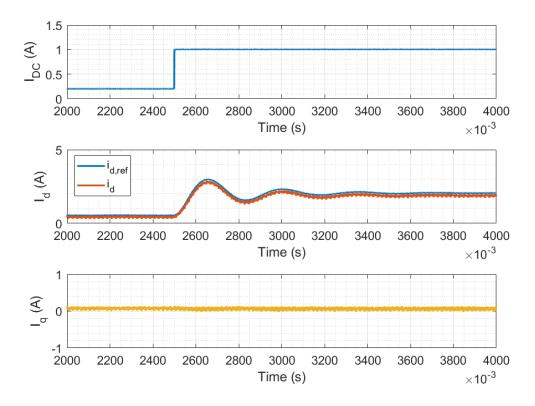

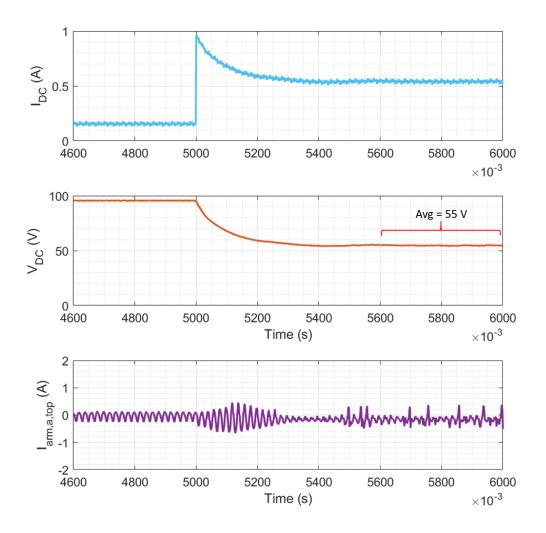

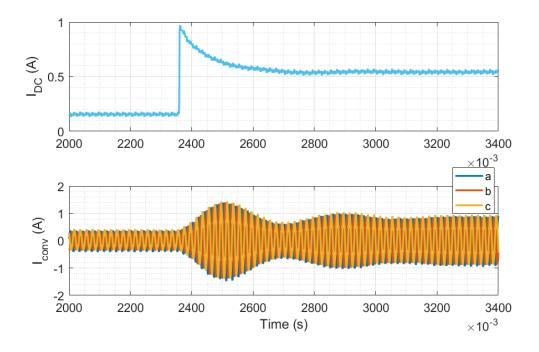

| Figure 6.17 - DC current, <i>id</i> and <i>iq</i> during the load change from 0.2 A to 1 A105 |

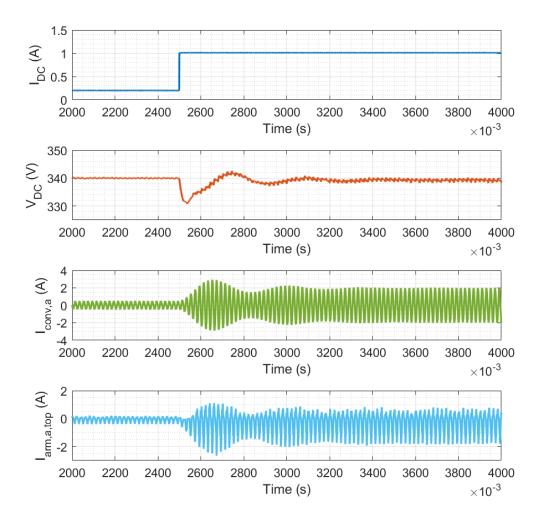

| Figure 6.18 - DC voltage, current of phase 'a' on the converter side and top arm current      |

| in phase 'a' of the MMC-FB during the load change from 0.2 A to 1 A106                        |

| Figure 6.19 - Capacitor voltages in the top arm of phase 'a' of the MMC-FB during the         |

| load change from 0.2 A to 1 A                                                                 |

| Figure 6.20 - Capacitor voltages of the first submodule in each arm of the MMC-FE             |

| during the load change from 0.2 A to 1 A107                                                   |

| Figure 6.21 - DC current, <i>id</i> and <i>iq</i> during the load change from 1 A to 0.2 A108 |

|-----------------------------------------------------------------------------------------------|

| Figure 6.22 - DC voltage, current of phase 'a' on the converter side and top arm current      |

| in phase 'a' of the MMC-FB during the load change from 1 A to 0.2 A109                        |

| Figure 6.23 - Capacitor voltages in the top arm of phase 'a' of the MMC-FB during the         |

| load change from 1 A to 0.2 A                                                                 |

| Figure 6.24 - Capacitor voltages in the top arm of phase 'a' of the MMC-FB during the         |

| load change from 1 A to 0.2 A                                                                 |

| Figure 6.25 - DC current and arm voltages in phase 'a' of the MMC-FB - DC short-              |

| circuit imitation                                                                             |

| Figure 6.26 - DC current and arm voltages in phase 'a' of the MMC-FB - cleared short-         |

| circuit                                                                                       |

| Figure 6.27 - DC current, DC voltage and top arm current in phase 'a' of the MMC-FB           |

| - DC short-circuit imitation                                                                  |

| Figure 6.28 - DC current and phase currents on the converter side - DC short-circuit          |

| imitation 115                                                                                 |

# **List of Tables**

| Table 2.1 - Notable events in development of traction systems [4], [8]–[10]7       |

|------------------------------------------------------------------------------------|

| Table 2.2 - SWOT analysis for MVDC railway electrification systems                 |

| Table 3.1 - Assumed operational conditions for the proposed MVDC railway           |

| electrification system21                                                           |

| Table 3.2 - Parameters of MVDC TPSs                                                |

| Table 3.3 - Parameters of MVDC TPS                                                 |

| Table 3.4 - Parameters of MMC-FB                                                   |

| Table 3.5 - Possible states for full-bridge submodule                              |

| Table 4.1 - Parameters of simulation case 4                                        |

| Table 4.2 - Parameters used in simulation case 5-1                                 |

| Table 4.3 - Average transferred power - cases 5-1 and 5-2                          |

| Table 4.4 - Simulation parameters - case 5-3                                       |

| Table 4.5 - Average power losses of the MVDC railway network between $t=0.5 s$ and |

| t = 0.8s - case 5-371                                                              |

| Table 4.6 - Simulation parameters - case 6                                         |

| Table 4.7 - Average power consumed in the MVDC railways - case 774                 |

| Table 5.1 – Specifications of the TPS experimental setup                           |

| Table 5.2 – AC-side voltage and <i>VDC</i> , <i>REF</i> in MMC-FB charging phase91 |

| Table 6.1 - Experimental conditions                                                |

# **List of Abbreviations**

| Term    | Explanation/Meaning/Definition                           |

|---------|----------------------------------------------------------|

| AI      | Analogue input                                           |

| AO      | Analogue output                                          |

| BCRRE   | Birmingham centre for railway research and education     |

| CSV     | Comma-separated values                                   |

| DCCB    | DC circuit breaker                                       |

| DG      | Distributed generation                                   |

| DO      | Digital output                                           |

| EMI     | Electromagnetic interference                             |

| dq      | direct-quadrature                                        |

| FFT     | Fast Fourier transform                                   |

| FPGA    | Field-programmable gate array                            |

| IGBT    | Insulated gate bipolar transistor                        |

| IGCT    | Integrated gate commutated thyristors                    |

| MMC-FB  | Modular multilevel converter with full-bridge submodules |

| MVDC    | Medium voltage DC                                        |

| NI cRIO | National Instruments Compact RIO                         |

| PETT    | Power electronic traction transformer                    |

| PI      | Proportional - Integral                                  |

| PV      | Photovoltaic                                             |

| Term    | Explanation/Meaning/Definition                    |

|---------|---------------------------------------------------|

| PLL     | Phase-locked-loop                                 |

| RMS     | Root mean square                                  |

| RT      | Real-time                                         |

| SFC     | Static frequency converter                        |

| STATCOM | Static synchronous compensator                    |

| SVC     | Static volt-ampere reactive compensator           |

| SWOT    | Strengths, Weaknesses, Opportunities, and Threats |

| TDD     | Total demand distortion                           |

| THD     | Total harmonic distortion                         |

| TPS     | Traction power substation                         |

|         |                                                   |

#### 1 INTRODUCTION

The mainline and high-speed electric railways are usually supplied by AC railway electrification systems at medium voltage level, which are single-phase supplies and cause imbalance on the three-phase public AC networks [1]. Therefore, the AC railways are typically connected to a high-voltage AC transmission line to mitigate the unbalanced loading issue [2]. This usually involves expensive equipment and connection works. In addition, high-voltage AC transmission lines are not always located near the railway traction power substations (TPSs), causing more cost for the railway electrification projects.

DC railway electrification systems draw balanced currents from the public AC networks using AC-DC power converters and they are usually used to supply urban railways and metros. This is because protecting DC lines needs complicated and costly DC circuit breakers [3], and thus, the voltage level of the DC electrification systems is limited to 4 kV [4]. This low voltage level, in turn, increases the voltage drop and transmission losses when the power consumption becomes higher.

Mitigating technical challenges of the traditional DC electrification systems can lead to development of a new electrification system for the high-speed lines with higher DC voltage levels such as 25 kV DC. Having low impact on the AC networks, power electronic converters make it possible to provide medium-voltage DC (MVDC) supply from widely available AC distribution networks. Moreover, it is possible to limit DC short-circuit currents by the power converters [5] and reduce the current ratings of the DC circuit breakers. Thanks to fully controlled bidirectional converters, the MVDC railway electrification system can be well integrated with the AC distribution networks, supporting the networks by consuming/producing reactive power [1]. Moreover, the

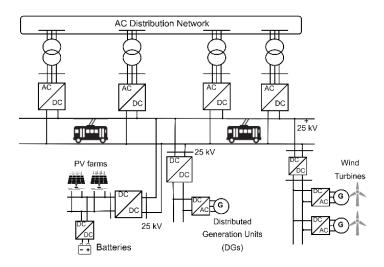

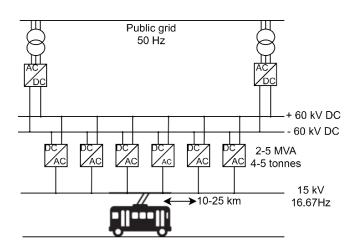

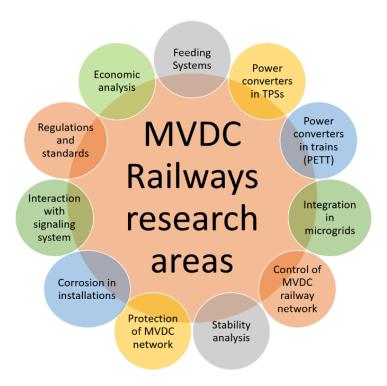

MVDC railways can have enough power capacity to integrate renewable power sources and create an MVDC microgrid. For instance, Figure 1.1 shows an MVDC microgrid where the distribution network, renewable energy sources, distributed generation units (DGs), and energy storages can flexibly interact with the railways [1], [3].

Figure 1.1 - MVDC railways as a part of a microgrid

In addition, the reactance of the overhead lines is theoretically zero in steady state, and thus, the voltage drop and reactive power consumption would be less than the AC railways [6]. Having no skin effect, the MVDC overhead lines can be realised with smaller cross-sectional area and lower cost [1]. In contrast to the AC railways, there is no need to implement neutral sections in the MVDC railways and the MVDC TPSs can be easily paralleled, which leads to reduction of the TPS power ratings [1], [7]. Inexistence of the neutral sections also simplifies the power diagram of the supply system and avoids power interruption and speed loss [7].

#### 1.1 Research objectives

Despite the advantages and due to practical challenges, MVDC railways have not been implemented in the railway industry. In particular, designing AC-DC power converters for the MVDC TPSs is one of the challenges towards developing the MVDC railways.

This is because the MVDC railway networks have unique characteristics which make them different from other MVDC networks. For instance, the electric trains are located between the network nodes and their power profile is dramatically changed during traction cycles (acceleration, coasting and braking). The power converter of the MVDC TPSs should be able to control the active and reactive power transfer between the MVDC railways and public AC networks while complying with power quality standards. Moreover, the MVDC TPS converter must have DC short-circuit current controller to tackle MVDC overhead line protection issue.

The aim of this research is to propose an MVDC railway electrification system for high-speed lines. As one of the main elements of the system, this research focuses on power converter of the MVDC TPSs. Based on the literature review and among the high-power AC-DC converter topologies suitable for the medium-voltage applications, modular multilevel converter with full bridge submodules (MMC-FB) has been found to be a promising topology for the MVDC TPSs. Hence, an MMC-FB is designed for the proposed MVDC electrification system and its performance is evaluated under various operating conditions. This overarching aim is achieved through the following objectives:

- To review the feeding arrangements proposed for the MVDC railway electrification systems in the technical literature.

- To define the specifications of the proposed MVDC electric railway system.

- To design an MMC-FB for the MVDC TPSs and propose a control and modulation scheme for the MMC-FB.

- To validate the MMC-FB design and the proposed control and modulation scheme by simulating an individual MVDC TPS equipped with the MMC-FB.

- To estimate the MMC-FB losses and its efficiency curve under various load conditions using the developed simulation model.

- To assess performance of the MMC-FBs in a double-end fed MVDC railway in the presence of renewable power sources by extending the simulation model.

- To analyse performance of the MMC-FBs in a MVDC railway network with multiple TPSs by an expanded simulation model.

- To build a small-scale lab demonstrator of an individual MVDC TPS and assess

the control and modulation scheme proposed for the MMC-FB using the

hardware setup.

#### 1.2 Publications

Several parts of this PhD research project have been published in a peer-reviewed journal and two international conferences:

- S. Sharifi, I. Ferencz, T. Kamel, D. Petreuş, P. Tricoli, "Medium-Voltage DC Electric Railway Systems: a review on feeding arrangements and power converter topologies", IET Electrical Systems in Transportation, vol. 12, no. 4, pp. 223–237, September 2022.

- S. Sharifi and P. Tricoli, "Medium voltage DC (MVDC) railway electrification systems: Assessment of performance," in World Congress on Railway Research 2022, June 2022.

- S. Sharifi, T. Kamel, P. Tricoli, "Investigating the best topology for Traction Power Substations (TPSs) in a Medium Voltage DC (MVDC) railway electrification system", in 23rd European Conference on Power Electronics and Applications (EPE'21 ECCE Europe), September 2021.

The research has been also presented in Centre for Power Electronics (CPE) Annual Conference 2021:

• S. Sharifi, P. Tricoli, C. Roberts, "Flexible Medium Voltage DC Electric Railway System," in Centre for Power Electronics (CPE) Annual Conference, July 2021, poster presentation.

The work presented in this thesis has been undertaken as part of Flexible medium voltage DC electric railway systems (MVDC-ERS) project funded by Shift2Rail Joint Undertaking (JU) under grant agreement No 826238.

#### 1.3 Thesis outline

The rest of this PhD thesis is organised as follows:

Chapter 2, 'Literature review', reviews the commonly used railway electrification systems and the feeding arrangements proposed for the MVDC railways in the literature. Moreover, it presents the high-power AC-DC converter topologies suitable for the MVDC TPSs.

Chapter 3, 'modelling the proposed MVDC electric railway system and modular multilevel converter', introduces the proposed MVDC railway electrification system and presents the methodology used for modelling the MVDC railway system, MMC-FB, proposed control and modulation scheme for the MMC-FB, and DC short-circuit current controller. Finally, this chapter discusses the MMC loss modelling.

Chapter 4, 'Simulation analysis of MVDC railways', describes the performance of the MVDC railway system in various simulation cases. It also presents the results for the loss estimation using the simulation model.

Chapter 5, 'Experimental setup of an MVDC TPS, introduces the hardware and software design of the small-scale lab demonstrator devolved for an individual MVDC TPS.

Chapter 6, 'Experimental results', discusses the performance of the small-scale lab demonstrator tested under constant DC loads, DC load change, and DC-side short-circuit.

Chapter 7, 'Conclusion and future work', draws conclusions of this research project and presents the possible areas of research related to the MVDC railways.

#### 2 LITERATURE REVIEW

#### 2.1 Conventional railway electrification systems

Currently, there are various kinds of electric traction systems around the world. The first electric traction systems were based on DC power supplies. The most notable events in early stages of development of traction systems have been presented in Table 2.1.

Table 2.1 - Notable events in development of traction systems [4], [8]–[10]

| Notes                         | Date          | Location         |

|-------------------------------|---------------|------------------|

| Experiments on battery        | 1837          | Massachusetts,   |

| propulsion                    |               | USA              |

| Experiments on battery        | 1838          | Scotland         |

| propulsion                    |               |                  |

| Power supply along with       |               |                  |

| traction line – The use of    | 1879          | Berlin, Germany  |

| small DC locomotive           |               |                  |

| Electric tram line 1881       |               | Berlin-          |

|                               | Lichterfelde, |                  |

|                               | Germany       |                  |

| Electric railway              | 1883          | Brighton, UK     |

| Electric streetcar line       | 1884          | Cleveland, Ohio, |

|                               |               | USA              |

| Tramway network with          | 1886          | Montgomery,      |

| simple overhead wire          |               | Alabama, USA     |

| Electric tramway network      | 1888          |                  |

| with sprung DC motors -       |               | Richmond,        |

| speed control using rheostat  |               | Virginia, USA    |

| and field control             |               |                  |

| Underground electric traction | 1890          | London and       |

| in urban areas                |               | Liverpool, UK    |

| Underground electric traction | 1895          | Baltimore,       |

| in urban areas                |               | Maryland, USA    |

Initially, the electric traction systems were mainly realised by DC or single-phase AC (universal) motors [4]. Based on the requirements of these traction motors and other technical and regional matters, the electric traction systems have been developed in various paths. Expansion of low-voltage DC systems, and emerging medium-voltage AC systems were two major technical solutions. While in Central Europe, the frequency for the AC electrification systems was selected to be  $16\frac{2}{3}$  Hz, it was chosen to be 25 Hz in the United States of America. The medium-voltage AC electrification system with 50 and 60 Hz was also implemented in 1950s and introduced as a replacement for some of the old low-voltage DC railways [11].

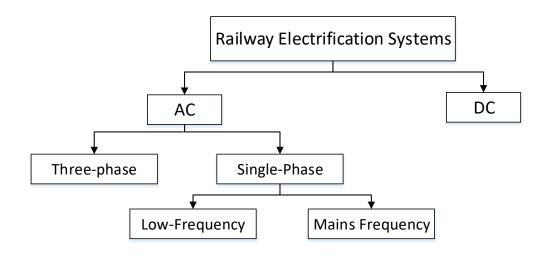

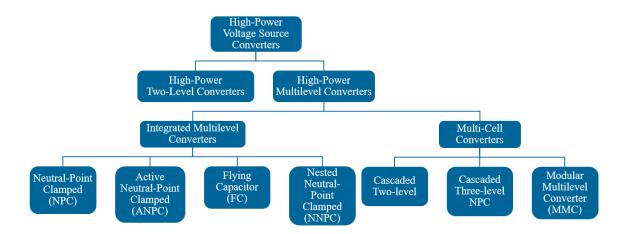

The commonly used railway electrification systems are classified in Figure 2.1 and are discussed in the following sections.

Figure 2.1 - Commonly used railway electrification systems

#### 2.1.1 Low-voltage DC systems

Having torque-speed characteristics compatible with the traction cycles, separately excited and series DC motors were suitable for the trains [11] and hence, the DC supplies were appropriate solutions in the earliest stages of the railway systems development. First, DC electrification systems with nominal voltages around 0.5 kV were developed to supply trams and metros. Having high voltage drops and power

losses, these systems were not able to supply the lines with high traffic volume. Therefore, the DC systems with higher nominal voltages, e.g. 0.75, 1.5, and 3 kV were introduced [4]. Moreover, 3 kV DC systems were developed in the United States of America between 1914 to 1916 [12]. Following this, 4 kV DC railways were used for Torino-Ceres railway in Italy in 1920 [4]. The DC systems with nominal voltages higher than 3 kV were also implemented in Belgium, Poland and Spain [1].

To use DC electrification systems for the mainlines and high-speed railways, it was needed to further increase the voltage level to decrease the power losses and voltage drops. However, the voltage level of DC systems was limited to 4 kV, mainly because of protection matters. In fact, DC circuit breaker suitable for higher voltage and current ratings were expensive and complicated due to lack of zero-crossing in DC voltages and currents. As a result, medium-voltage AC systems were chosen as suitable systems for the high-speed railways.

#### 2.1.2 Single-phase AC systems with low frequency

The single-phase AC railway electrification systems with low frequency have been used in the United States of America and European countries such as Switzerland, Germany, Sweden, Austria and Norway. In these systems, on-board transformers are used to step down overhead line voltage (10 – 15 kV) to the voltage levels appropriate for the motor drives. As two examples, the New York – New Haven line was electrified by 11 kV, 25 Hz system in 1906 and the Dessau-Bitterfeld line was realised by 10 kV, 15 Hz supply system in 1911 [4].

The series commutator motors were mainly used as traction motors in the AC railways.

These motors had high maintenance costs due to sparks during commutation process.

As the number of sparks is proportional to the frequency of the supply system, the

system designers decided to reduce the supply frequency to  $16\frac{2}{3}$  (where the mains frequency is 50 Hz) or 20 - 25 (where the mains frequency is 60 Hz). In addition, choosing lower frequencies has led to other technical advantages over the AC railways operating at mains frequency, such as less reactance and voltage drops and less skin effect in the overhead line conductors. The benefits in terms of voltage stability, electromagnetic compatibility and transmission losses have been also investigated in [13]. On the other hand, the on-board transformers in the low-frequency supply systems are bulkier and have negative impact on the system efficiency.

This electrification system can be developed in two forms [4]:

- 1) Centralised system, in which a dedicated power system consisted of generators and transmission and distribution lines is constructed for the railway network. Before 1900, this was the preferred form as the public grid was not widely available.

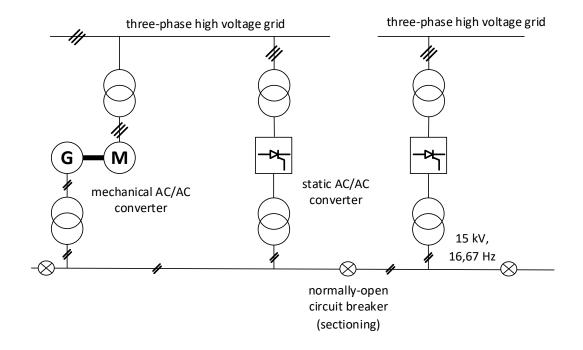

- 2) Distributed system, in which the railway lines are connected to three-phase public grids via frequency converters. This form, shown in Figure 2.2, became more economical when the public grid and the railway loads were more expanded. In this configuration, the TPSs should be isolated by neutral sections when they are connected to different public grids with different phase and frequency.

Initially, rotating converters (electric machines with different number of pole pairs) were used for the frequency conversion. In 1980s and 1990s, the rotating converters were replaced by static cyclo-converters [14]. In cyclo-converters, thyristors are used to perform direct AC/AC conversion. The output waveform, however, is not purely sinusoidal and contains harmonic contents. Back-to-back converters were then proposed and implemented to tackle this issue. In these converters, insulated gate

bipolar transistors (IGBTs) or integrated gate commutated thyristors (IGCTs) are used to realise a rectifier and an inverter stage to indirectly convert the frequency.

Figure 2.2 - low-frequency AC railways - Distributed form [4]

#### 2.1.3 Single-phase AC systems operating at mains frequency

Development of static rectifiers after the World War II made it possible to feed the DC traction motors by an AC supply system. Therefore, the AC supply systems could be directly connected to the public AC networks without frequency conversion. In addition, motor drives were developed enough to drive three-phase induction motors [4], providing more options for selecting traction motors.

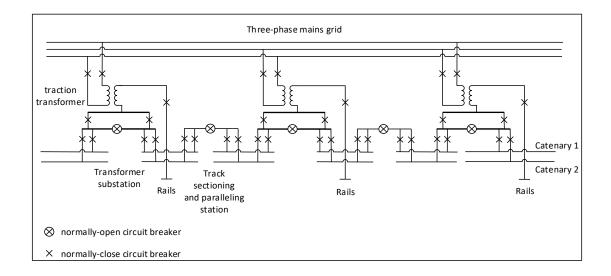

The 25 kV, 50 (60) Hz electrification system is widely used for mainlines and high-speed railways. Figure 2.3 illustrates a typical 25 kV AC railway electrification system [15], where the traction transformers of the substations feed the trains. Supplying single-phase AC railways from the three-phase mains grid causes unbalanced loading issue. Hence, the adjacent substations are fed by different phases of the mains grid to

reduce this negative effect. As a result, the substations should be isolated by neutral sections.

Figure 2.3 - A typical 25 kV, 50 (60) Hz supply system [15]

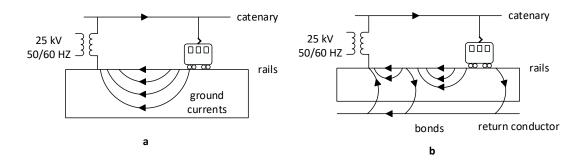

There are various configurations for realising 25 kV, 50 (60) Hz systems. The simplest arrangement, shown in Figure 2.4 (a), consists of a transformer directly connected to the railway supply system. This arrangement, however, suffers from high line impedance and voltage drops, considerable rail-to-earth potential difference and safety issues, and high ground currents which might cause interference with the adjacent communication devices [15].

Figure 2.4 - Various configurations for 25 kV, 50 (60) Hz railways [15]: a) Direct connection via a transformer b) Direct connection via a transformer and a return conductor

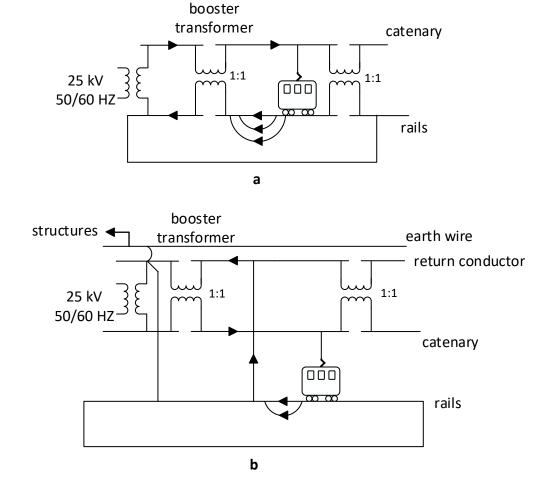

As depicted in Figure 2.4 (b), a return conductor bonded to the rails can reduce the return path impedance. Another solution is to use booster transformers, installed in every 3 – 4 kilometres. According to Figure 2.5 (a), the booster transformers with unity turns ratio are installed between the overhead lines and rails. In this way, almost all the return current flows through the secondary of the booster transformer. Figure 2.5 (b) presents an alternative for this arrangement, where a return conductor is installed together with the booster transformers to absorb the return current.

Figure 2.5 - 25 kV, 50 (60) Hz railways with (a) Booster transformer (b) Booster transformer and a return conductor [15]

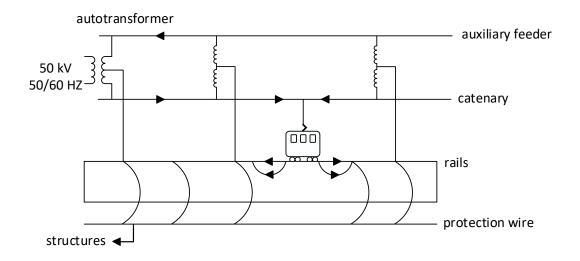

Figure 2.6 demonstrates another established arrangement for the 25 kV, 50 (60) Hz railways, which consists of autotransformers with unity turns ratio connected to the

overhead lines and an auxiliary feeder. The centre tap of the autotransformer is connected to the rails, and the voltage on the primary side is 50 kV. Therefore, the trains are supplied at 25 kV but the input voltage is higher (50 kV). This makes it possible to increase the distance between the traction substations. In addition, the return current is forced to flow through the autotransformers.

Figure 2.6 - Implementation of autotransformers in 25 kV, 50 (60) Hz railways [15]

As mentioned, the single-phase 25 kV railways cause imbalance on the three-phase public AC networks. Hence, these electrification systems are typically supplied by a high-voltage AC transmission line [2]. Balanced transformers have been proposed and used to alleviate the unbalanced loading problem by creating a balanced two-phase system. Impedance matching, Le-Blanc, Scott, and Woodbridge transformers are the most notable designs. In addition, the use of balanced transformers can attenuate harmonic distortions in some cases. Nevertheless, these transformers cannot entirely solve the unbalanced loading issue, since they operate as a balanced three-phase transformer only when the output phases are equally loaded [2], and this is not usually the case.

The imbalanced loading and voltage drops can also be reduced by Static volt-ampere reactive compensators (SVCs). The SVCs uses thyristors to switch reactors and/or capacitors. The switching of the thyristors, however, produces unwanted harmonic contents which should be filtered by bulky passive filters. The Static synchronous compensators (STATCOMs) are also a solution for improve the power quality on the public AC networks. Operating based on switch-mode converters, STATCOMs are able to act as active filters and eliminate the unwanted harmonic contents produced by the railway network with smaller filters than those implemented in SVCs [14].

The 25 kV 50 (60) Hz railways are also realised by Static frequency converters (SFCs). In these converters, the three-phase AC voltage is rectified to DC voltage in the first stage, and it is converted to single-phase 50 (60) Hz voltage for the railway network in the second stage. Therefore, the railway TPSs draw balanced and high-quality currents from the three-phase AC network, and thus, the railway network can be connected to the AC networks with lower voltage levels and the neutral sections can be removed from the railway system. In addition, the power factor and short circuit currents can be fully controlled by the converters. It is also possible to share the load among the TPSs in the railway network [14]. On the other hand, SFCs are more complex and generally less energy-efficient in comparison to the transformers.

#### 2.1.4 Three-phase AC systems with low frequency

The three-phase asynchronous motors became an option for the traction applications in the early of the twentieth century. Feeding these motors via feeders with voltage level of a few kV was technically viable, and this led to development of a three-phase AC railway electrification system. As there were no reliable adapter gear units available at that time, the motors were connected to the train wheels by means of a crank. Hence,

the motor speed was limited to the speed of the wheels and the trains speed was controlled by changing the number of poles of the motors. To operate the trains at 50-60 km/h speed and less, the supply frequency had to be reduced.

A three-phase 16.7 Hz electrification system was developed in Switzerland in 1985 [4]. The three-phase railway supplies were also implemented in Italy, Hungry and United States of America. The voltage level of the overhead lines was chosen up to 3 kV, and the motors were supplied by two parallel overhead lines [4].

Due to insulation considerations, the structure of the overhead lines was complicated at junctions. In addition, the trains speed was limited to 100 km/h because of two-wire contact lines and mechanical constrains linked to them. In addition, because of the strong coupling between motor speed and synchronous speed, speed control was difficult. Furthermore, there were ripples in the power consumed by the motors as a result of the rigid connection between the motors and wheels, causing interference with the nearby communication lines [4].

After a few years of operation and because of the technical issues, the three-phase railway supplies were abandoned in almost all countries and were replaced by low-frequency single-phase AC or DC railways.

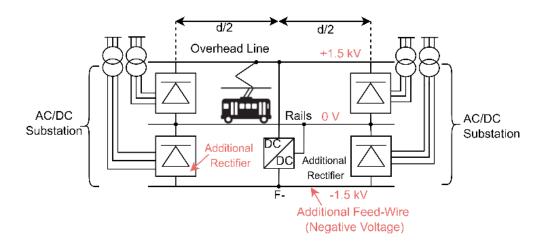

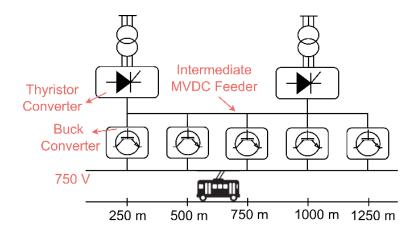

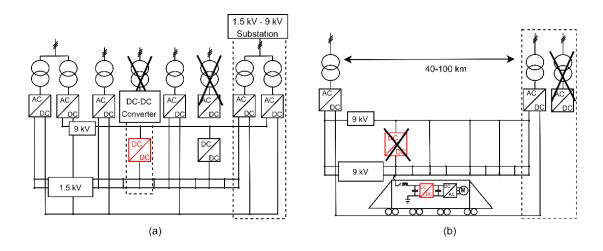

#### 2.2 Proposed feeding arrangements for MVDC railways

The idea of increasing voltage level of the DC railway electrification systems has been proposed since 1989 [16]. However, this system has not been implemented in the railway industry due to technical challenges. The feeding arrangements proposed for the MVDC railways can be classified into two groups: 1) Systems with MVDC intermediate feeders; and 2) Systems with MVDC overhead lines. Appendix A presents

the review paper published by the author of this PhD thesis in which these proposals are thoroughly reviewed (section 2).

Table 2.1 presents a Strengths, Weaknesses, Opportunities and Threats (SWOT) analysis for the MVDC railway electrification system to demonstrate its advantages over the traditional solutions and elaborate the challenges. Some of the strengths and opportunities are demonstrated in this thesis. This thesis also deals with the weakness related to the design and development of the power converters for the MVDC TPSs.

Table 2.2 - SWOT analysis for MVDC railway electrification systems

#### **Strengths**

- Low impact on the main three-phase AC networks (no imbalanced loading)

- Ability of limiting DC short circuit currents by power converters

- Facilitating the integration of renewable power sources and creating microgrids

- Negligible voltage drop and reactive power consumption due to negligible reactance in steady state

- Simple power diagram without neutral sections

- No skin effect in the overhead lines and smaller and lighter overhead lines

- Having less conversion stages in the power converters and possibly higher power efficiencies (in comparison to 25 kV AC railways realised by static frequency converters)

#### Weaknesses

- The need for DC circuit breakers and more expensive protection equipment

- Lack of experience in topology selection, design and development of the power converters for the MVDC TPSs

- Power losses in the power electronic converters (both in TPSs and in PETTs)

- Complex central control unit and the need for bidirectional data transfer (in the case of implementing power sharing schemes)

- Possibility of corrosion on installations

#### **Opportunities**

- Possibility of using the same infrastructure as 25 kV AC railways

- Integrating MVDC railways to widely available AC distribution networks rather than high-voltage AC transmission networks

- Bidirectional active power transfer with the main three-phase AC networks (absorbing regenerated energy from the brakes, injecting generated power by the renewable resources to the main grid)

- Providing reactive power support for the main three-phase AC networks

- Possibility of power sharing between the MVDC TPSs and reducing the power capacity of the TPSs.

- Possibility of increasing the speed of the trains (as there are no neutral sections, and thus, there are no power interruptions)

#### **Threats**

- The reliability of the TPSs and PETTs needs to be evaluated

- There are research areas which need to be further investigated (as will be discussed in section 7.1 and section 4 of Appendix A)

- There are no approved standards for the MVDC railways at the moment

- The need for power electronic traction transformers (PETT) on the trains, which implies that all the rolling stocks need to be redesigned/modified

#### 2.3 Converter topologies suitable for the MVDC TPSs

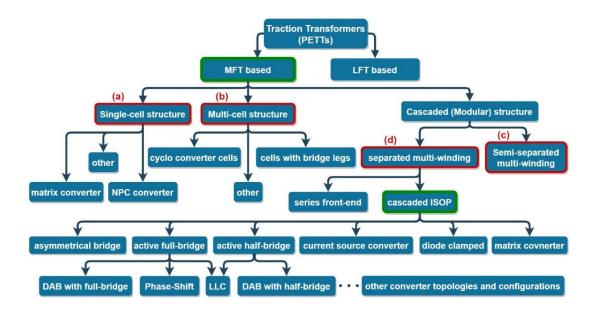

Considering the requirements of an MVDC railway electrification system with 25 kV overhead lines, the high-power AC-DC converter topologies have been analysed in the published review paper (Appendix A, section 3.1). Based on this study, MMC-FB has been identified as a feasible and promising solution for the power converters of the MVDC TPSs.

# MODELLING THE PROPOSED MVDC ELECTRIC RAILWAY SYSTEM AND MODULAR MULTILEVEL CONVERTER

In this chapter, specifications of the proposed MVDC electric railway electrification system are defined. Then, an individual MVDC TPS is modelled, and the assumptions made in the modelling are discussed. The TPS converter, realised by MMC-FB topology, is the main part of the TPS. The MMC-FB designed for the MVDC TPSs and the proposed control and modulation units are described in detail. Finally, the method used for evaluating MMC-FB losses and efficiency is presented. The TPS modelling is done in Matlab/Simulink environment, and the simulation results are presented in the next chapter.

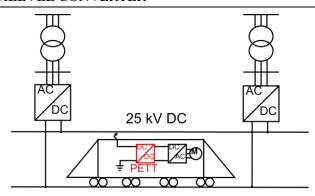

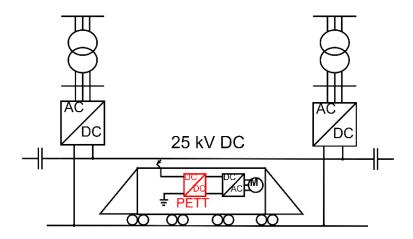

#### 3.1 Specifications of the proposed MVDC railway electrification system

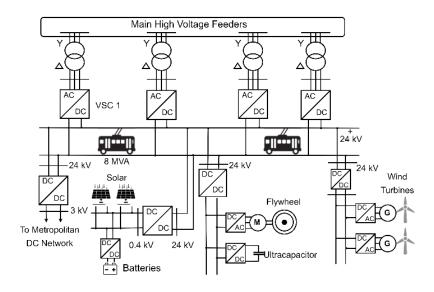

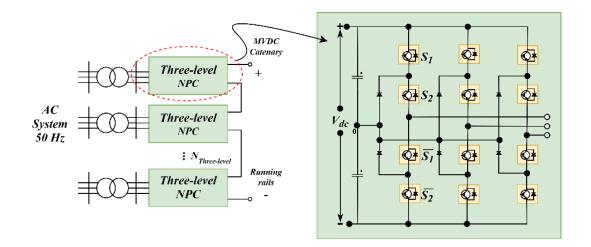

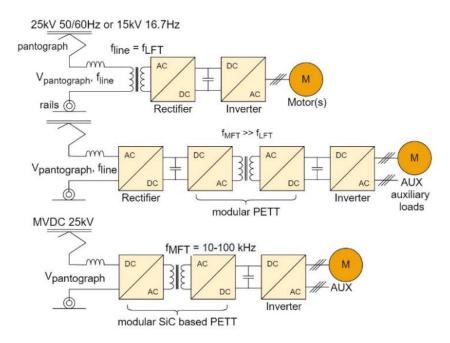

The arrangement for the proposed MVDC railway electrification system is illustrated in Figure 3.1. The AC-DC power converters of the MVDC TPSs provide DC voltage from AC distribution networks. In addition, a PETT is installed on each rolling stock to convert the MVDC overhead line voltage to the voltage levels suitable for the motor drives. The nominal voltage chosen for the proposed MVDC electrification system is 25 kV DC. In this way, the existing infrastructure for 25 kV AC railways can be used for MVDC railways in the future. In addition, MVDC railways with 25 kV feeders will have enough capacity to transfer energy between the renewable power sources, distribution network and railway TPSs.

Figure 3.1 - The proposed MVDC railway electrification system

So far, MVDC railways have not been implemented in the industry. Therefore, there are no defined standards for their operation. As the operation conditions in MVAC and MVDC railways can be similar, the parameters defined in the standards for MVAC railways [17] are chosen for the proposed MVDC electrification system. Table 3.1 shows the assumed operational conditions.

Table 3.1 - Assumed operational conditions for the proposed MVDC railway electrification system

| Parameter                     | Symbol       | Value (kV) |

|-------------------------------|--------------|------------|

| Lowest non-permanent voltage  | $U_{min2}$   | 17.5       |

| Lowest permanent voltage      | $U_{min1}$   | 19         |

| Nominal voltage               | $V_{DC,nom}$ | 25         |

| Highest permanent voltage     | $U_{max1}$   | 27.5       |

| Highest non-permanent voltage | $U_{max2}$   | 29         |

The long-term overvoltages can last between 20 milliseconds and 1 second. The catenary voltage can drop to  $U_{min2} < V < U_{min1}$  for no more than 2 minutes. In addition, the catenary voltage can increase to  $U_{max1} < V < U_{max2}$  for a maximum duration of 5 minutes. In the no-load condition, the output voltage of a TPS should be equal to or less than  $U_{max1}$ . In this research, the no-load and nominal voltage selected is 25 kV DC.

For 25 kV AC railways, the highest long-term overvoltage ( $U_{max3}$ ) is 38.75 kV. Considering that in AC systems, the Root Mean Square (RMS) of the nominal voltage is 25 kV while in DC systems the nominal voltage has a DC value of 25 kV, the highest long-term overvoltage for the MVDC electrification system can be smaller than that in AC railways. In this study, the value for  $U_{max3}$  is defined as  $U_{max2} + 10\% = 31.9$  kV. The proposed MVDC electrification system is designed for high-speed lines. As a typical value, the maximum load for each TPS is considered to be 16 MW. To increase the reliability of the system, it is desired to have at least two AC-DC power converters in each MVDC TPS. In this case, one converter is used as a reserve converter. In this study and for simplicity, each TPS is designed with one power converter. As the semiconductors of the power converters cannot be overloaded, the TPS converters should be designed for the peak load. In addition, the TPSs should be able to handle low-duration overloads. Hence, a margin of 4 MW (25%) is considered, and the power rating for each TPS (and its converter) is assumed to be 20 MW. Table 3.2 shows the parameters selected for the MVDC TPSs and their power converters.

Table 3.2 - Parameters of MVDC TPSs

| Parameter                                               | Symbol          | Value |

|---------------------------------------------------------|-----------------|-------|

| Maximum consumption (for each TPS)                      | $P_{max,load}$  | 16 MW |

| Power rating of each TPS                                | $P_{rated,TPS}$ | 20 MW |

| Number of AC-DC converters in each TPS                  | $N_c$           | 1     |

| Power rating of the power converter                     | $P_{rated,c}$   | 20 MW |

| Nominal DC voltage of the power converter               | $V_{DC,nom,c}$  | 25 kV |

| DC current of the power converter at full load of 16 MW | $I_{DC,full,c}$ | 640 A |

| Maximum DC current of the power converter               | $I_{DC,max,c}$  | 800 A |

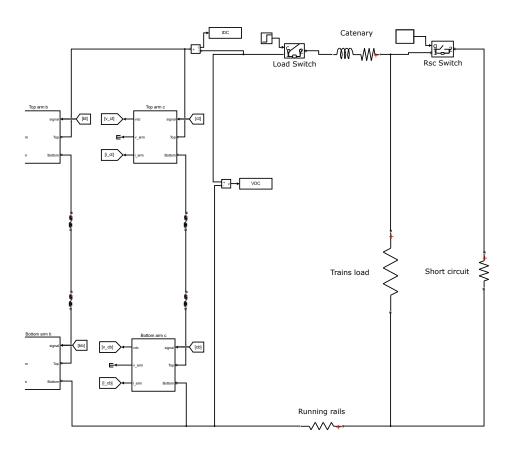

#### 3.2 Model of the MVDC railway

Figure 3.2 depicts the power diagram for an MVDC TPS. Each MVDC TPS is connected to an AC distribution network and is equipped with a Y-Y transformer to provide a suitable voltage level for the TPS converter. In this study, the distribution voltage level chosen is 33 kV, and the TPS transformer provides 11 kV on the converter side. The distance between the TPS and distribution network is 0.5 km, and the AC cable parameters are selected based on [18].

Figure 3.2 - The MVDC TPS model

The MVDC electrification system feeds the trains' load  $R_L$  through overhead lines, which are modelled by  $r_c$  and  $l_c$ . The running rails provide a path for return current. In the model, they are represented by  $r_r$ .

In this study, the simulation models are used to investigate the TPS converter's performance. Considering the converter's dynamic behaviour, the time span of the simulations is less than 1 second. During this time span, the trains' movement can be neglected. Therefore, the parameters for the overhead lines and running rails are constant during a simulation.

The MVDC system is a double-track railway system, i.e., the inbound and outbound trains are fed by two parallel feeding paths. Choosing contact wire conductors with a 150 mm<sup>2</sup> cross-sectional area for each feeding path, the equivalent inductance and

resistance of the overhead line equipment are assumed to be 1.55 mH/km and  $0.16\,\Omega$ /km, respectively. The running rails in each path have 15 m $\Omega$ /km resistance [19]. Similar to the conventional railway electrification systems, the potential difference between running rails and ground (as a result of current leakage) causes safety issues. In addition, the return path should be a low-impedance path to avoid voltage drops and facilitating short-circuit current detection. Hence, earthing and bonding should be considered during the MVDC system design.

Due to the same voltage level in MVAC and MVDC railways, the methods used for earthing and boning can be similar, concentrating on electromagnetic interference (EMI) issues. It should be noted that at a same power level, the current level in a 25 kV DC railway is less than a 25 kV AC railway as the there is less reactive power consumption in the MVDC system. This implies smaller potential differences between the running rails and ground. The detailed design of earthing and bonding system for the MVDC railway system is out of scope of this thesis.

As the parallel overhead lines (and the running rails) are bonded together in a double-track MVDC system, they can be assumed as parallel impedances. Hence, the double-track system is modelled and simulated by only one path, and the overhead line equipment (and running rail) impedances are halved. Table 3.3 summarises the parameters used in the simulation models.

Table 3.3 - Parameters of MVDC TPS

| Parameter                                                       |  | Value                           |

|-----------------------------------------------------------------|--|---------------------------------|

| Distribution network frequency                                  |  | 50 Hz                           |

| Distribution network voltage level                              |  | 33 kV                           |

| Voltage on secondary side of TPS transformer (converter side)   |  | 11 kV                           |

| Apparent power of TPS transformer                               |  | 20 MVA                          |

| Per unit resistance of TPS transformer                          |  | 1.1%                            |

| Per unit reactance of TPS transformer                           |  | 10%                             |

| Resistance of AC cables                                         |  | 60.1 mΩ/km                      |

| Inductance of AC cables                                         |  | 0.37 mH/km                      |

| Distance between TPS and distribution network                   |  | 0.5 km                          |

| Resistance of the overhead line equipment (double-track system) |  | $80.0~\text{m}\Omega/\text{km}$ |

| Inductance of the overhead line equipment (double-track system) |  | 0.78 mH/km                      |

| Resistance of the running rails (double-track system)           |  | $7.5 \text{ m}\Omega/\text{km}$ |

The developed model for an individual MVDC TPS is then extended to double-end fed and meshed MVDC railway system by connecting MVDC TPS models in Matlab/Simulink.

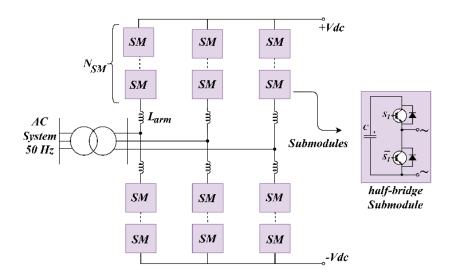

#### 3.3 MMC-FB model

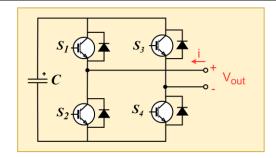

#### 3.3.1 Power circuit

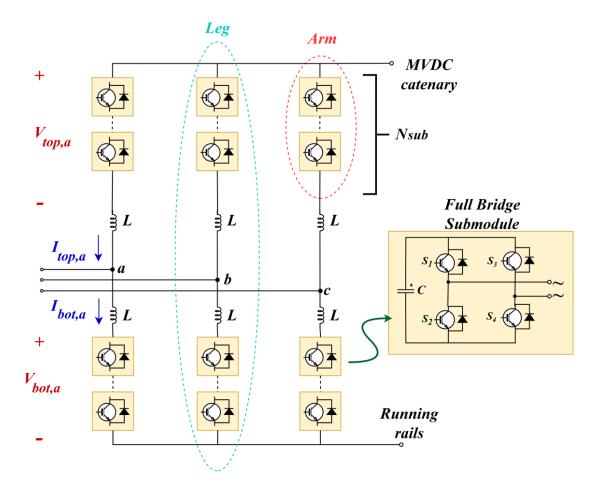

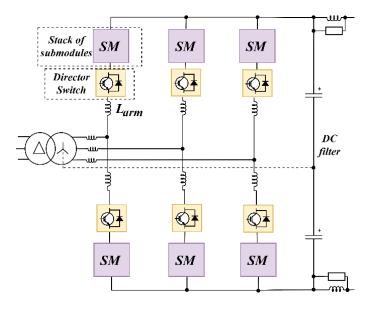

As shown in Figure 3.3, the MMC-FB power circuit consists of three legs, and each leg is formed by two arms. In each arm, there are  $N_{sub}$  full-bridge submodules and one arm inductor. Table 3.4 presents the parameters of the simulated MMC-FB.

The MMC-FB is designed for  $U_{max3} = U_{max2} + 10\% = 31.9$  kV on the DC side. Therefore, it is realised by eight submodules per arm. In the worst-case scenario, the capacitors in each submodule should be charged up to  $\frac{U_{max3}}{N_{sub}} = \frac{31.9 \text{ kV}}{8} = 4$  kV. This means that each IGBT in the full-bridge submodules should be able to block 4 kV and the submodules can be realised by 6.5 kV IGBTs, considering enough safety margin

for their operation [20]. The MMC-FB design can be easily extended to operate at higher DC voltages by increasing the number of submodules in each arm. In other words, even if a  $U_{max3}$  higher than 31.9 kV is selected, the design of the MMC-FB does not change dramatically.

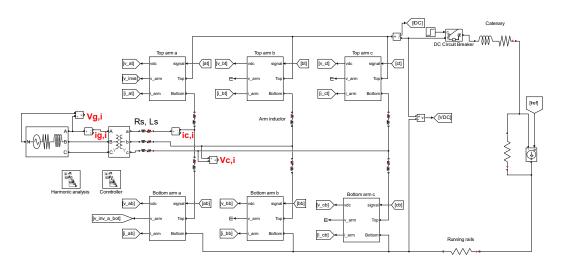

Figure 3.3 - Power circuit of the MMC-FB

Table 3.4 - Parameters of MMC-FB

| Parameter                                          | Symbol      | Value   |

|----------------------------------------------------|-------------|---------|

| Number of submodules (per arm)                     | $N_{sub}$   | 8       |

| Nominal voltage of the capacitor in each submodule | $V_{C,nom}$ | 3.13 kV |

| Capacitance (per submodule)                        | $C_{sub}$   | 10 mF   |

| Arm inductance                                     | $L_{arm}$   | 8 mH    |

| Resistance of the arm inductor windings            | $R_{arm}$   | 0.01 Ω  |

| Carrier frequency                                  | $f_c$       | 3 kHz   |

To select a proper IGBT for the MMC-FB, the maximum arm current needs to be evaluated. Assuming a lossless converter, displacement factor of 1 (( $\cos(\varphi_1) = 1$ ) and modulation index of 0.7 (m = 0.7), the equations below estimate the maximum arm current. First, the maximum phase voltage on the AC side is calculated:

$$V_{AC,phase,peak} = \frac{1}{2} m V_{DC} \rightarrow V_{AC,phase,peak} = 8.75 \, kV$$

(3-1)

After evaluating the maximum phase current on the AC side by (3-2), the arm current can be represented as in (3-3) [21]:

$$\frac{3}{2} V_{AC,phase,peak} I_{AC,phase,peak} = V_{DC} I_{DC}$$

(3-2)

$$I_{arm}(t) = \frac{I_{DC}}{3} \pm \frac{I_{AC,phase,peak}}{2} \cos(\omega t)$$

(3-3)

Considering the DC current of  $I_{DC,max,c}$ , the maximum value for the peak arm current is evaluated as follows:

$$I_{(AC,phase,peak)max} = 1.52 kA$$

$$I_{(arm,peak)max} = \frac{I_{DC,max,c}}{3} + \frac{I_{(AC,phase,peak)max}}{2} = 1.03 kA$$

(3-4)

To consider the transients and the effect of the displacement factor, it is recommended to select an IGBT-diode module with a collector current rating of at least 1.3 kA. Alternatively, the submodules can be realised by four groups of parallel IGBT-diode modules with lower current ratings.

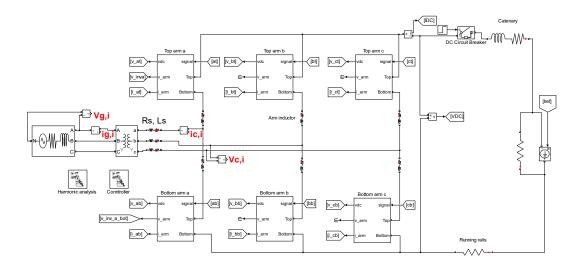

Figure 3.4 represents the TPS model developed in Matlab/Simulink using the Simscape library. To rectify some issues with the transformer block, the transformer impedance is modelled by setting the impedance parameters of the transformer block (0.002 pu), together with external resistance and inductances on the secondary side ( $R_s$  and  $X_s$ , 0.998 pu).

In some simulation cases, the trains' load is modelled by a controlled current source, where the current profile corresponds to a power profile at a fixed DC voltage of 25 kV. In the rest of simulations, the load is applied by a constant resistor corresponding to a specific power level at 25 kV DC. In the next chapter and for each simulation case, the load type is indicated.

Figure 3.4 - The MVDC TPS modelled in Matlab/Simulink

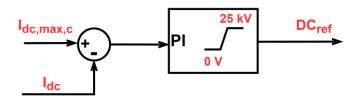

#### 3.3.2 Control scheme

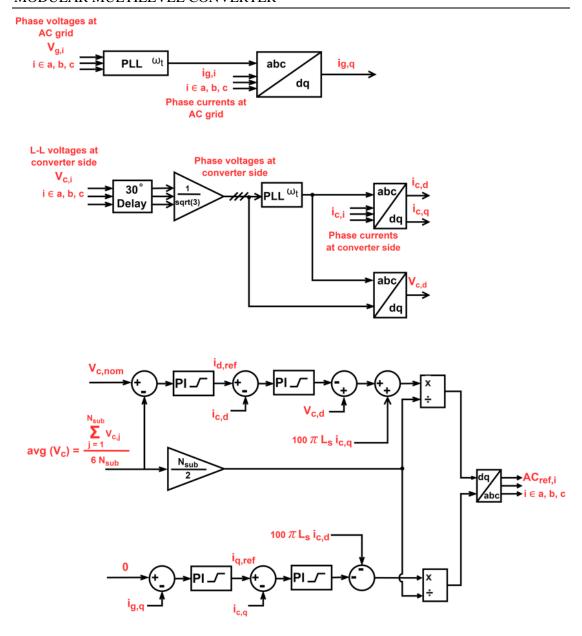

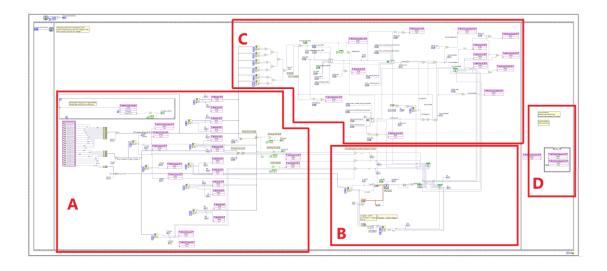

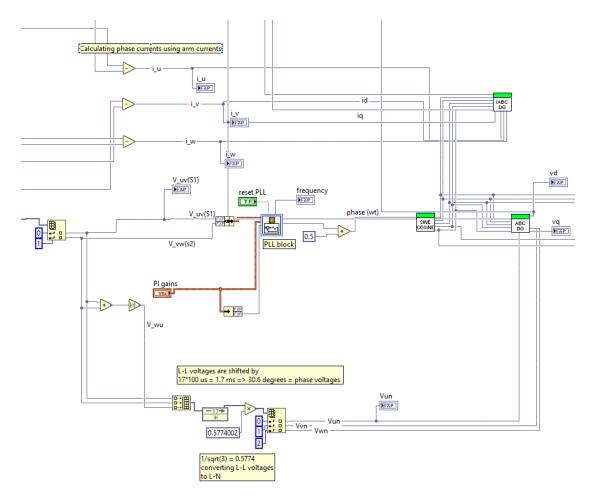

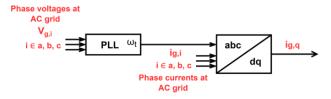

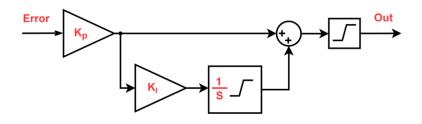

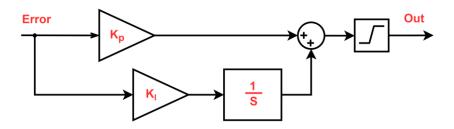

The proposed control scheme for the MMC-FB is designed in a direct-quadrature (dq) frame. The principle of the control scheme is similar to that of grid-connected two-level converters in the dq frame [22]. However, the outer control loop in the d axis is designed differently. Figure 3.5 shows the implemented MMC-FB controller, which mainly consists of outer and inner control loops. The overall schematic of the control system and the Proportional–Integral (PI) controller gains used in the MVDC TPS simulations are presented in Appendix B.

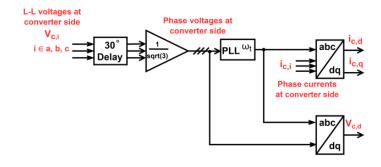

Figure 3.5 - The proposed controller for the MMC-FB

On the AC grid side, the measured phase voltages are passed to a Phase-Locked-Loop (PLL) block to determine the phase angle  $\omega_t$ . This phase angle is then used to calculate the quadrature component of the AC grid currents  $(i_{g,q})$ . Similarly, line-to-line voltages on the transformer's secondary (converter) side are measured to evaluate direct and quadrature components of the converter currents  $(i_{c,d})$  and direct component of the converter-side voltage  $(v_{c,d})$ .

The outer control loop in the d axis is responsible for maintaining the average of the capacitor voltages to the reference value ( $\frac{V_{DC,nom,c}}{N_{sub}} = \frac{25 \text{ kV}}{8} = 3.13 \text{ kV}$ ). In fact, this control loop provides the reference for  $i_{c,d}$  to control the active power transfer to/from the converter capacitors. The outer control loop in the q axis regulates the reactive power consumption on the primary side of the transformer (grid side) to a setpoint, by producing a reference for  $i_{c,q}$ . Based on the AC network requirements, the setpoint for the reactive power can be changed during the TPS operation. In this study, the setpoint is zero in all the simulation cases.

The aim of inner control loops is to keep the measured  $i_{d,c}$  and  $i_{q,c}$  to their reference values. After applying cross-coupling terms between d and q axes, the control signals are divided by  $\frac{N_{sub}}{2} \times avg$  ( $V_c$ ), where avg ( $V_c$ ) refers to the average of the capacitor voltages. This operation is necessary to form the amplitude of the control signals and make them appropriate for the modulation stage. In other words, after transforming the control signals from the dq to abc frame, the resultant control signals for the phases 'a', 'b' and 'c' are sinusoidal-like waveforms ( $AC_{ref,i}$ ,  $i \in a,b,c$ ). For modulation indices less than 1, the  $AC_{ref,i}$  signals should lie between -1 and 1.

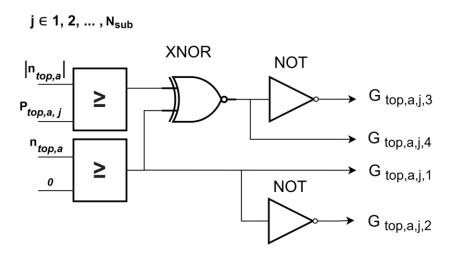

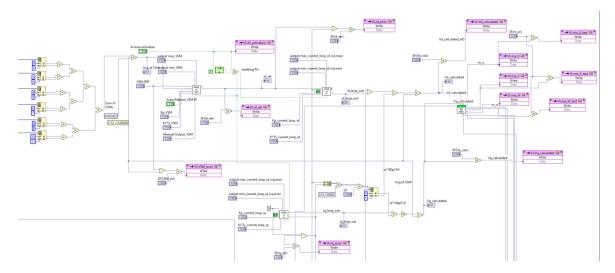

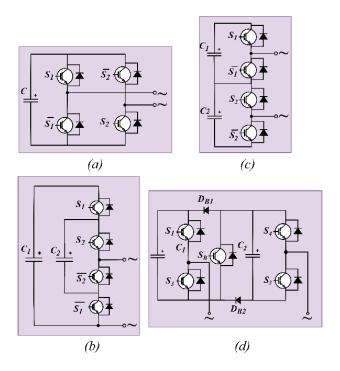

#### 3.3.3 Modulation and sorting scheme

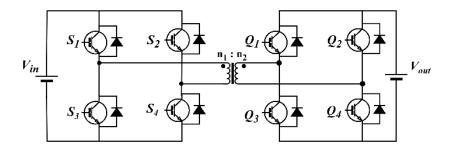

In [23], a level-shifted carrier modulation scheme has been described for the MMCs with half-bridge submodules. In this PhD thesis, the mentioned scheme is extended for the MMC with full-bridge submodules. In this way, the proposed modulation unit can be used for the MMC-FBs in the MVDC TPSs. This aim is achieved by designing proper logic for driving four IGBTs (instead of two) and inserting submodules with

both positive and negative output voltages. In addition, the output of the modulation scheme is reformulated, so that the DC-side voltage is controlled by a DC reference.

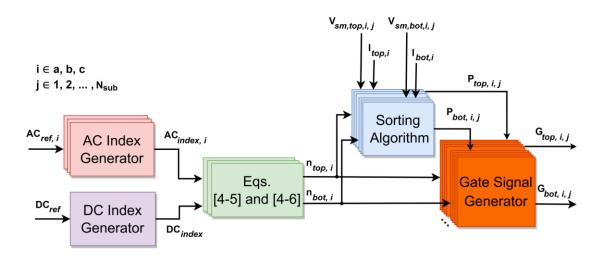

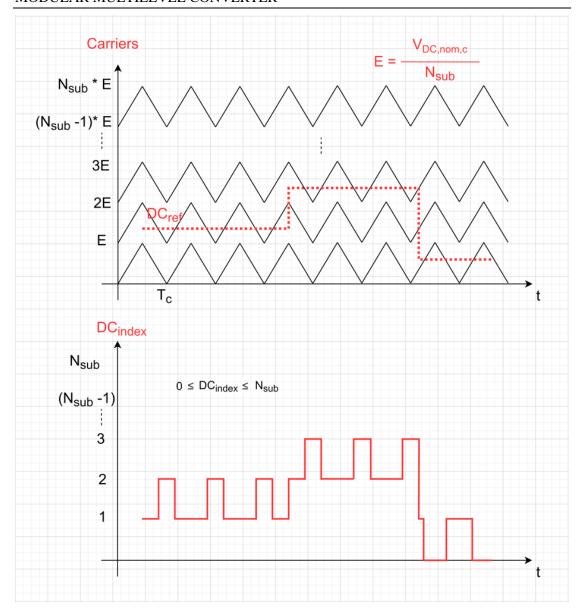

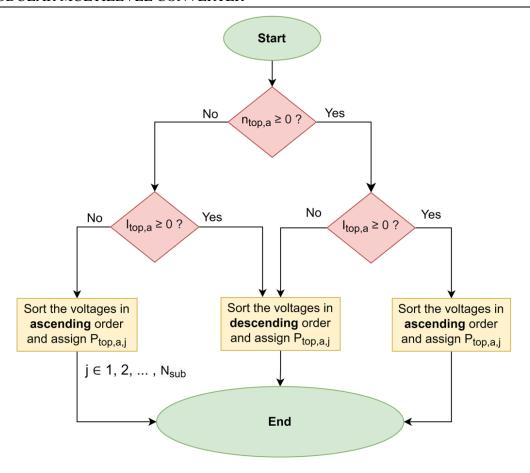

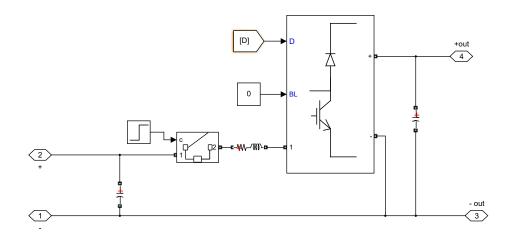

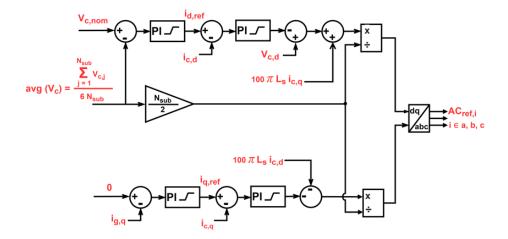

Figure 3.6 illustrates the block diagram of the designed modulation and sorting scheme. In the DC index generator block and as shown in Figure 3.7, a reference for the DC voltage is compared with  $N_{sub}$  level-shifted carriers and a DC index ( $DC_{index}$ ) is produced. Using negative carriers, and thus, negative DC indices, this arrangement can also be used for producing negative DC voltages. Nevertheless, the voltage polarity does not change in the MVDC railway electrification system and only positive carriers are implemented in this study.

Figure 3.6 - Block diagram of the modulation and sorting scheme used for the MMC-FB

Figure 3.7 - The DC index generator block

In all the simulation cases, the carrier frequency ( $f_c$ ) is 3 kHz. Except for the simulation cases related to the DC short-circuit current controller, the reference for the DC voltage is  $V_{DC,nom,c} = 25$  kV DC, which corresponds to a  $DC_{index}$  of 8.

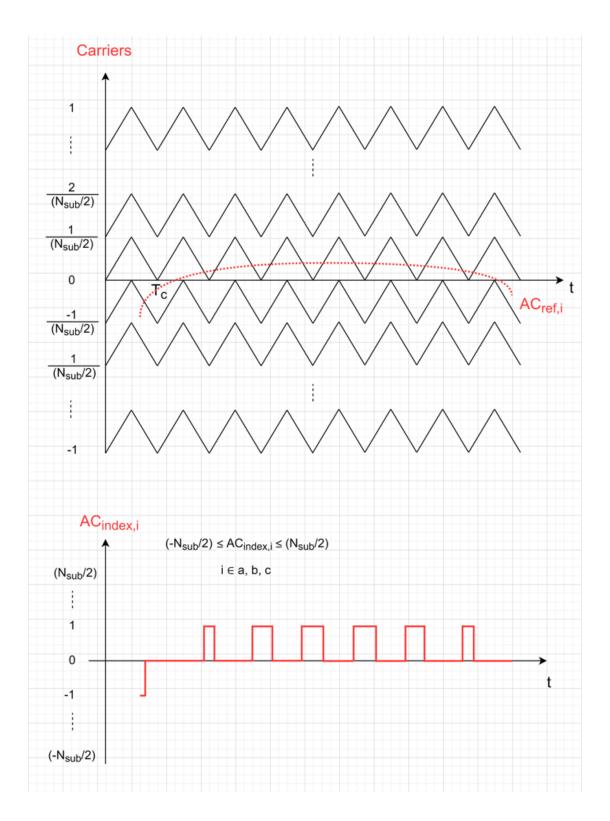

Similarly, the output of the controller for each phase  $(AC_{ref,i}, i \in a, b, c)$  is compared with  $N_{sub}$  level-shifted carriers in the AC index generator blocks. Figure 3.8 shows the logic implemented in these blocks.

Figure 3.8 - The AC index generator block

# MODELLING THE PROPOSED MVDC ELECTRIC RAILWAY SYSTEM AND MODULAR MULTILEVEL CONVERTER

The resultant AC index for each phase  $(AC_{index,i}, i \in a, b, c)$  is then utilised to evaluate the number of submodules which should be inserted in each arm circuit  $(n_{top,i})$  and  $n_{bot,i}$ ,  $i \in a,b,c$ :

$$n_{bot,i} = floor \left(0.5 \left(DC_{index} + 2AC_{index,i} + 1\right)\right) - N_{sub} \le n_{bot,i} \le N_{sub}$$

(3-5)

$$n_{top,i} = DC_{index} - n_{bot,i} \qquad -N_{sub} \le n_{top,i} \le N_{sub}$$

(3-6)

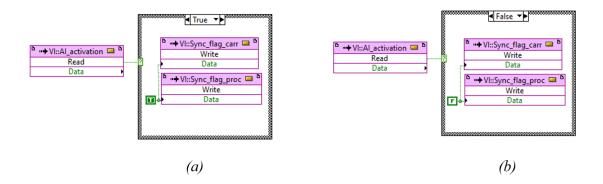

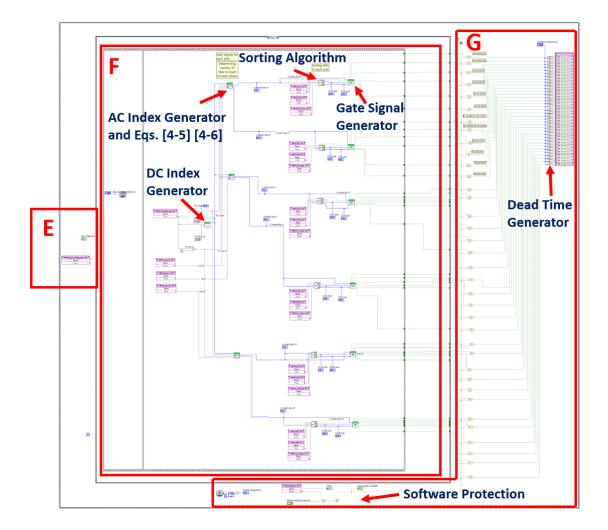

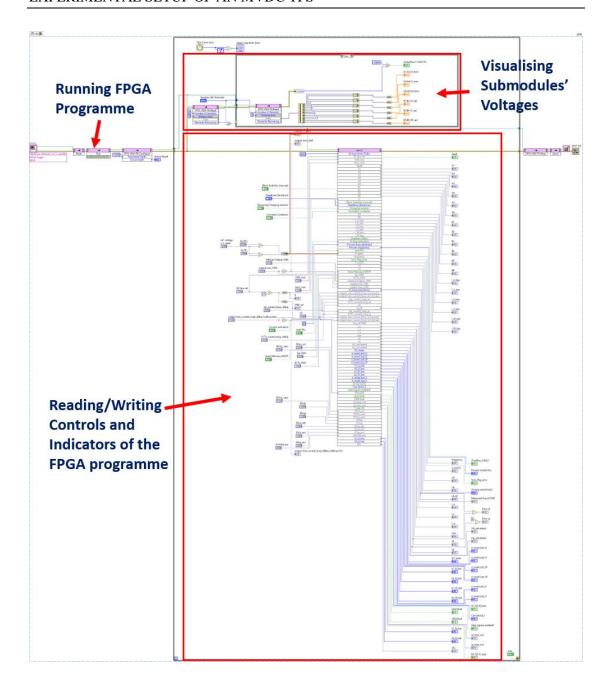

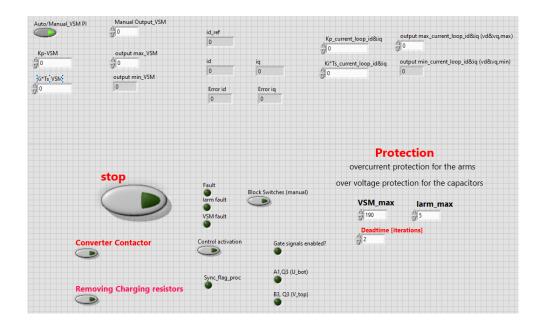

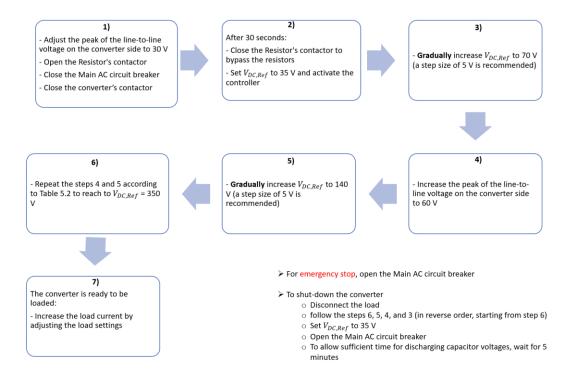

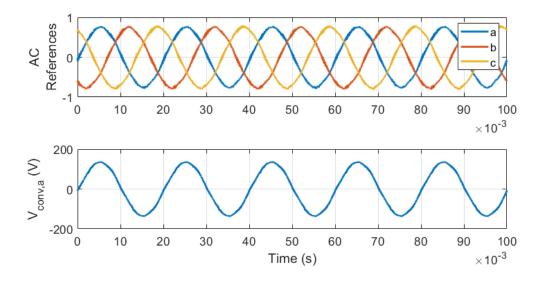

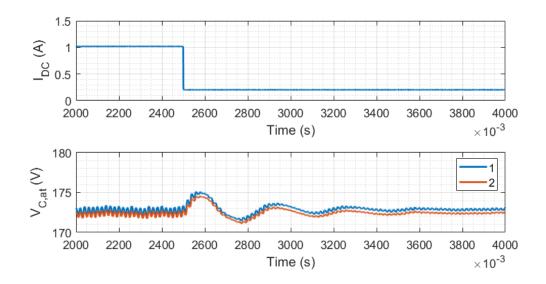

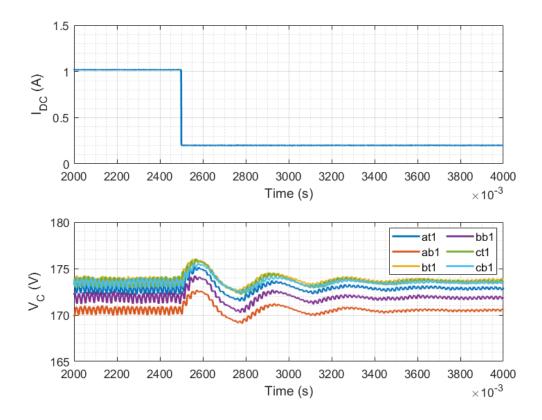

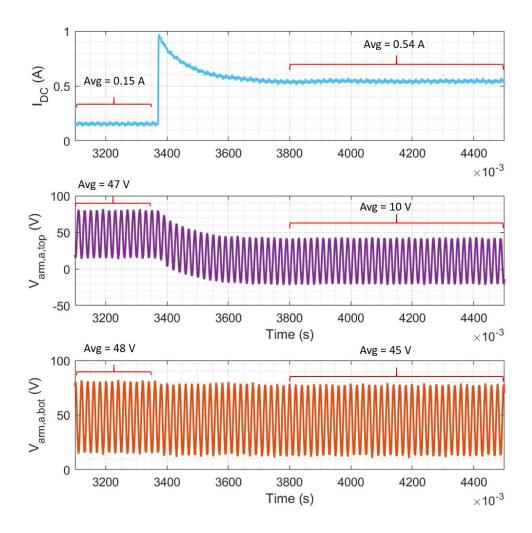

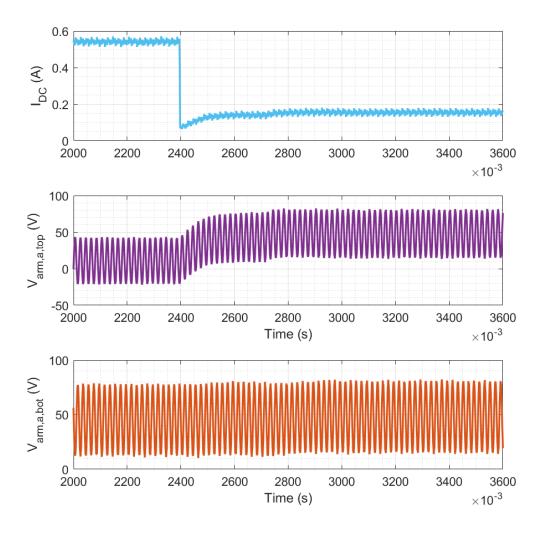

The negative values for  $n_{top,i}$  and  $n_{bot,i}$  indicate that the submodules need to be inserted with a negative voltage. The derivation of the above formula is presented in Appendix C.