# AUTOMOTIVE FIRMWARE EXTRACTION AND ANALYSIS TECHNIQUES

by

Jan Van den Herrewegen

A thesis submitted to The University of Birmingham for the degree of DOCTOR OF PHILOSOPHY

> School of Computer Science College of Engineering and Physical Sciences The University of Birmingham March 2021

# UNIVERSITY<sup>OF</sup> BIRMINGHAM

# **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

#### Abstract

An intricate network of embedded devices, called Electronic Control Units (ECUs), is responsible for the functionality of a modern vehicle. Every module processes a myriad of information and forwards it on to other nodes on the network, typically an automotive bus such as the Controller Area Network (CAN). Analysing embedded device software, and automotive in particular, brings many challenges.

The analyst must, especially in the notoriously secretive automotive industry, first lift the ECU firmware from the hardware, which typically prevents unauthorised access. In this thesis, we address this problem in two ways: (i) We detail and bypass the access control mechanism used in diagnostic protocols in ECU firmware. Using existing diagnostic functionality, we present a generic technique to download code to RAM and execute it, without requiring physical access to the ECU. We propose a generic firmware readout framework on top of this, which only requires access to the CAN bus. (ii) We analyse various embedded bootloaders and combine dynamic analysis with low-level hardware fault attacks, resulting in several fault-injection attacks which bypass on-chip readout protection.

We then apply these firmware extraction techniques to acquire immobiliser firmware by two different manufacturers, from which we reverse engineer the DST80 cipher and present it in full detail here. Furthermore, we point out flaws in the key generation procedure, also recovered from the ECU firmware, leading to a full key recovery based on publicly readable transponder pages.

# ACKNOWLEDGEMENTS

As Margaret Hungerford expressed eloquently, beauty lies in the eyes of the beholder. So, first and foremost, I would like to thank you, the reader, for taking the time out of your busy life to pick up this thesis and, however briefly or thoroughly, read (part of) it.

Along the way I have had the privilege to meet and work with many exceptional people. First of all, I would like to thank my supervisor turned friend, Flavio Garcia, without whom I would have never started a PhD, let alone finish it. Thank you for the many interesting discussions, coffee breaks and most of all the occasional life advice. Equally, my gratitude goes out to my co-supervisor David Oswald, who always had an answer to my (at times naive) questions and never failed to provide me with a new insight to tackle problems.

I extend my gratitude to my examiners, Tom Chothia and Colin O'Flynn, who kindly gave up their valuable time to read and assess this thesis.

To my office mates and friends throughout the department, Andreea, Kit, Chris, Sam and Richard - thank you for the (at times too) pleasant work environment. To my new family and friends in what they would refer to as 'gods country' Franz, Emilio, Charlie, Fred, the Jacks and Sams, and to my friends back home, Luigi, Seba, Martino, Pedro, Florrie - thank you for keeping me sane and bringing some perspective to the long and at times arduous PhD journey. To my coaches, Rob, Jon and Burnsy, thank you for all your advice and patience.

Finally, I would like to thank my family for their unconditional support. Inge and Tim for putting up with their little brother and teaching me the ways of life. And my parents, Lut and Piet, for being so supportive of any decision I take, be it in sport, studies or life.

# CONTENTS

| 1        | Intr | oducti | ion                                                         | 1  |

|----------|------|--------|-------------------------------------------------------------|----|

|          | 1.1  | Contr  | ibutions                                                    | 4  |

|          |      | 1.1.1  | Breaking Diagnostics: Firmware Extraction over CAN          | 4  |

|          |      | 1.1.2  | Obtaining Firmware through Enhanced Embedded Bootloader Ex- |    |

|          |      |        | ploits                                                      | 5  |

|          |      | 1.1.3  | Security Analysis of DST80 Immobiliser ECUs                 | 5  |

| Ι        | Ba   | ckgro  | ound & Related Work                                         | 7  |

| <b>2</b> | Bac  | kgroui | nd                                                          | 8  |

|          | 2.1  | Auton  | notive Protocol Stack                                       | 8  |

|          |      | 2.1.1  | Physical & Data-Link Layer                                  | 9  |

|          |      | 2.1.2  | Transport & Network Layer                                   | 10 |

|          |      | 2.1.3  | Application Layer                                           | 12 |

|          | 2.2  | Auton  | notive Supply Chain                                         | 14 |

|          | 2.3  | Acqui  | ring Automotive Firmware                                    | 15 |

|          |      | 2.3.1  | Non-intrusive Firmware Acquisition                          | 16 |

|          |      | 2.3.2  | Hardware-based Extraction                                   | 16 |

|          |      | 2.3.3  | Fault Injection                                             | 18 |

|          | 2.4  | Vehicl | e Theft Prevention                                          | 19 |

|          |      | 2.4.1  | Immobiliser System                                          | 20 |

|          |      | 2.4.2  | DST80 Transponders                                          | 21 |

|    | 2.5          | Firmw   | rare Analysis Techniques                       | 22 |

|----|--------------|---------|------------------------------------------------|----|

|    |              | 2.5.1   | Reverse Engineering Embedded Firmware          | 23 |

|    | 2.6          | Notati  | on and Variables                               | 26 |

| 3  | Rela         | ated W  | Vork                                           | 28 |

|    | 3.1          | Auton   | notive Network and Component Security          | 29 |

|    |              | 3.1.1   | Automotive Networks                            | 29 |

|    |              | 3.1.2   | ECU Security                                   | 31 |

|    | 3.2          | Immol   | oiliser and Keyless Entry Security             | 38 |

|    |              | 3.2.1   | Immobiliser Security                           | 39 |

|    |              | 3.2.2   | Keyless Entry Security                         | 42 |

|    | 3.3          | CRP l   | oypass techniques                              | 45 |

|    |              | 3.3.1   | Fault-Injection Techniques                     | 45 |

|    |              | 3.3.2   | Hardware-based CRP bypass                      | 51 |

|    |              | 3.3.3   | Software-based CRP bypass                      | 53 |

|    | 3.4          | Embed   | dded Device Analysis                           | 54 |

|    |              | 3.4.1   | Dynamic Analyis Techniques                     | 54 |

|    |              | 3.4.2   | Static Analysis                                | 58 |

|    |              |         |                                                |    |

| II | $\mathbf{E}$ | CU F    | irmware Extraction and Analysis                | 60 |

| 4  | Bre          | aking [ | Diagnostics: Firmware Extraction over CAN      | 61 |

|    | 4.1          | Motiva  | ation                                          | 62 |

|    | 4.2          | Contri  | butions                                        | 62 |

|    | 4.3          | Crypta  | analysis of diagnostic protocols               | 63 |

|    |              | 4.3.1   | Obtaining and analysing ECU firmware images    | 63 |

|    |              | 4.3.2   | Analysis of the Ford challenge-response cipher | 64 |

|    |              | 4.3.3   | Analysis of the Fiat challenge-response cipher | 67 |

|    |              | 4.3.4   | Analysis of the Volkswagen Group cipher        | 69 |

|   | 4.4 | Remot  | se code execution over CAN                                          | 71  |

|---|-----|--------|---------------------------------------------------------------------|-----|

|   |     | 4.4.1  | Use case: changing the odometer on a Ford Instrument Cluster        | 74  |

|   |     | 4.4.2  | Use case: reprogramming a Fiat Body System Interface                | 75  |

|   | 4.5 | Buildi | ng a firmware modification and extraction framework                 | 77  |

|   | 4.6 | Mitiga | tion                                                                | 79  |

|   | 4.7 | Discus | sion                                                                | 80  |

|   | 4.8 | Chapt  | er Summary                                                          | 81  |

| 5 | Obt | aining | Firmware through Enhanced Embedded Bootloader Exploits              | 83  |

|   | 5.1 | Motiva | ation                                                               | 84  |

|   | 5.2 | Contri | butions                                                             | 86  |

|   | 5.3 | Secure | Bootloader Design Directives                                        | 88  |

|   | 5.4 | Findin | g software vulnerabilities through static and dynamic analysis: NXP |     |

|   |     | LPC1x  | xxx bootloader                                                      | 91  |

|   |     | 5.4.1  | Analysis of the LPC1xxx Bootloader                                  | 92  |

|   |     | 5.4.2  | CRP 1 Bypass with Stack Overwrite                                   | 94  |

|   |     | 5.4.3  | CRP 1 Bypass with Partial Flash Overwrite                           | 96  |

|   |     | 5.4.4  | Discussion                                                          | 97  |

|   | 5.5 | Glitch | ing guided by dynamic analysis: The STM8 bootloader                 | 97  |

|   |     | 5.5.1  | Bootloader Extraction and Analysis                                  | 99  |

|   |     | 5.5.2  | Profiling Critical Bootloader Sections                              | 99  |

|   |     | 5.5.3  | Partially Attacking the Bootloader on Reset                         | 102 |

|   |     | 5.5.4  | Full Double-Glitch Attack                                           | 105 |

|   | 5.6 | Glitch | ing guided by static analysis: Renesas 78K0 bootloader              | 106 |

|   |     | 5.6.1  | 78K0 Bootloader Extraction and Analysis                             | 106 |

|   |     | 5.6.2  | Constraint-based Glitching                                          | 108 |

|   |     | 5.6.3  | Exploitation and Evaluation                                         | 111 |

|   | 5.7 | Dynan  | nic vs Static Approach                                              | 115 |

|   | 5.8 | Chapt  | er Summary                                                          | 117 |

| 6                         | Sec                                                               | urity Analysis of DST80 immobiliser ECUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 118   |  |  |

|---------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|

|                           | 6.1                                                               | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 119   |  |  |

|                           | 6.2                                                               | Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120   |  |  |

|                           | 6.3                                                               | The DST80 Cipher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 121   |  |  |

|                           |                                                                   | 6.3.1 Reading out immobiliser firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 121   |  |  |

|                           |                                                                   | 6.3.2 Reverse engineering the cipher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 123   |  |  |

|                           |                                                                   | 6.3.3 Cipher details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 124   |  |  |

|                           | 6.4                                                               | Practical attacks on DST80 systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125   |  |  |

|                           |                                                                   | 6.4.1 Uncovering key diversification schemes from immobiliser firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 126 |  |  |

|                           | 6.5                                                               | Transponder configuration issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 129   |  |  |

|                           | 6.6                                                               | Discussion and mitigation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 133   |  |  |

|                           | 6.7                                                               | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 134   |  |  |

|                           |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |

| ΙΙ                        | III Closing Statements 136                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |

| 7                         | 7 Closing Remarks 137                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |

|                           | 7.1 Conclusion                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |

| $\mathbf{A}_{\mathbf{J}}$ | ppen                                                              | ${ m dix}\;{f A} {:}\; { m Full}\; { m assembly}\; { m of}\; { m the}\; { m {\tt get\_block\_no}}\; { m and}\; { m {\tt cmp\_addr}}\; { m functions}\; { m from}\; { m constant}\; { m const$ | om    |  |  |

|                           | the 78K0 bootloader 139                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |

| Aj                        | Appendix B: Example path through the checksum command handler 142 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |  |  |

| Aj                        | ppen                                                              | dix C: Specification of the DST80 Feistel function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 146   |  |  |

| Li                        | $\mathbf{st}$ of                                                  | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 149   |  |  |

# LIST OF FIGURES

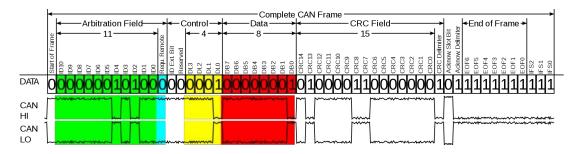

| 2.1 | Structure and signals of a Controller Area Network (CAN) frame              | 9  |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | A typical On-Board Diagnostics (OBD-II) port and a simple diagnostic        |    |

|     | device purposed to connect to it                                            | 10 |

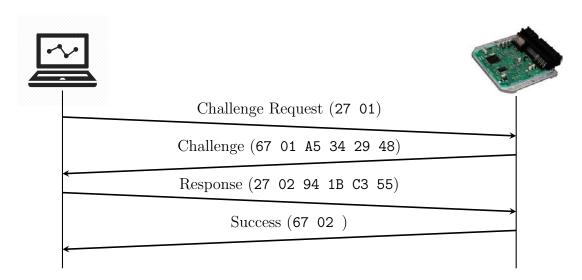

| 2.3 | The challenge-response protocol specified by UDS                            | 13 |

| 2.4 | A Joint Test Action Group (JTAG) interface on a Ford Body Control Mod-      |    |

|     | ule (BCM) incorporating a SPC560B microcontroller                           | 17 |

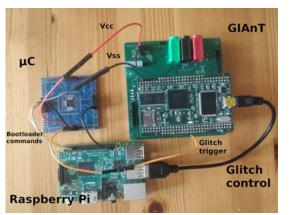

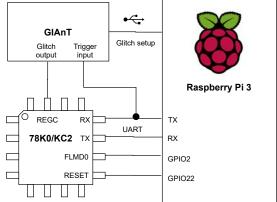

| 2.5 | Our hardware setup for the voltage glitching attacks described throughout   |    |

|     | this Thesis.                                                                | 19 |

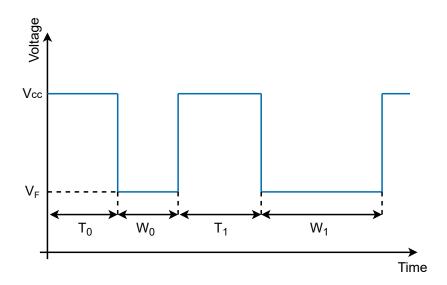

| 2.6 | Parameter conventions for voltage glitches                                  | 20 |

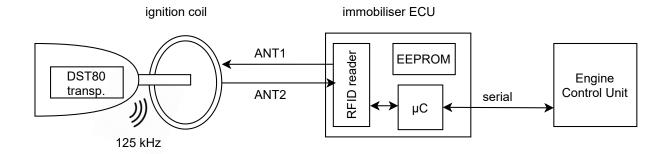

| 2.7 | A typical immobiliser system                                                | 21 |

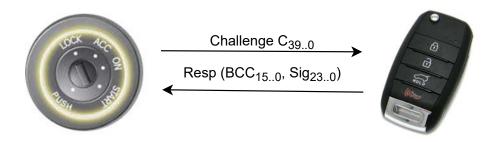

| 2.8 | The Digital Signature Transponder (DST) authentication protocol             | 22 |

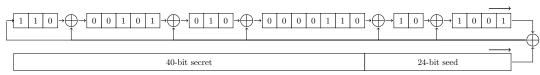

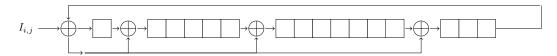

| 4.1 | Initial state and structure of the Ford LFSR used in the challenge response |    |

|     | authentication.                                                             | 65 |

| 4.2 | Structure of the LFSR used in the diagnostic access control mechanism in    |    |

|     | Fiat Electronic Control Units (ECUs)                                        | 68 |

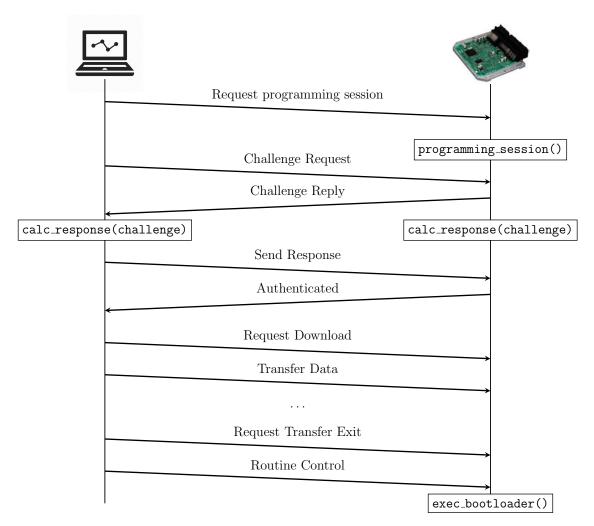

| 4.3 | Download and execution process of the secondary bootloader from a diag-     |    |

|     | nostic client to an ECU                                                     | 73 |

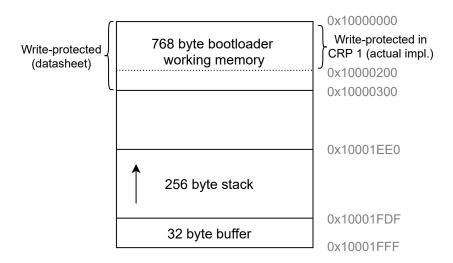

| 5.1 | RAM memory layout of the LPC1343 bootloader, indicating write-protected     |    |

|     | memory areas according to actual implementation and datasheet               | 93 |

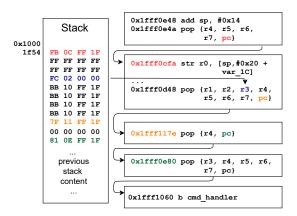

| 5.2 | Return-Oriented Programming (ROP) chain for bypassing readout protec-                       |       |

|-----|---------------------------------------------------------------------------------------------|-------|

|     | tion of LPC bootloader and reading 900 byte from any start address (here:                   |       |

|     | Ox2fc). The exploit is applied by invoking the "Write to RAM" command                       |       |

|     | as: W 268443476 172                                                                         | . 96  |

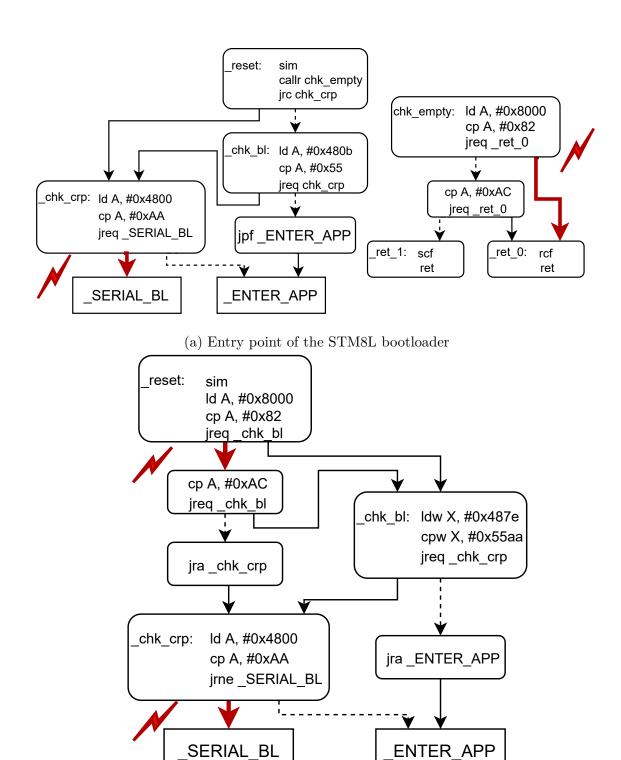

| 5.3 | Control flow diagrams of the STM8L and STM8A bootloaders. Jumps                             |       |

|     | are displayed with a full line, whereas a dotted line implies a fallthrough                 |       |

|     | path. Glitch paths for each Microcontroller ( $\mu \mathrm{C}$ ) with first flash byte $82$ |       |

|     | are indicated in red.                                                                       | . 100 |

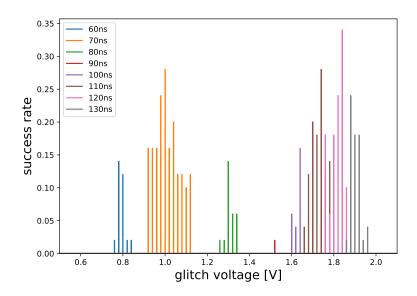

| 5.4 | Success rate for glitching the _enter_app bootloader section (which imme-                   |       |

|     | diately precedes the serial bootloader) on the STM8A at a constant offset                   |       |

|     | of 0.34 μs                                                                                  | . 103 |

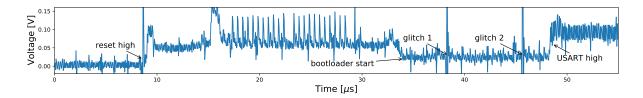

| 5.5 | Power consumption of the STM8L152 upon reset measured with a $30\Omega$                     |       |

|     | shunt resistor.                                                                             | . 105 |

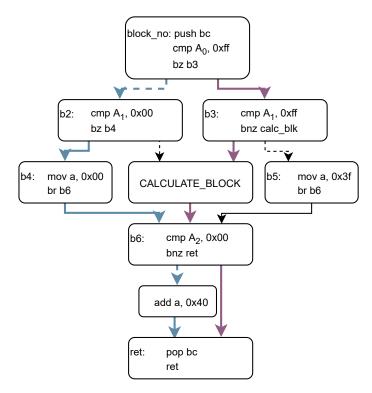

| 5.6 | Simplified control flow graph of the get_block_no function, which takes                     |       |

|     | as input a 3 byte address $A = A_2 A_1 A_0$ . To illustrate, we depict example              |       |

|     | execution paths for the equivalence classes of $0x1004c$ and $0x5ff$                        | . 112 |

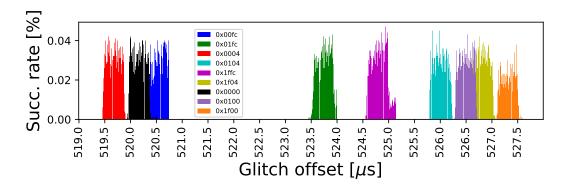

| 5.7 | Glitch success rate and offset of the checksum command for the first ad-                    |       |

|     | dress of each equivalence set. Glitch triggered on falling edge of the Serial               |       |

|     | Peripheral Interface (SPI) clock pin on a 78<br>K0/KC2 $\upmu{\rm C}$ powered at 3 V        |       |

|     | clocked by $8\mathrm{MHz}$ internal oscillator. Glitch voltage and width constant at        |       |

|     | 0 V and 120 ns, respectively.                                                               | . 113 |

# LIST OF TABLES

| 2.1 | Non-exhaustive list of common automotive chips and their debug interfaces.                                                       | 18  |

|-----|----------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | DST80 transponder memory layout                                                                                                  | 22  |

| 4.1 | ECUs on which we examined and identified the Ford cipher                                                                         | 65  |

| 4.2 | Secrets found in the firmware of two different Fiat ECUs                                                                         | 69  |

| 4.3 | ECUs on which we implemented the firmware extraction framework $\dots$ .                                                         | 78  |

| 5.1 | Glitch success rate and their offsets triggered on reset of the critical boot-                                                   |     |

|     | loader sections of the STM8L. Glitch voltage and width kept constant at                                                          |     |

|     | $V_F = 1.84 \mathrm{V}$ and $W = 50 \mathrm{ns}$                                                                                 | 104 |

| 5.2 | Glitch parameters for fully locked STM8 chips with first flash byte 82                                                           |     |

|     | triggered on reset                                                                                                               | 106 |

| 5.3 | Comparison of predicted number of cycles and actual glitch offset (first                                                         |     |

|     | offset with a glitch success rate above $3\%$ ) for each equivalence class for                                                   |     |

|     | the checksum command. Differences $\left(\frac{\Delta T}{\Delta c} = \frac{T_n - T_0}{c_n - c_0}\right)$ are calculated from the |     |

|     | offset $T_0$ of the first encountered equivalence class, 0004                                                                    | 114 |

| 5.4 | Success rates of different glitch search strategies on checksum and verify                                                       |     |

|     | commands. wvf and pulse use the same genetic algorithm, with the latter                                                          |     |

|     | using a pulse-shaped glitch similar to our hardware, whereas the former                                                          |     |

|     | also optimises the glitch waveform                                                                                               | 114 |

| 5.5 | Overview of the effectiveness of voltage fault-injection techniques in dif-                                                      |     |

|     | ferent scenarios. We include a non-exhaustive list of references for each                                                        |     |

|     | technique                                                                                                                        | 117 |

| 6.1                                                                    | Non-exhaustive list of vehicles affected by the research in this chapter. The                 |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

|                                                                        | indicated production period is based on the information available in [31,                     |  |  |

| 207]. The models in bold point out the specific vehicles we inspected. |                                                                                               |  |  |

| 6.2                                                                    | Kia and Hyundai immobilisers and their respective DST80 keys. The two                         |  |  |

|                                                                        | 2-byte constants ${\tt X}$ and ${\tt Y}$ have been redacted on the manufacturers request. 127 |  |  |

| 6.3                                                                    | Attacks on DST80 transponders described in this chapter. In the scenarios                     |  |  |

|                                                                        | marked by an asterisk lookup tables can be employed to speed up the key                       |  |  |

|                                                                        | recovery process                                                                              |  |  |

| C.1                                                                    | The tables used in the Feistel function F                                                     |  |  |

|                                                                        |                                                                                               |  |  |

| List                                                                   | of Acronyms                                                                                   |  |  |

| BCM                                                                    | Body Control Module                                                                           |  |  |

| BL                                                                     | Bootloader Enable                                                                             |  |  |

| CAN Controller Area Network                                            |                                                                                               |  |  |

| CBS Critical Bootloader Section                                        |                                                                                               |  |  |

| CCP Can Calibration Protocol                                           |                                                                                               |  |  |

| CFG Control-Flow Graph                                                 |                                                                                               |  |  |

| CRP                                                                    | Code Readout Protection                                                                       |  |  |

| $\mathbf{DoS}$                                                         | Denial-of-Service                                                                             |  |  |

| DST                                                                    | Digital Signature Transponder                                                                 |  |  |

| ECU                                                                    | Electronic Control Unit                                                                       |  |  |

| EEPR                                                                   | OM Electrically Erasable Programmable Read-Only Memory                                        |  |  |

| EMFI                                                                   | Electromagnetic Fault Injection                                                               |  |  |

| GIAnT                                                                  | Γ Generic Implementation ANalysis Toolkit                                                     |  |  |

| $\mathbf{HF}$                                                          | F High Frequency                                                                              |  |  |

IC Integrated Circuit

**IDS** Intrusion Detection System

**ISA** Instruction Set Architecutre

**ISO** International Organization for Standardization

**ISO-TP** ISO Transport Layer

JTAG Joint Test Action Group

KWP Keyword Protocol 2000

**LF** Low Frequency

LFSR Linear Feedback Shift Register

LTE Long Term Evolution

MAC Message Authentication Code

MMU Memory Management Unit

μC Microcontroller

**OBD-II** On-Board Diagnostics

**OEM** Original Equipment Manufacturer

**OS** Operating System

PCB Printed Circuit Board

PKE Passive Keyless Entry

PKES Passive Keyless Entry and Start

**POR** Power-On Reset

**RAM** Random Access Memory

**RFID** Radio Frequency IDentification

**RKE** Remote Keyless Entry

**RNG** Random Number Generator

**ROP** Return-Oriented Programming

RTOS Real-Time Operating System

**SPI** Serial Peripheral Interface

SoC System-on-Chip

**SUT** System Under Test

**SWD** Serial-Wire Debug

SWIM Single Wire Interface Module

TCU Telematics Control Unit

TPMS Tire Pressure Monitoring System

TI Texas Instruments

**TP 2.0** Transport Protocol 2.0

**UART** Universal Asynchronous Receiver Transmitter

**UDS** Unified Diagnostic Services

V-FI Voltage-Fault Injection

VAG Volkswagen Auto Group

VIN Vehicle Identification Number

VLE variable length encoded

XCP Universal Measurement and Calibration Protocol

**XOM** eXecute-Only-Memory

OCD On-Chip Debug

## CHAPTER 1

# INTRODUCTION

Vehicles are ubiquitous in modern day life. In 2019, the automotive industry produced a total of 92.8 million vehicles worldwide [59]. Across Great Britain, on average 68% of commuters did so by car in 2019, while 79% of freight was transported by road in 2018, pointing at the widespread use of both passenger vehicles and trucks [52]. With most manufacturers to a greater (e.g., self-driving cars) or lesser (e.g., lane-assist technology) extent moving towards more autonomous vehicles, inevitably the technological aspect of a vehicle will only increase. However, unlike other more transient electronic appliances, such as phones or personal computers, cars are designed to stay in use for decades. Hence, manufacturers must strike a balance between incorporating the newest technologies, while still safeguarding the vehicle's longevity. This also manifests itself in a systems security point of view: the average automobile lasts over a decade [58], which is considered a long time in the fast-moving field of computer security. Over the years, the automotive industry has continuously introduced new safety procedures in order to make their vehicles safer (e.g., the three-point seat belt [218]). However, with a modern vehicle nowadays resembling an electronic appliance more than a purely mechanical one, the industry must now equally focus on securing its fleet from a new type of adversary, the connected attacker.

A host of interconnected ECUs determines a vehicle's capabilities, each of these embedded automotive computers with their own interfaces and peculiarities. Millions of lines of code [35] interact seamlessly and hide the vast complexity of a modern automobile. What used to be a closed, purely mechanical system is now a metropolis of interacting embedded devices, inevitably raising security concerns. With connected components (e.g., Bluetooth, 4G, WiFi) now an integral part of the automotive ecosystem, the internal vehicular network can no longer be treated as a closed system. This brings along security implications not only for ECUs connected to the outside world, but for all other ECUs inside the car. After all, if an external attacker compromises any remote component they can create a bridge to the internal vehicular network (see e.g., [36, 126]). On top of that, the most prevalent automotive bus, CAN, is unencrypted and unauthenticated. This makes an adversary with access to the internal network even more powerful. Namely, ECUs expose a diagnostic interface which provides an external device connected over the CAN bus with powerful functionality such as read and write access to the internal memory. Both Keyword Protocol 2000 (KWP) [3] and its successor Unified Diagnostic Services (UDS) [2] standardise this diagnostic interface, and specify a security protocol to prevent unauthorised access to security sensitive functionality. However, the standards leave the choice of the cipher and key size up to the manufacturer. An adequate choice for this cipher is crucial for sufficiently securing this powerful interface.

Historically, the automotive industry has relied on proprietary cryptography to secure the critical parts of the network. Unsurprisingly, it has experienced a myriad of attacks on these proprietary cryptographic primitives (see e.g., [22, 70, 125]). For instance, manufacturers have a track record of using insecure, proprietary ciphers in immobiliser systems, the main theft-deterrent system in a car, since 2004. The immobiliser prevents so-called hot-wiring of a vehicle by cryptographically authenticating the transponder embedded in the keyfob. These flaws, typically exploitable with cheap, off-the-shelf equipment, stand in stark contrast with the often large purchase and upkeep cost of a vehicle. Manufacturers constantly migrate to newer, more secure ciphers with bigger internal states and key sizes. However, the transponder configuration and key derivation scheme used equally contribute to the security of the system. One weak link compromises the whole system

and allows an attacker to bypass the immobiliser.