# **CRYOGENIC CHARACTERISTICS OF IGBTs**

by

SHAOYONG YANG

A thesis submitted to

The University of Birmingham

for the degree of

DOCTOR OF PHILOSOPHY

Electronic, Electrical and Computer Engineering School of Engineering The University of Birmingham July 2005

# UNIVERSITY<sup>OF</sup> BIRMINGHAM

# **University of Birmingham Research Archive**

## e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

#### **Abstract**

Applications are now starting to emerge for superconducting devices in the areas of electrical power conversion and management, for example superconducting windings for marine propulsion motors, superconducting fault current limiters and superconducting magnet energy storage (SMES). Many of these applications also require power electronics, and it is therefore timely to consider the possibility of locating the power electronics in the cryosystem with the superconducting devices. Although significant work has been undertaken on the cryogenic operation of small devices, little has been published on larger devices, particularly the IGBT. This therefore forms the focus of this study.

To examine the cryogenic performance of the sample devices, a cryo-system consisting of a cold chamber, a helium-filled compressor and vacuum pumps was built. Static, gate charge and switching tests were carried out on three types of IGBT modules, PT (punch-through), NPT (non-punch-through) and IGBT3 respectively, in the temperature range of 50 to 300 K. The switching tests were undertaken at 600V and up to 110 A.

A physically based, compact level-1 model was selected to model the cryogenic performance of the IGBTs. A generic Saber power diode model with reverse recovery was selected to model the diode cryogenic performance. Close correspondence was demonstrated between the models and experimental results over the temperature range of 50- 300 K.

Saber simulation was used to examine the cryogenic performance of a DC-DC step-down converter and a pulse-width modulated inverter leg, in which the temperature-dependent power device models developed in the modelling work were used. The simulation results

showed that standard power electronic circuits using standard devices could work much more efficiently at low temperatures, for example, the efficiency of the DC-DC converter working at 50 kHz being increased from 90.0% at room temperature to 97.0% at 50 K.

Dedicated to Ruohui Yang and my parents!

### Acknowledgement

I am indebted, beyond words in any language, to the staff of the Department of Electronic and Electrical Engineering at the University of Birmingham: especially to my supervisor, Professor Andrew J Forsyth for his help on my work and life throughout my PhD.

I would like to acknowledge the great help and support from Phil Mawby and Petar Igic at Swansea University for their generous loan of a curve tracer and valuable advice on the modelling work.

I would like to thank EPSRC for their help towards the funding of this project and in particular D. G. Wong for his help and concern.

I am deeply appreciative of the efficient help that I received from Bill Findlay and Kev Birkett at Dynex Semiconductor, and Colin Oates at Areva T&D.

I am very grateful to Stefan Mollov, Paul Weston and Andy Cross for their valuable suggestions and encouragement.

I would like to say thanks to Andy Dunn, Ade Zentani and other technical staff for their great support.

I would like to thank Tao Chang, Jiehua Chen, Michael Theodoridis, Javier Chivite-zabalza, Alfred Baghramian, Chaobo Dai, Chunjiang Jia, Xinyun Liu and other friends in my office.

I would like to record special thanks to my housemates, especially Adam Robertson and Terry Gawtrey for their heart-warming personal help.

Finally, I would like to show my respect to my friends in my homeland, China, especially Zongbin Yue and Zhenwei Ma for their great help and friendship.

# **Contents**

| List of Figures and Tables                                                 | IX       |

|----------------------------------------------------------------------------|----------|

| List of Abbreviations and Symbols.                                         |          |

|                                                                            |          |

| Chapter 1 Introduction and literature review                               | 1        |

| 1. 1 Introduction                                                          |          |

| 1. 2 Cryogenic power applications                                          | 1        |

| 1. 2. 1 Magnetic resonance imaging (MRI)                                   | 2        |

| 1. 2. 2 Rotating machinery                                                 |          |

| 1. 2. 3 High voltage transmission cables                                   |          |

| 1. 2. 4 Superconducting Magnet Energy Storage (SMES)                       |          |

| 1. 2. 5 Power transformers                                                 |          |

| 1. 2. 6 Fault current limiters                                             |          |

| 1. 2. 7 Space power applications                                           | 7        |

| 1. 2. 8 Summary of cryogenic power applications                            |          |

| 1. 3 Review of cryogenic semiconductor physics                             |          |

| 1. 4 Review of cryogenic power electronics                                 |          |

| 1. 4. 1 PiN diode cryogenic characteristics                                |          |

| 1. 4. 2 Power bipolar junction transistor (BJT) cryogenic characteristics  |          |

| 1. 4. 3 Power MOSFET cryogenic characteristics                             |          |

| 1. 4. 4 Power IGBT cryogenic characteristics                               |          |

| 1. 4. 5 Germanium devices                                                  |          |

| 1. 4. 6 Cryogenic power converters                                         |          |

| 1. 4. 7 Summary of cryogenic power electronics                             |          |

| 1. 5 Summary of literature review                                          |          |

| 1. 6 Scope of the thesis                                                   |          |

| References                                                                 |          |

|                                                                            |          |

| Chapter 2 Basic characteristics of the PiN diode and IGBT                  | 30       |

| 2. 1 Introduction                                                          |          |

| 2. 2 PiN power diode                                                       |          |

| 2. 2. 1 Basic structure                                                    |          |

| 2. 2. 2 Static characteristics.                                            |          |

| 2. 2 .3 Switching characteristics                                          |          |

| 2. 2. 4 Trade-off between the switching speed and the forward voltage drop |          |

| 2. 2. 5 Temperature effects                                                |          |

| 2. 3 Power IGBTs                                                           |          |

| 2. 3. 1 Basic structure and operation                                      |          |

| 2. 3. 2 Typical IGBTs                                                      |          |

| 2. 3. 3 Static blocking capability                                         |          |

| 2. 3. 4 Forward conduction characteristics                                 |          |

| 2. 3. 5 Switching characteristics                                          |          |

| 2. 3. 6 Temperature effects                                                |          |

| 2. 4 Summary                                                               |          |

| References                                                                 | 57<br>58 |

| Chapter 3 Characterisation of IGBT devices at cryogenic temperatures   |     |

|------------------------------------------------------------------------|-----|

| 3. 1 Introduction                                                      | 60  |

| 3. 2 Test system                                                       | 61  |

| 3. 2. 1 Cold chamber                                                   |     |

| 3. 2. 2 Temperature regulation                                         | 63  |

| 3. 3 Sample IGBTs and diodes                                           |     |

| 3. 4 Measurement of static characteristics                             |     |

| 3. 4. 1 On-state characteristics                                       | 68  |

| 3. 4. 2 Forward blocking characteristics                               | 74  |

| 3. 5 Gate parameters                                                   | 76  |

| 3. 5. 1 Gate resistance                                                |     |

| 3. 5. 2 Gate capacitance                                               | 78  |

| 3. 6 Switching characteristics                                         | 81  |

| 3. 6. 1 Switching test circuit                                         | 81  |

| 3. 6. 2 Switching test results                                         | 88  |

| 3. 7 Diode characteristics                                             | 93  |

| 3. 7. 1 Diode static characteristics                                   | 94  |

| 3. 7. 2 Diode reverse recovery characteristics                         | 97  |

| 3. 8 Analysis of experimental results                                  | 100 |

| 3. 8. 1 IGBT cryogenic characteristics                                 | 100 |

| 3. 8. 2 Diode cryogenic characteristics                                | 102 |

| 3. 9 Summary                                                           |     |

| Statement of original contributions                                    | 104 |

| References                                                             | 104 |

|                                                                        |     |

| Chapter 4 Modelling of IGBTs and diodes at cryogenic temperatures      | 106 |

| 4. 1 Introduction                                                      | 106 |

| 4. 2 IGBT model                                                        | 107 |

| 4. 2. 1 IGBT parameters and equations                                  | 107 |

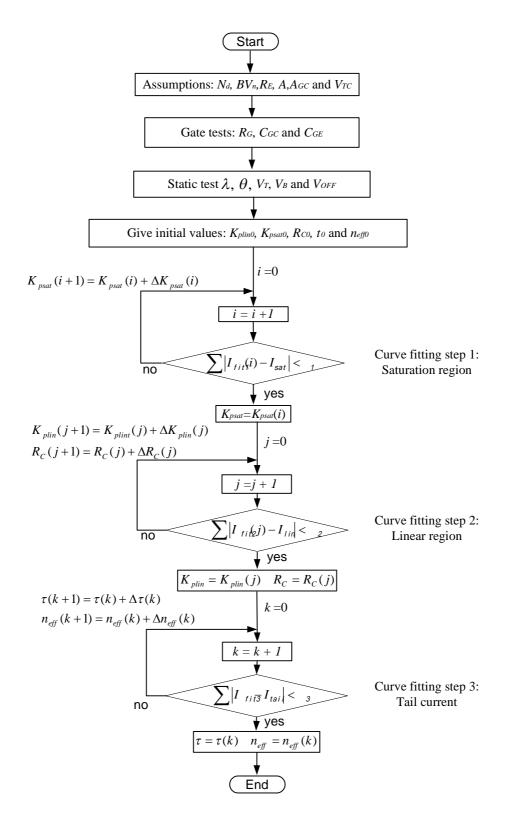

| 4. 2. 2 Parameterisation methodology                                   | 115 |

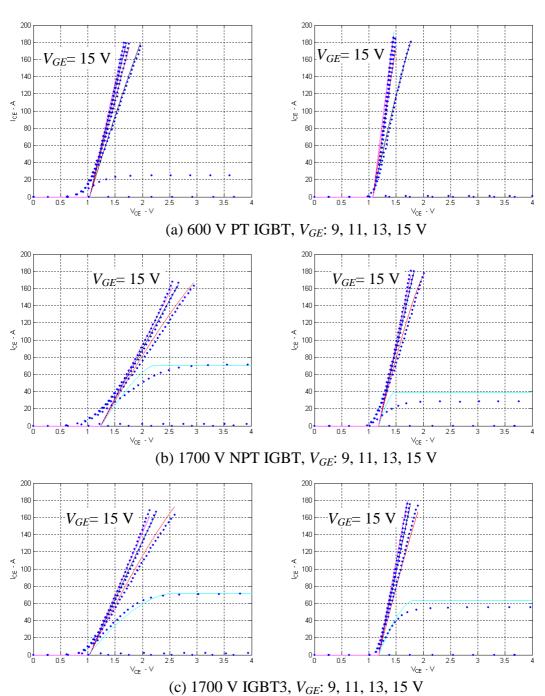

| 4. 2. 3 Parameter results                                              | 125 |

| 4. 2. 4 Power loss comparison between the model and experimental work  | 130 |

| 4. 3 Diode model                                                       | 130 |

| 4. 3. 1 Diode parameters and equations                                 | 131 |

| 4. 3. 2 Parameterisation methodology                                   | 136 |

| 4. 3. 3 Parameter results                                              |     |

| 4. 3. 4 Power loss comparison between the model and experimental work  | 141 |

| 4. 4 Summary                                                           | 142 |

| Statement of original contributions                                    | 142 |

| References                                                             | 143 |

|                                                                        |     |

| Chapter 5 Evaluation of cryogenic converter performance by simulations | 144 |

| 5. 1 Introduction                                                      |     |

| 5. 2 DC-DC step-down (buck) converter simulations                      | 145 |

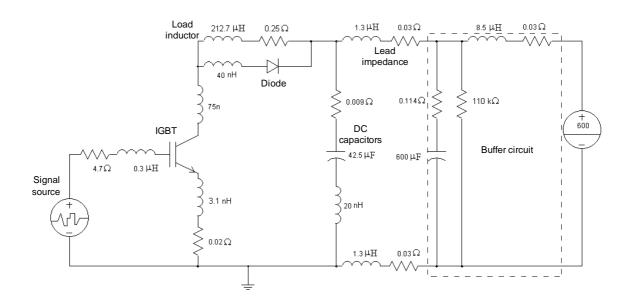

| 5. 2. 1 Converter circuit                                              | 145 |

| 5. 2. 2 Simulation work                                                | 151 |

| 5. 2. 3 Converter summary                                              | 155 |

| 5. 3 PWM Inverter leg simulations                                       | 156 |

|-------------------------------------------------------------------------|-----|

| 5. 3. 1 Inverter circuit.                                               | 156 |

| 5. 3. 2 Simulation work                                                 | 159 |

| 5. 3. 3 Inverter summary                                                | 164 |

| 5.4 Summary                                                             |     |

| Statement of original contributions.                                    |     |

| References                                                              | 166 |

| Chapter 6 Conclusions and further work                                  | 167 |

| 6. 1 Introduction                                                       | 167 |

| 6. 2 Contribution of this thesis                                        | 167 |

| 6. 2. 1 Experimental exploration of three types of IGBTs                | 168 |

| 6. 2. 2 Modelling of IGBTs                                              | 169 |

| 6. 2. 3 Simulation of converters                                        | 169 |

| 6. 3 Further work                                                       | 170 |

| 6. 4 Conclusions                                                        | 171 |

| References                                                              | 171 |

| Appendix 1 List of publications resulting from work in this thesis      | 172 |

| Appendix 2 Cold chamber and vacuum pumps                                |     |

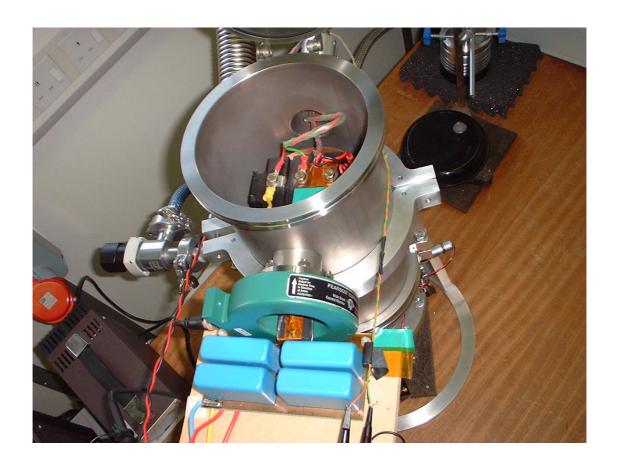

| Appendix 3 Cold chamber holding a device under test                     |     |

| Appendix 4 MIL-STD-750D test method 3471 for semiconductor devices      |     |

| Appendix 5 IGBT gate circuit from Dynex                                 |     |

| Appendix 6 IGBT model results                                           | 186 |

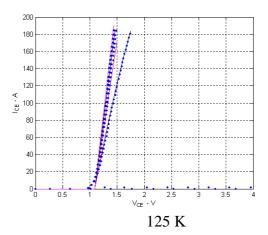

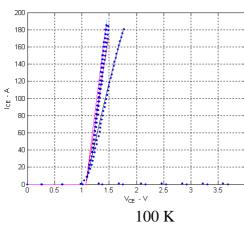

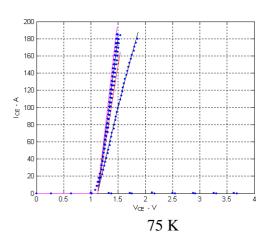

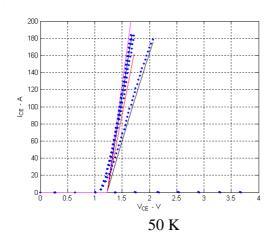

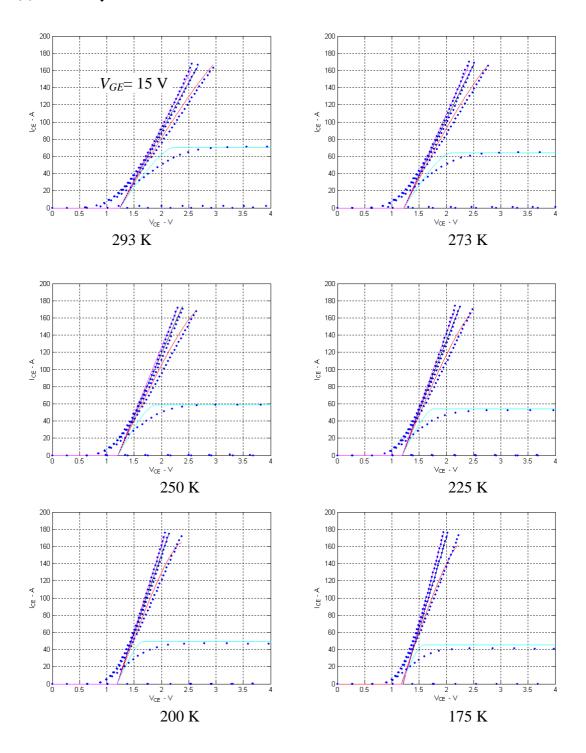

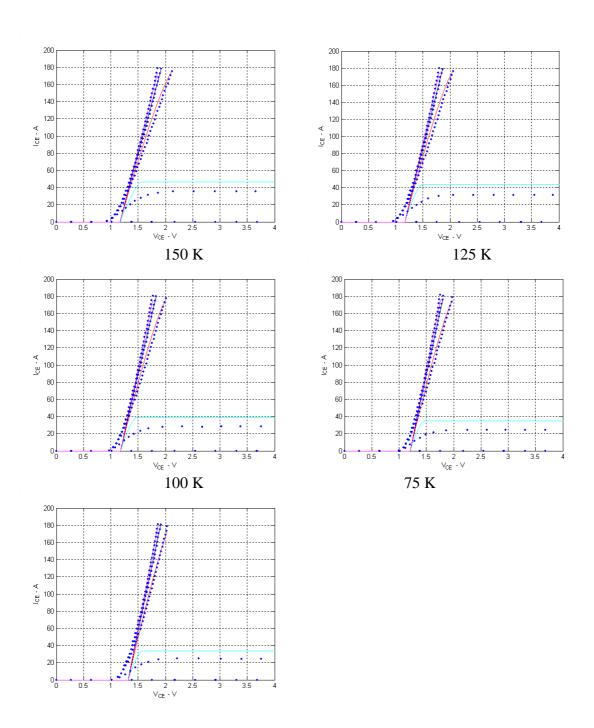

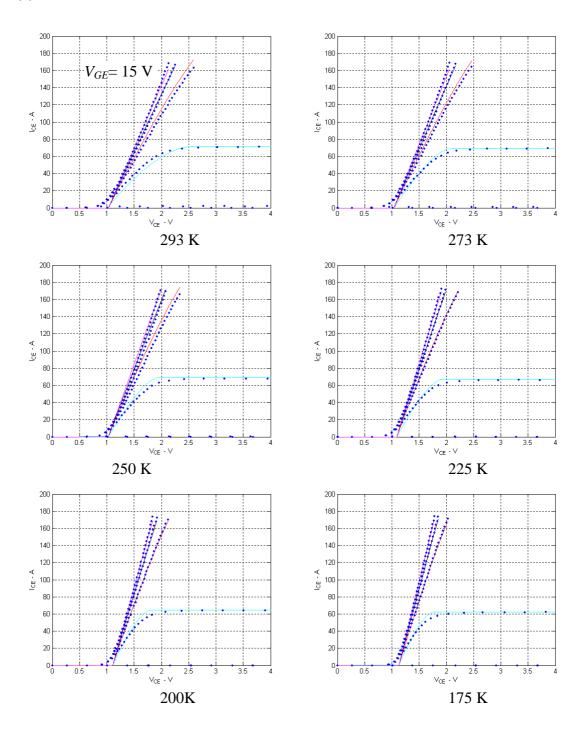

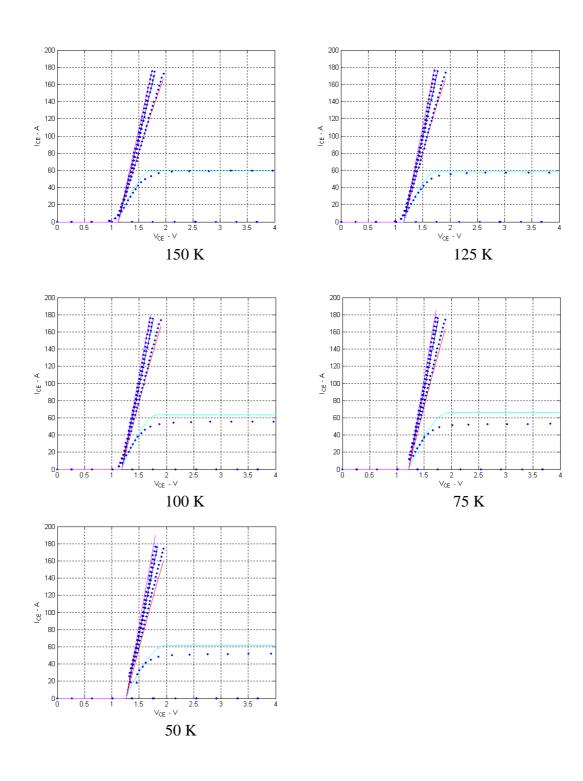

| A 6. 1 On-state characteristics from the IGBT model at low temperatures | 186 |

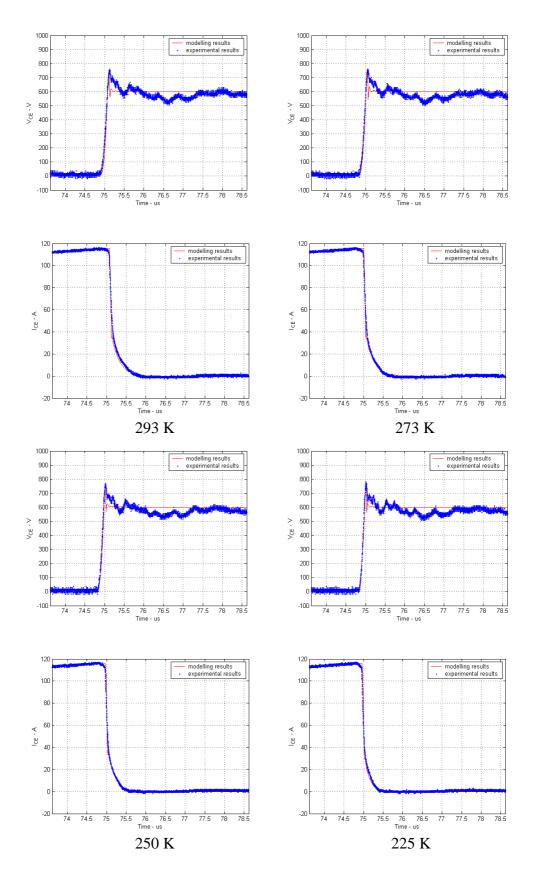

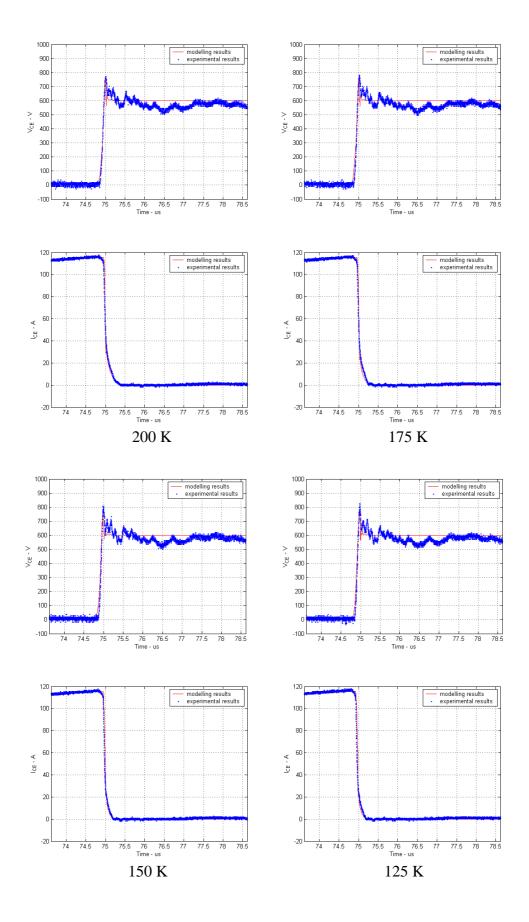

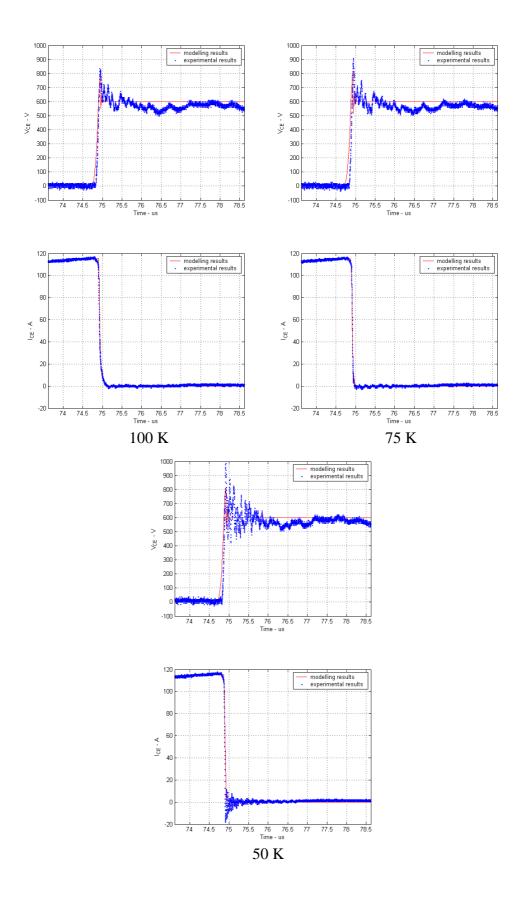

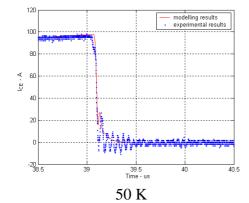

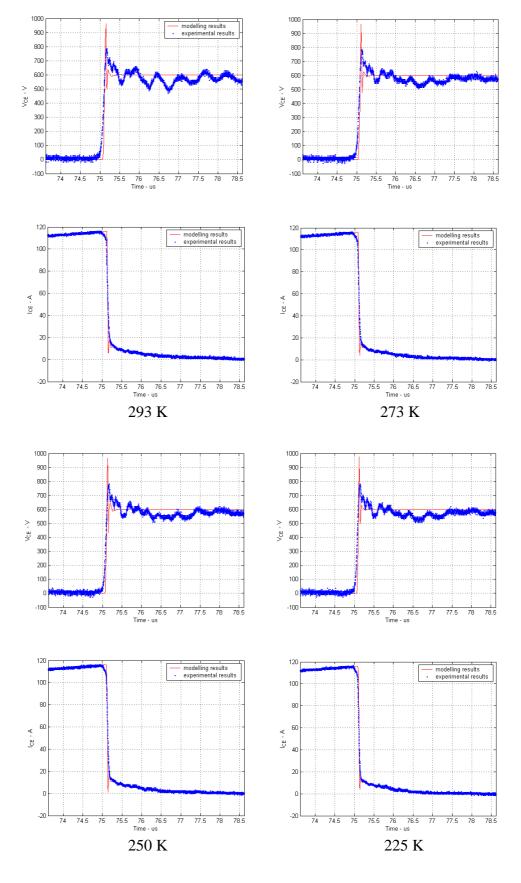

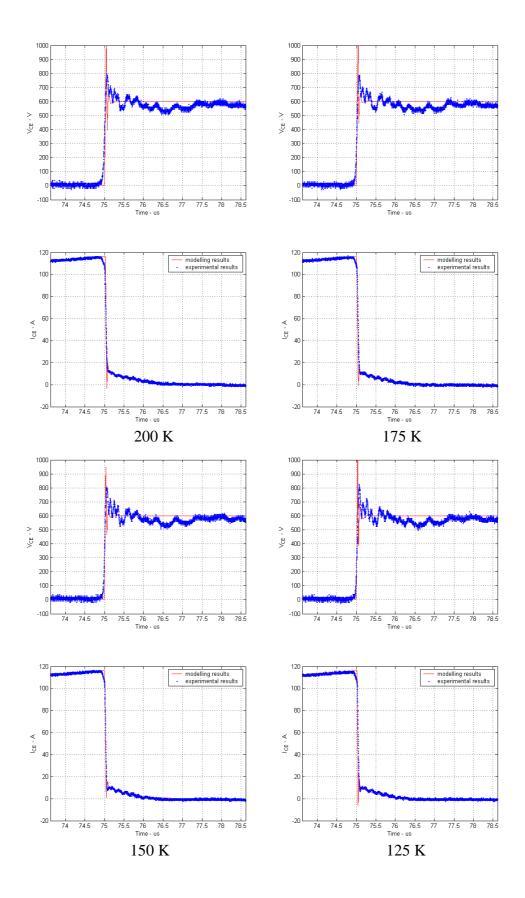

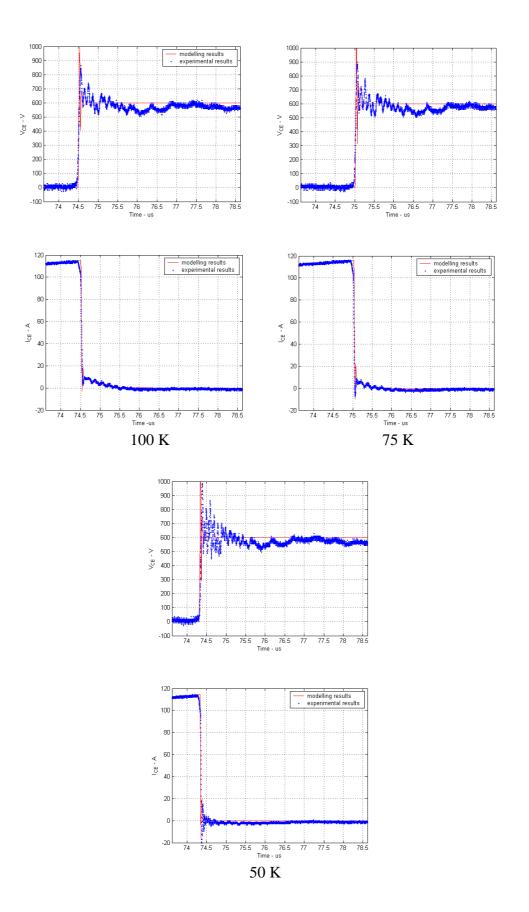

| A 6. 2 Turn off transients from the IGBT model at low temperatures      | 193 |

# **List of Figures and Tables**

| Figure 1-1 Structure of a typical half-cell of a power BJT                                                      | 13       |

|-----------------------------------------------------------------------------------------------------------------|----------|

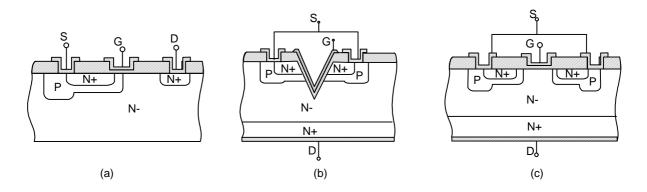

| Figure 1-2 Cross sections of three typical MOSFETs                                                              |          |

| Figure 1-3 Structure of an IGBT.                                                                                |          |

| Figure 1-4 MOSFET and IGBT application range                                                                    |          |

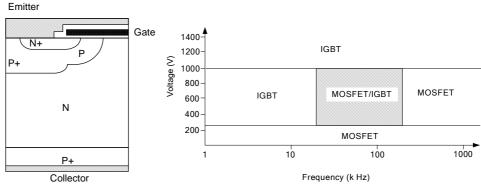

| Figure 2-1 Structure of a typical PiN diode                                                                     | 31       |

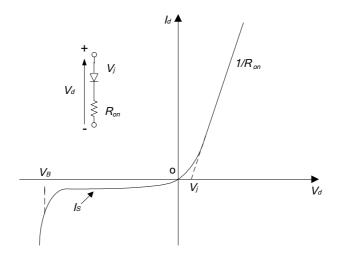

| Figure 2-2 I-V characteristics of a PiN diode                                                                   |          |

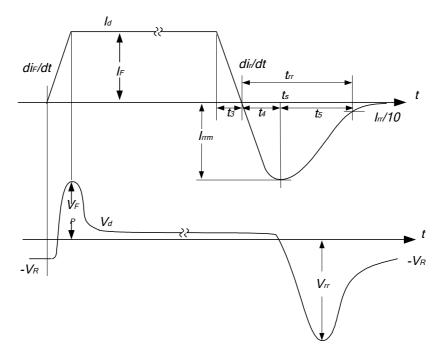

| Figure 2-3 Sketched current and voltage waveforms during turn-on and turn-off transients                        |          |

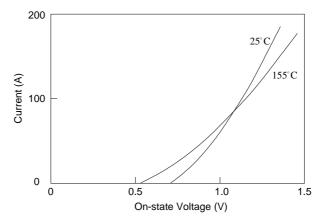

| Figure 2-4 Temperature effect on the forward characteristics of a 2.5 kV diode                                  |          |

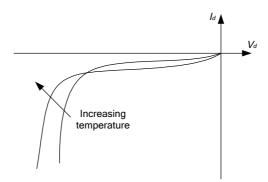

| Figure 2-5 Temperature effect on the reverse bias characteristics of a power diode                              |          |

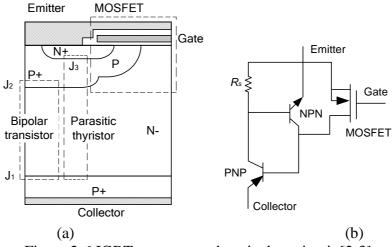

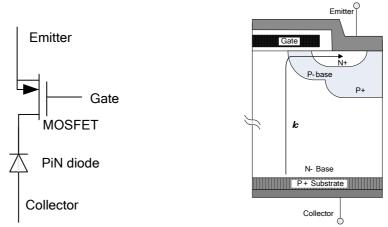

| Figure 2-6 IGBT structure and equivalent circuit                                                                |          |

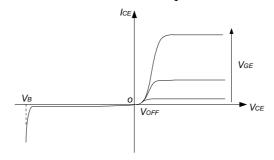

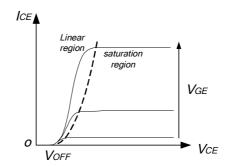

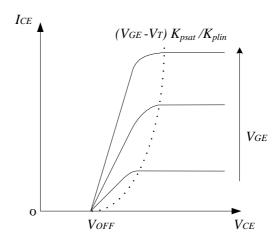

| Figure 2-7 Output characteristics of an IGBT                                                                    |          |

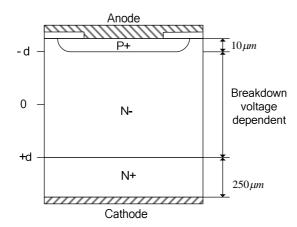

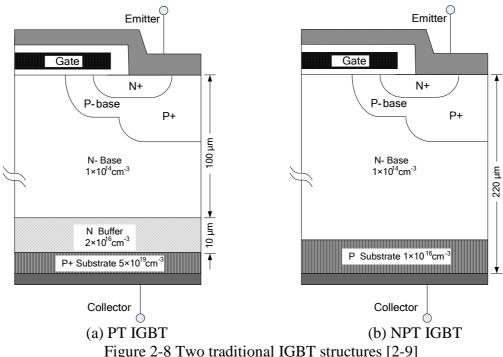

| Figure 2-8 Two traditional IGBT structures                                                                      |          |

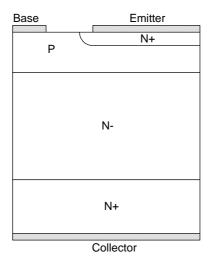

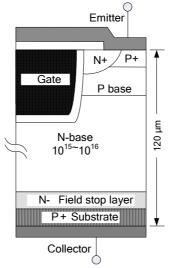

| Figure 2-9 Structure of a IGBT3                                                                                 |          |

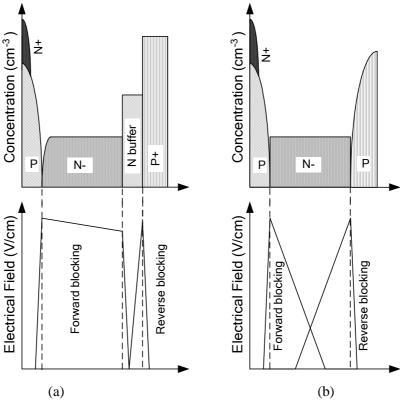

| Figure 2-10 Doping profiles and electric field distributions in (a) PT and (b) NPT IGBTs                        |          |

| under forward and reverse blocking conditions                                                                   | 47       |

| Figure 2-11 PiN diode/MOSFET model                                                                              | 48       |

| Figure 2-12 IGBT forward conduction characteristics                                                             | 50       |

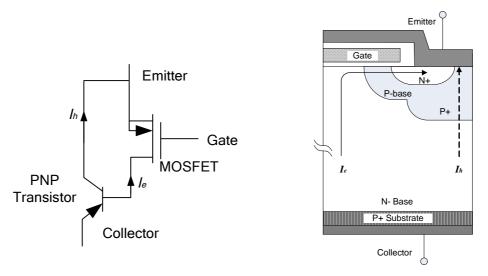

| Figure 2-13 The equivalent circuit and current distribution for the bipolar transistor /MOSFET model of an IGBT | 51       |

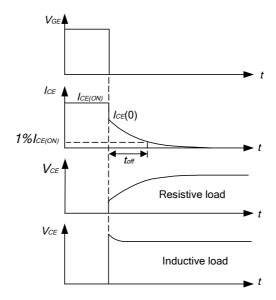

| Figure 2-14 Sketched turn-off waveforms for an IGBT                                                             | 51<br>53 |

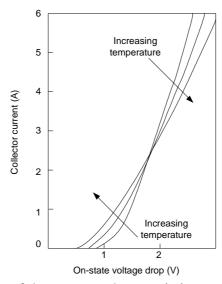

| Figure 2-15 Typical variation of the on-state characteristics at elevated temperatures                          |          |

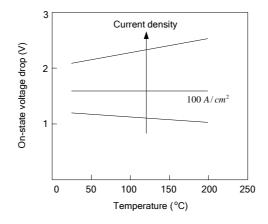

| Figure 2-16 Variation of on-state voltage drop of a 600 V NPT IGBT at elevated                                  | 55       |

| temperatures                                                                                                    | 55       |

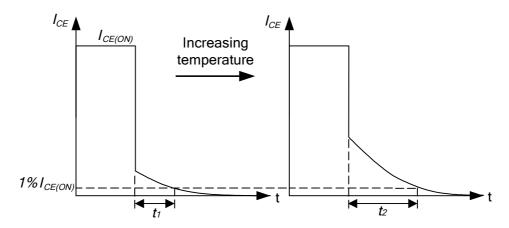

| Figure 2-17 Variation in turn-off waveforms at an increased temperature                                         |          |

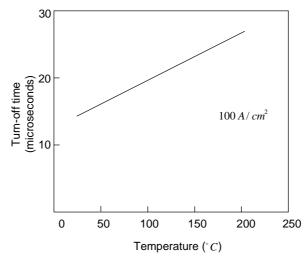

| Figure 2-18 Increase in turn-off time with temperature for a NPT IGBT                                           |          |

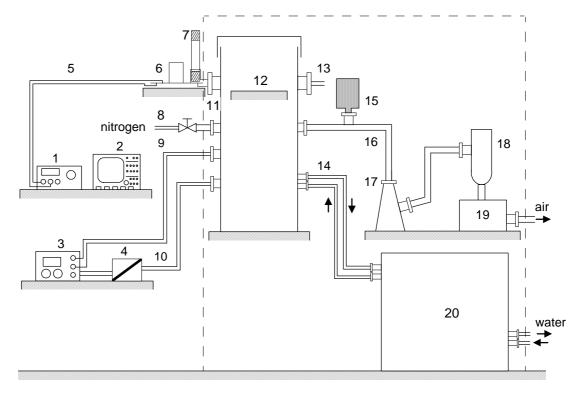

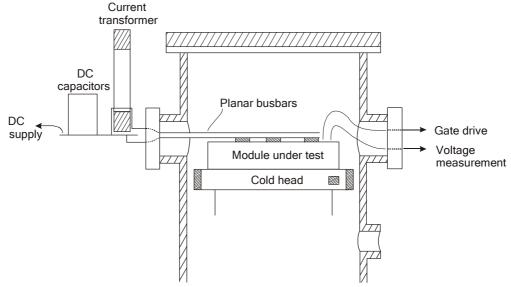

| Figure 3-1 Test system arrangement                                                                              | 62       |

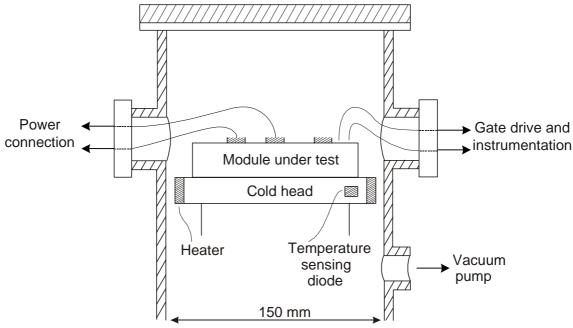

| Figure 3-2 Cold chamber cross- section diagram                                                                  |          |

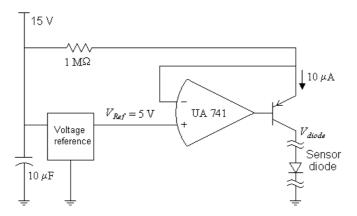

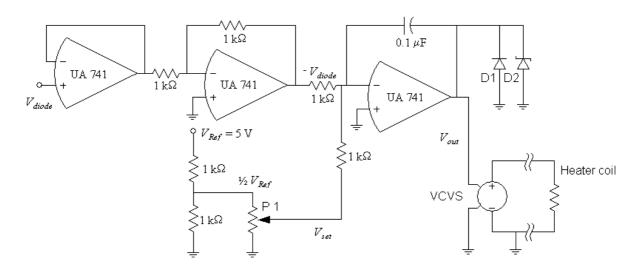

| Figure 3-3 Temperature measurement and control circuits                                                         |          |

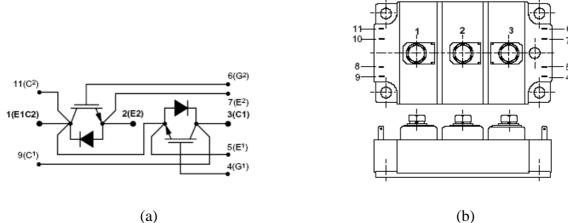

| Figure 3-4 Electrical connection for the tested modules                                                         |          |

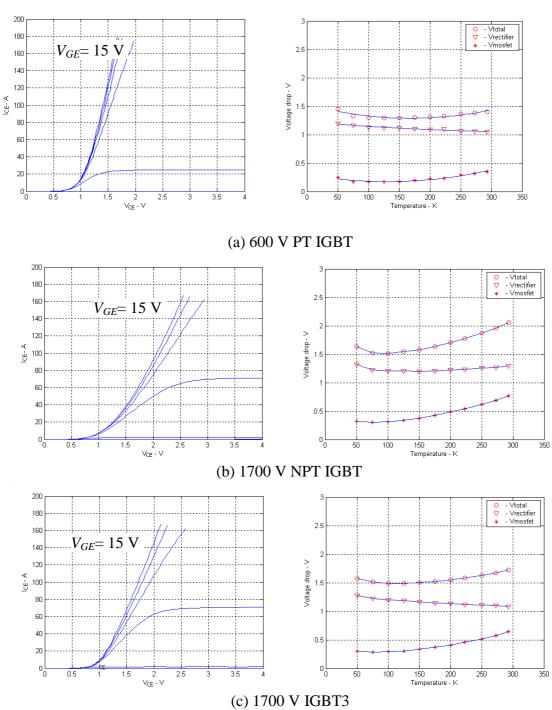

| Figure 3-5 On-state voltage drops at 100A from 50 K to 300 K                                                    |          |

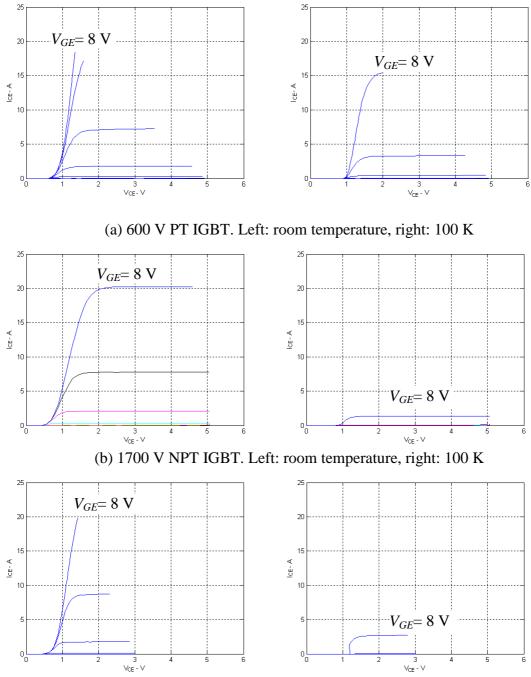

| Figure 3-6 On-state characteristics in the subthreshold region                                                  |          |

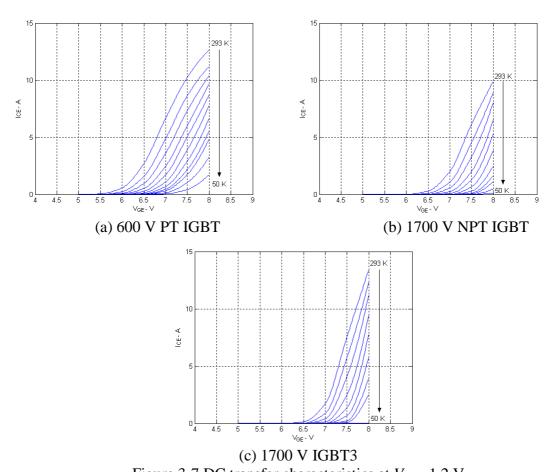

| Figure 3-7 DC transfer characteristics at $V_{CE}$ =1.2 V                                                       |          |

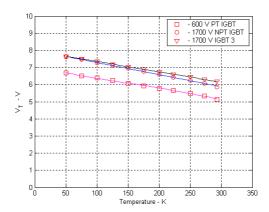

| Figure 3-8 Threshold voltage variations from 50 K to room temperature                                           | 74       |

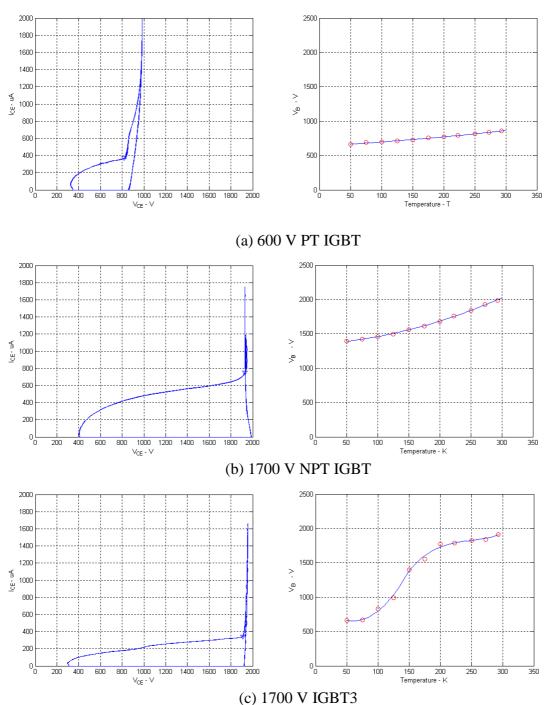

| Figure 3-9 Measurements and temperature dependence of forward breakdown voltage                                 | 75       |

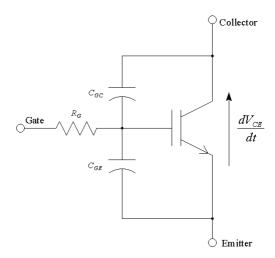

| Figure 3-10 IGBT gate resistance and parasitic capacitances                                                     | 76       |

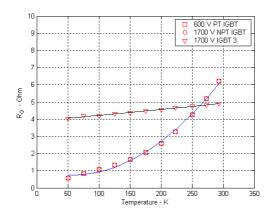

| Figure 3-11 Temperature characteristics of gate resistors                                                       | 77       |

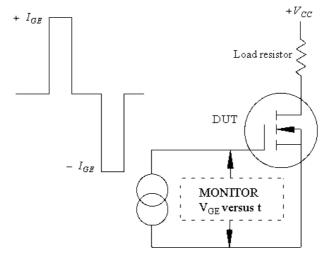

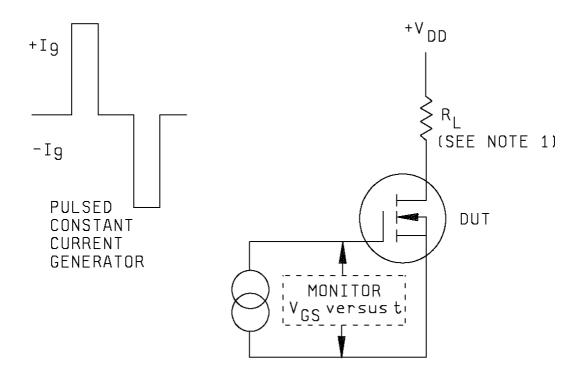

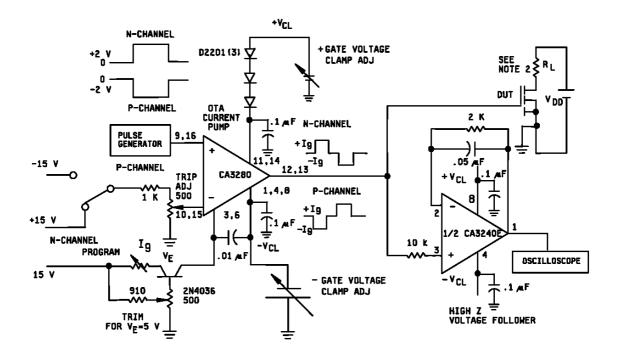

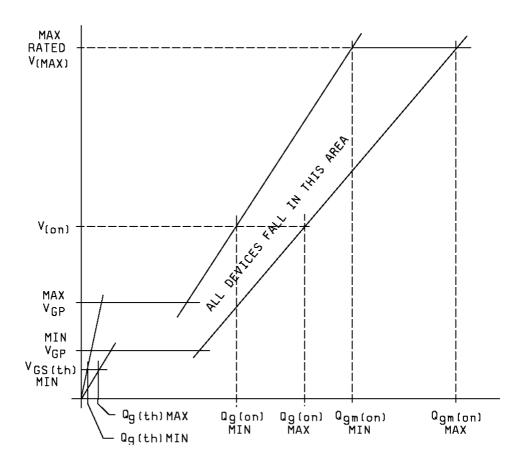

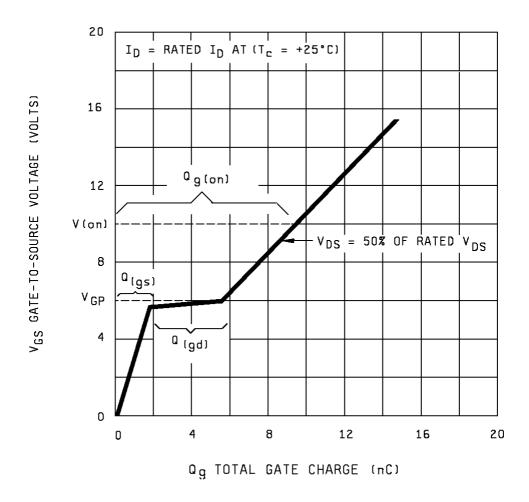

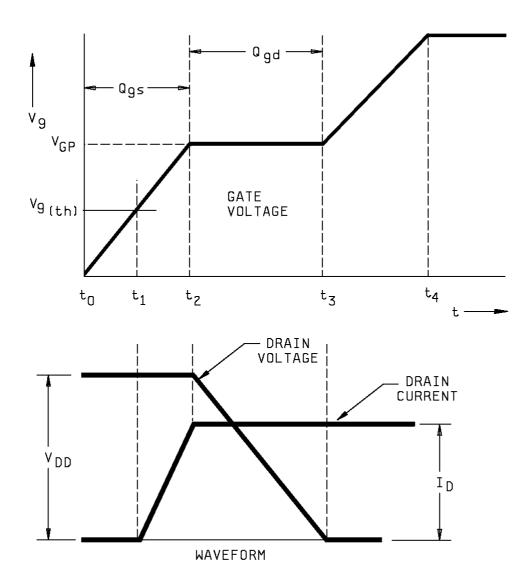

| Figure 3-12 Gate charge test diagram, $Q_{GE} = I_{GE} \times t$                                                | 78       |

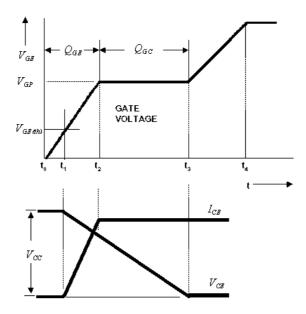

| Figure 3-13 Gate charge waveforms                                                                               |          |

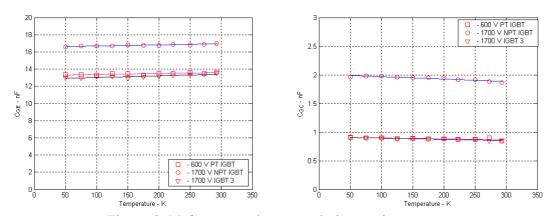

| Figure 3-14 Gate capacitance variation against temperature                                                      |          |

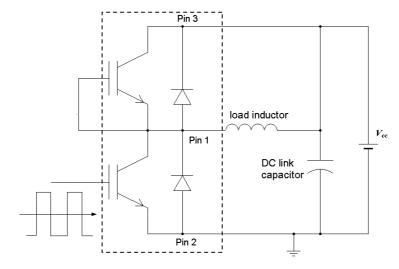

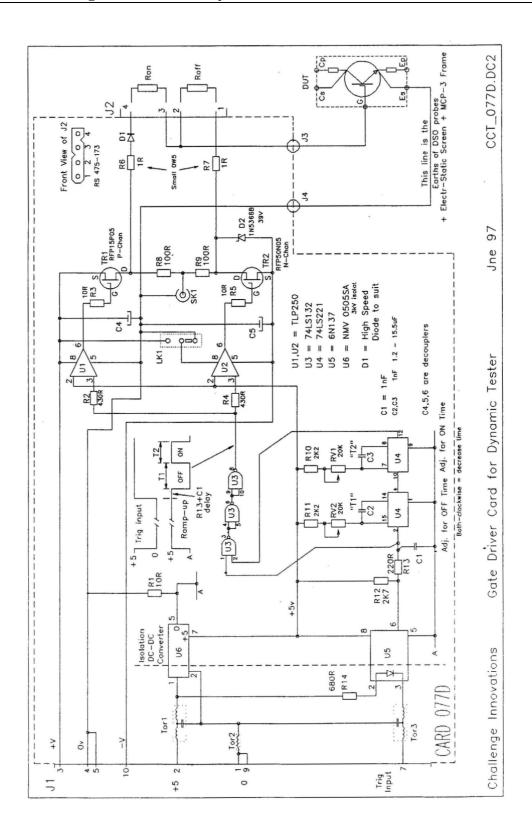

| Figure 3-15 Switching test circuit.                                                                             |          |

| Figure 3-16 Electrical connection for switching tests.                                                          |          |

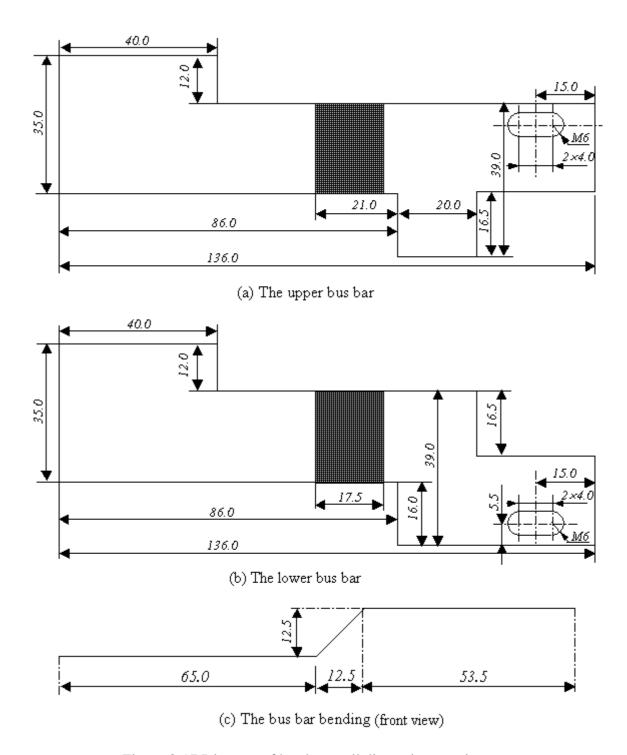

| Figure 3-17 Diagram of bus bars                                                                                 |          |

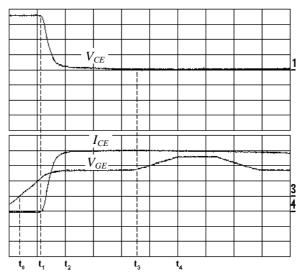

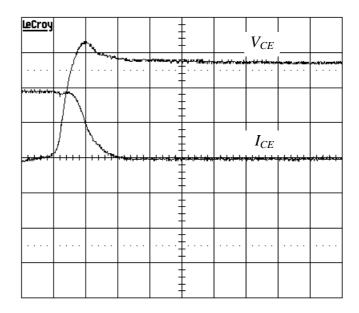

| Figure 3-18 A sample of switching test results                                                                  |          |

| Figure 3-19 Sample results for switching measurements on an IGBT                                                | 87       |

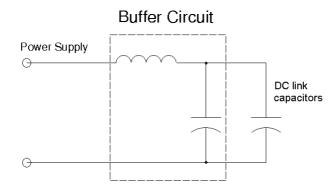

| Figure 3-20 Buffer circuit                                                             | 88  |

|----------------------------------------------------------------------------------------|-----|

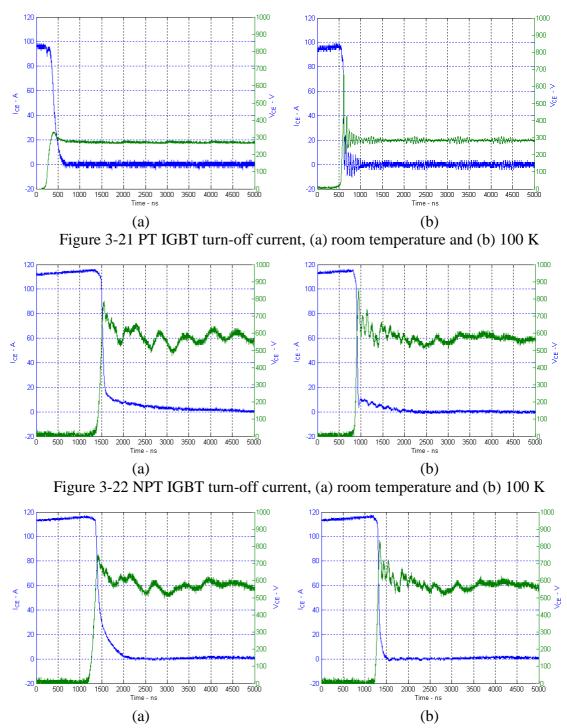

| Figure 3-21 PT IGBT turn-off current, (a) room temperature and (b) 100 K               | 89  |

| Figure 3-22 NPT IGBT turn-off current, (a) room temperature and (b) 100 K              |     |

| Figure 3-23 IGBT3 turn-off current, (a) room temperature and (b) 100 K                 |     |

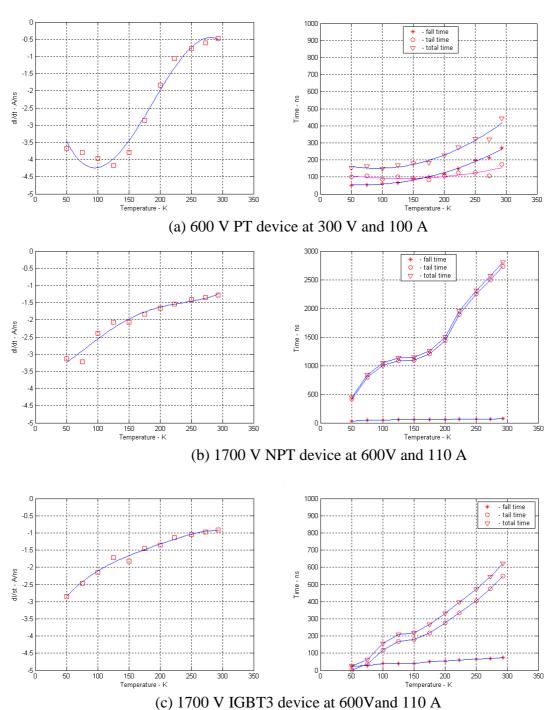

| Figure 3-24 Turn-off di/dt (left) and turn-off times (right) from 50 K to 300 K        |     |

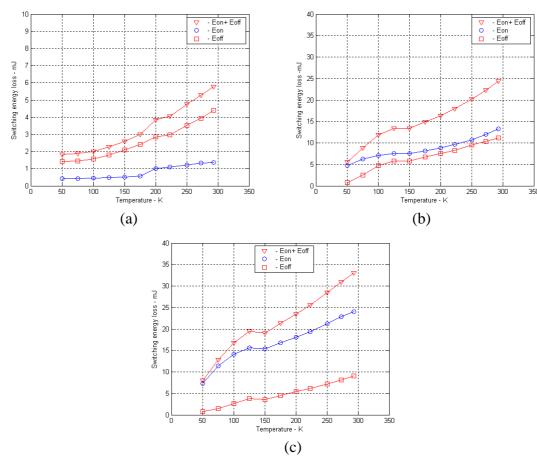

| Figure 3-25 Switching energy losses from 50 K to 300 K                                 |     |

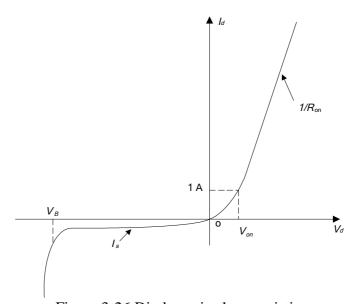

| Figure 3-26 Diode static characteristics.                                              |     |

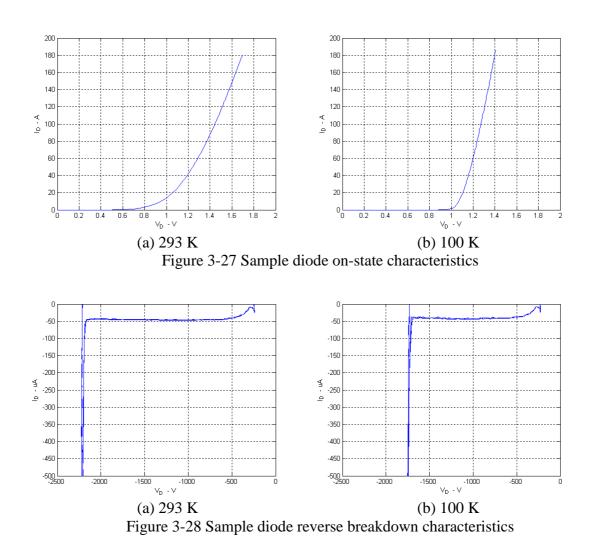

| Figure 3-27 Sample diode on-state characteristics                                      |     |

| Figure 3-28 Sample diode reverse breakdown characteristics                             |     |

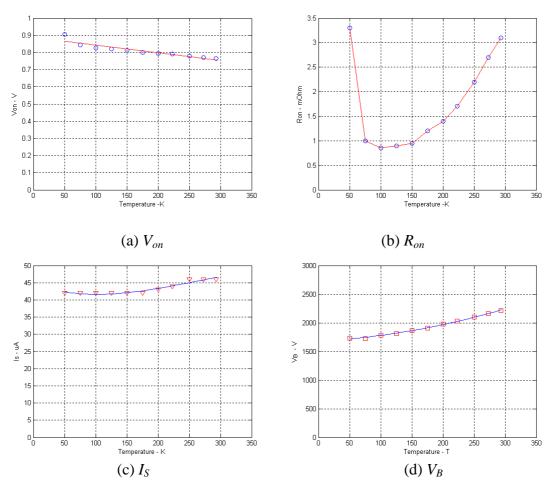

| Figure 3-29 Diode static parameter variations at low temperatures                      |     |

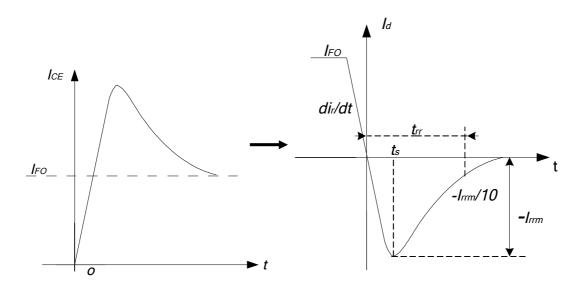

| Figure 3-30 Diode reverse recovery transient.                                          |     |

| Figure 3-31 Diode reverse recovery currents at room temperature and 100 K              |     |

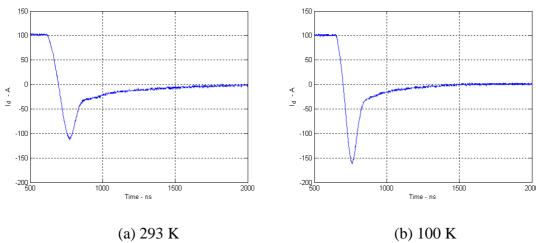

| Figure 3-32 Diode reverse recovery parameter variations at low temperatures            |     |

| rigure 5-52 Diode reverse recovery parameter variations at low temperatures            | 100 |

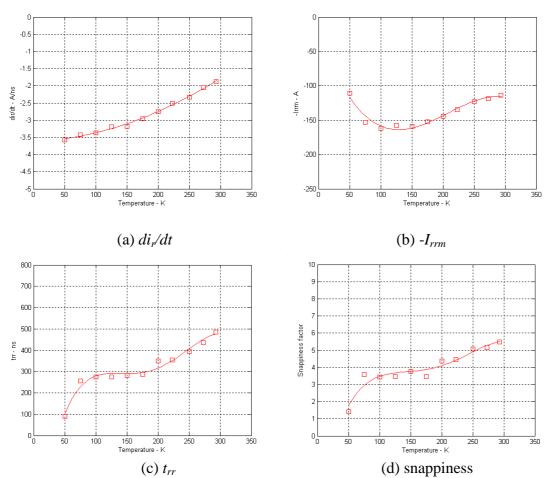

| Figure 4-1 IGBT model                                                                  | 107 |

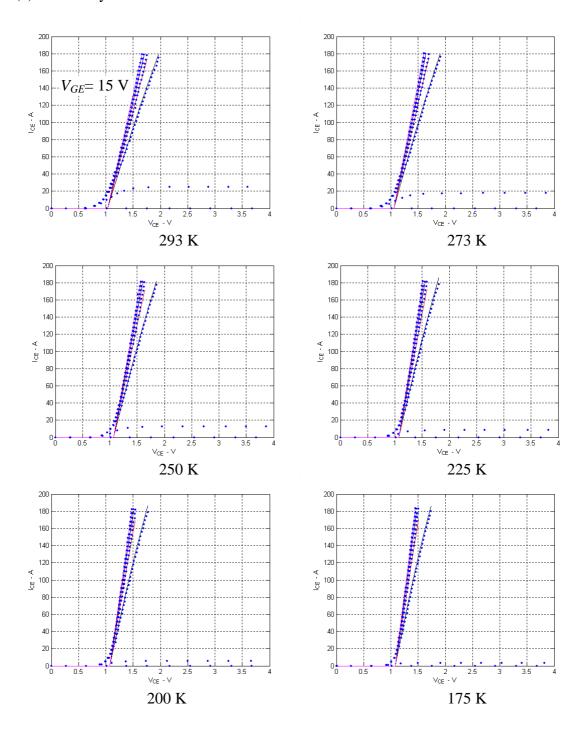

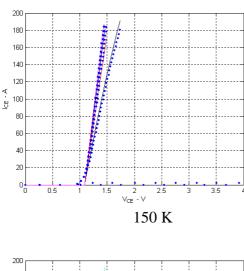

| Figure 4-2 IGBT on-state characteristics                                               |     |

| Figure 4-3 Flow chart for the model parameterisation process                           |     |

| Figure 4-4 On-state characteristics from the IGBT model                                |     |

|                                                                                        |     |

| Figure 4-5 The circuit to simulate the IGBT turn-off transients                        |     |

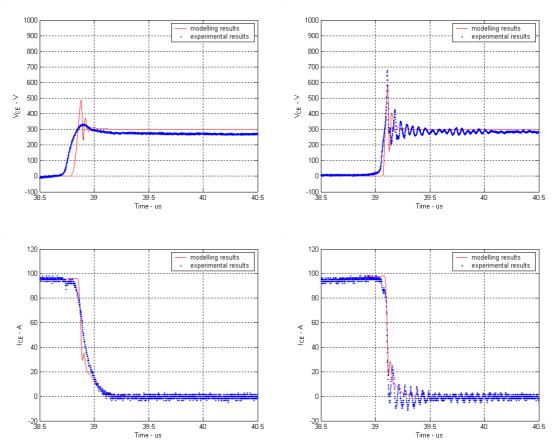

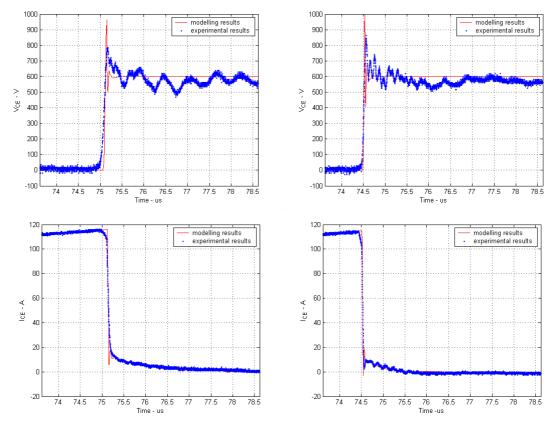

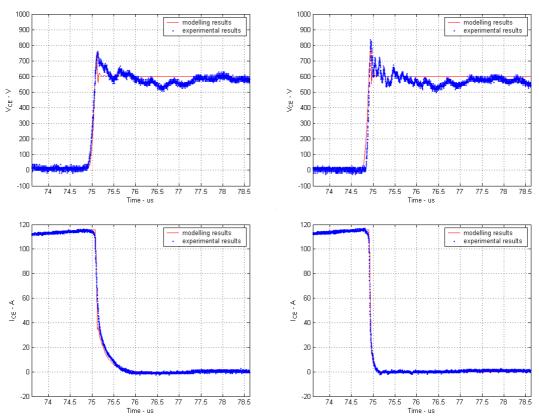

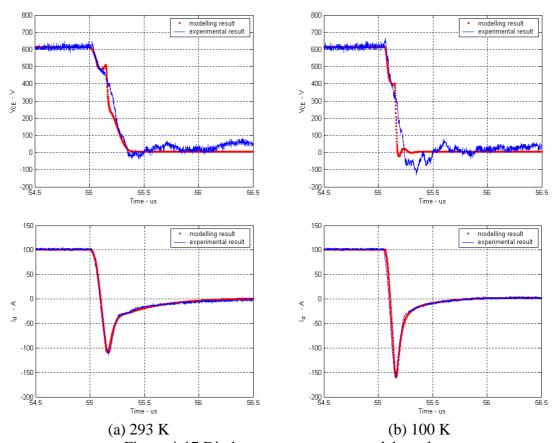

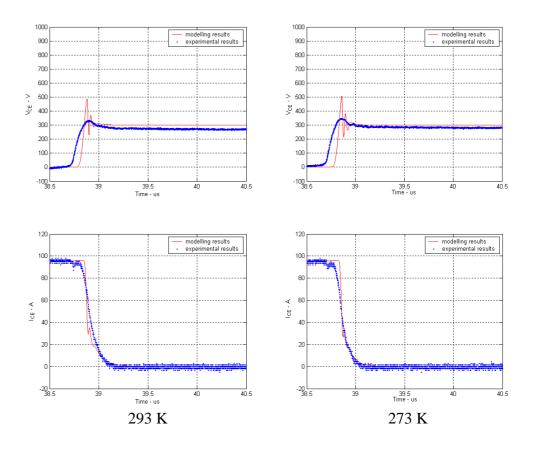

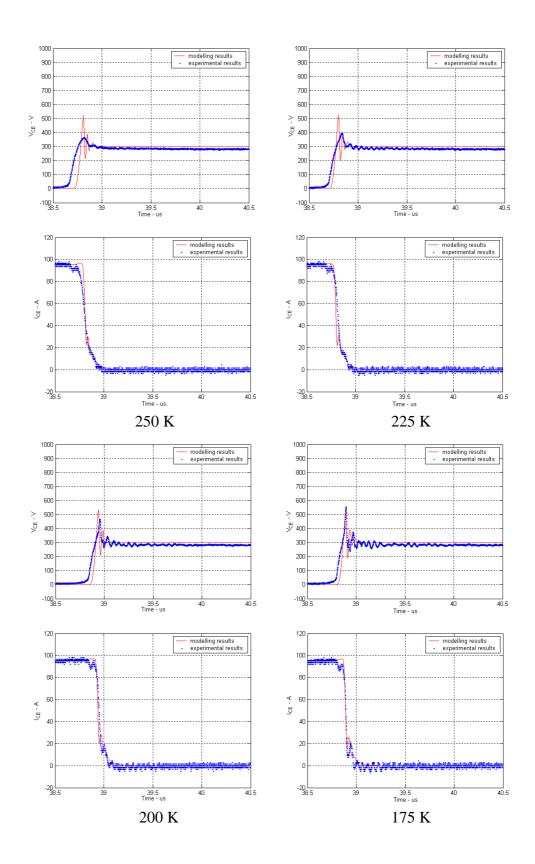

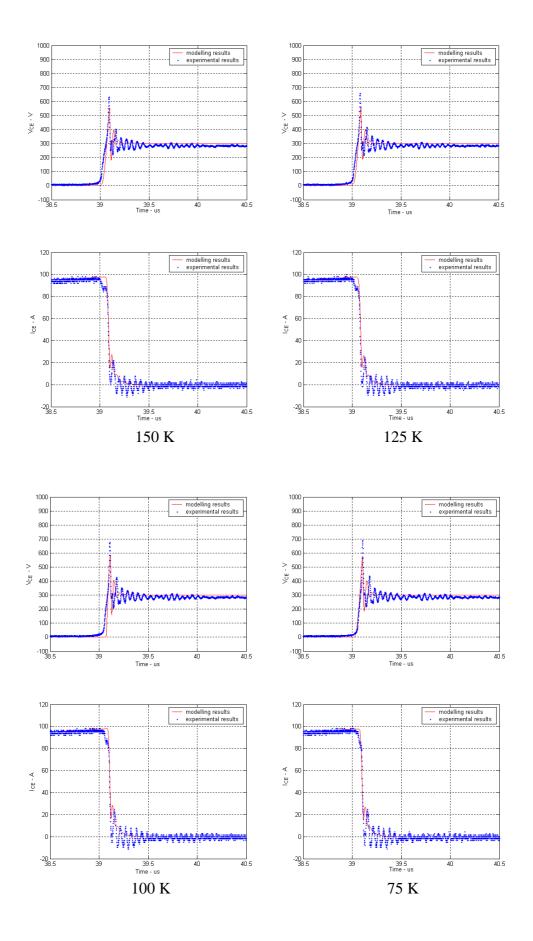

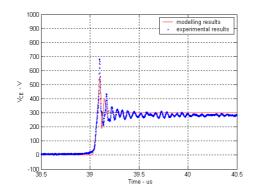

| Figure 4-6 Turn-off transient of the 600 V PT IGBT                                     |     |

| Figure 4-7 Turn-off transient of the 1700 V NPT IGBT                                   |     |

| Figure 4-8 Turn-off transient of the 1700 V IGBT3                                      |     |

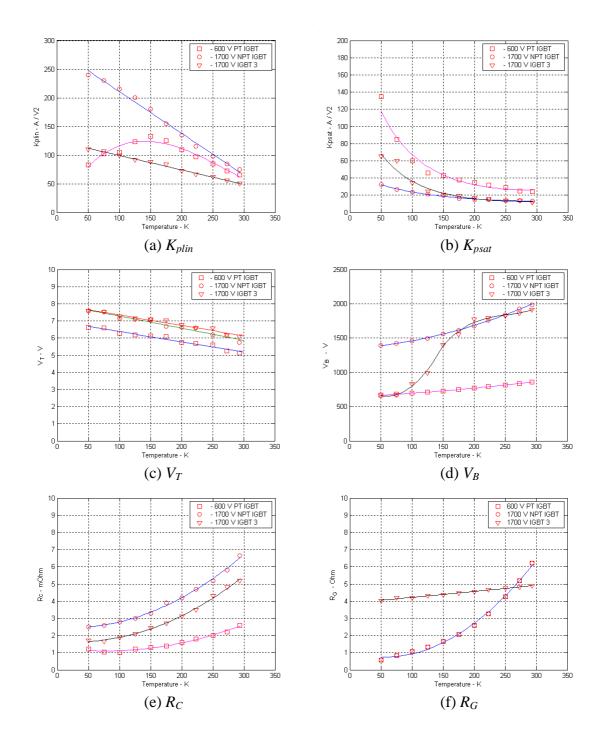

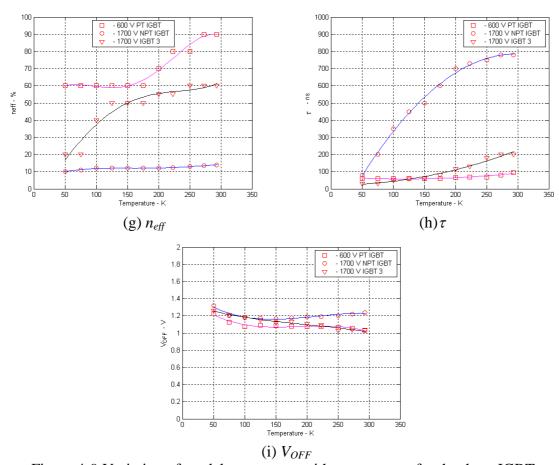

| Figure 4-9 Variation of model parameters with temperature for the three IGBTs          |     |

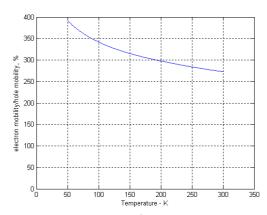

| Figure 4-10 Mobility ratio $\mu_n/\mu_p$ against temperature                           |     |

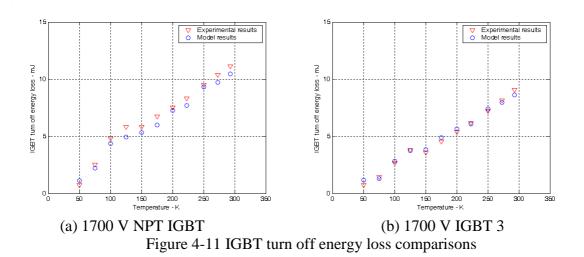

| Figure 4-11 IGBT turn off power loss comparisons                                       |     |

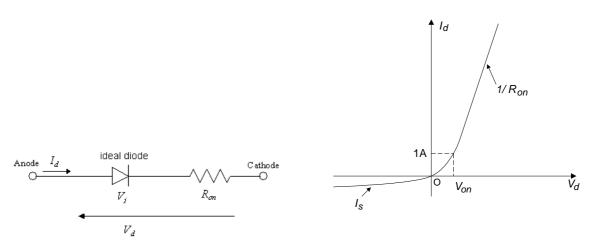

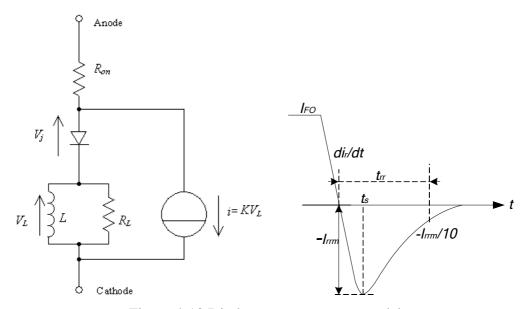

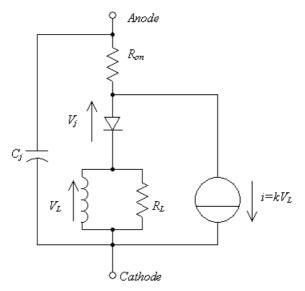

| Figure 4-12 Diode static model and characteristics                                     |     |

| Figure 4-13 Diode reverse recovery model                                               |     |

| Figure 4-14 The complete diode model                                                   |     |

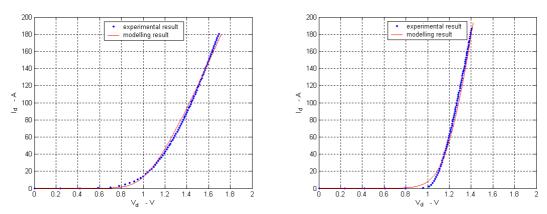

| Figure 4-15 Diode static modelling results                                             |     |

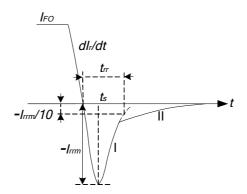

| Figure 4-16 Practical power diode reverse recovery waveform                            | 137 |

| Figure 4-17 Diode reverse recovery model results                                       | 139 |

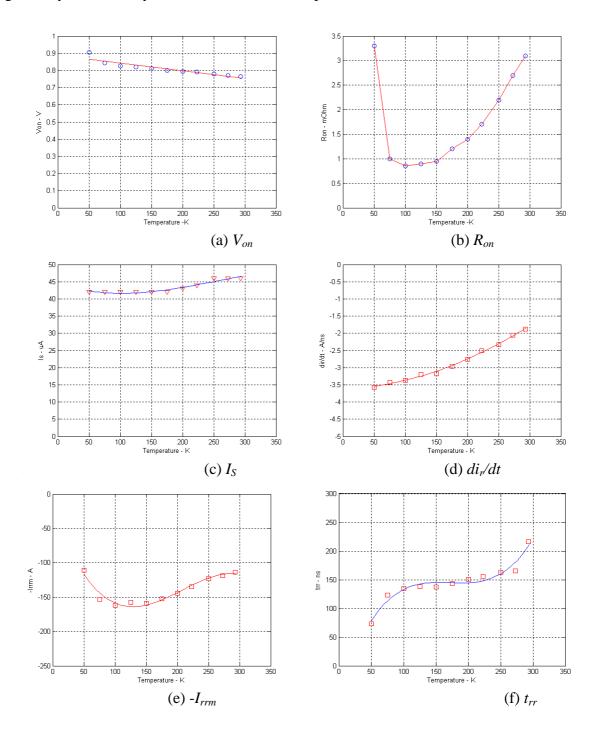

| Figure 4-18 Parameter variations against temperature for the diode in the 1700 V Dynex |     |

| module                                                                                 |     |

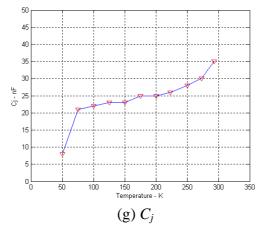

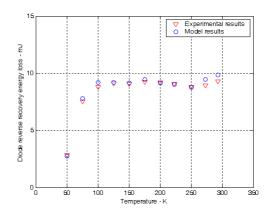

| Figure 4-19 Diode reverse recovery power loss comparisons                              | 142 |

|                                                                                        |     |

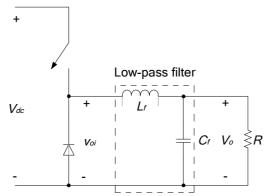

| Figure 5-1 Basic circuit of a step-down DC-DC converter [5-1]                          |     |

| Figure 5-2 Voltage and current waveforms in a step-down converter [5-1]                | 147 |

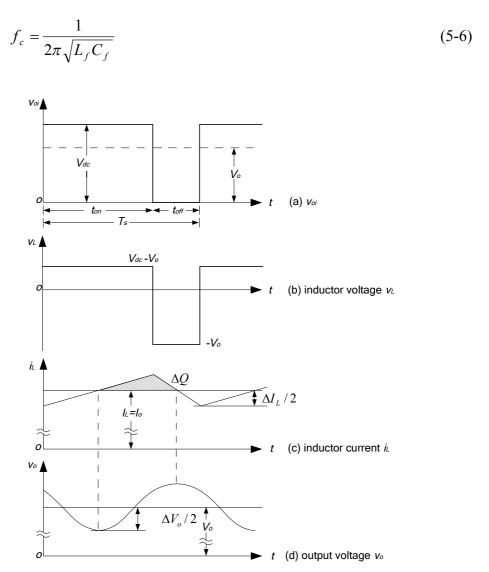

| Figure 5-3 DC-DC step-down converter simulation circuit                                | 148 |

| Figure 5-4 Converter current and voltage waveforms at 293 K from case I-2, 150A        | 151 |

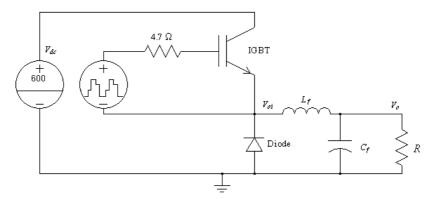

| Figure 5-5 Buck converter energy losses for Mode I, 10 kHz                             | 153 |

| Figure 5-6 Buck converter energy losses for Mode II, 50 kHz                            | 154 |

| Figure 5-7 Buck converter efficiency variation against temperature                     |     |

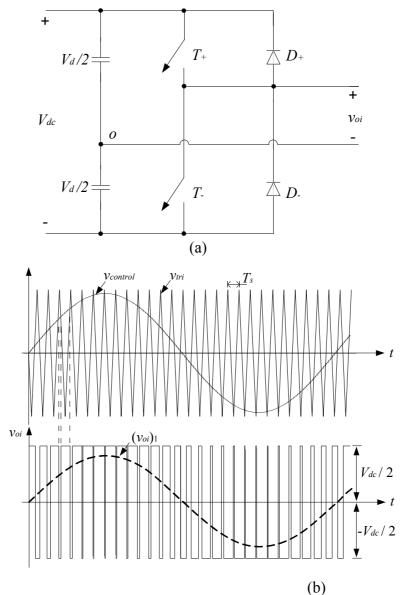

| Figure 5-8 Basic inverter leg circuit and PWM waveforms                                |     |

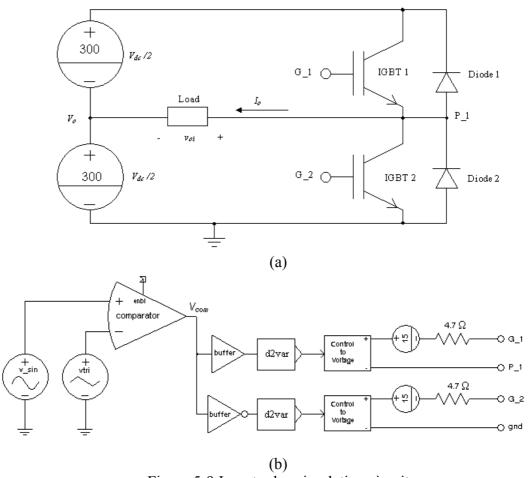

| Figure 5-9 Inverter leg simulation circuit                                             |     |

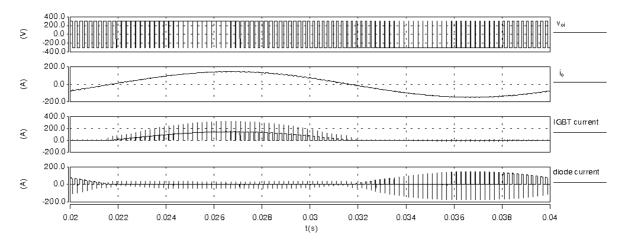

| Figure 5-10 Inverter current and voltage waveforms for case I-2                        |     |

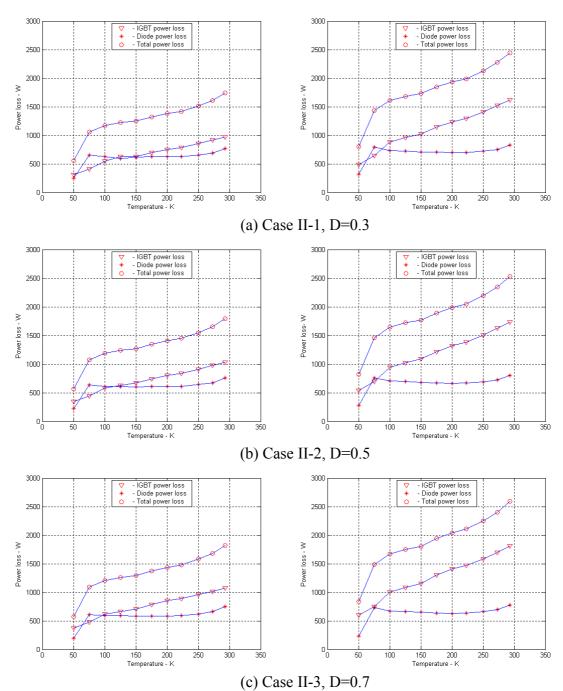

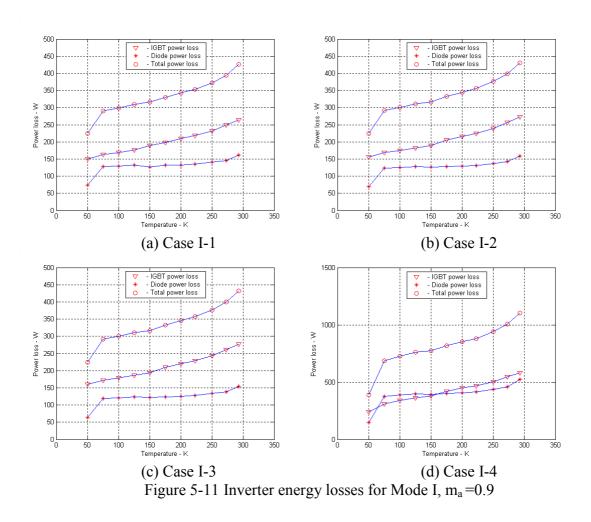

| Figure 5-11 Inverter energy losses for Mode I, m <sub>a</sub> =0.9                     |     |

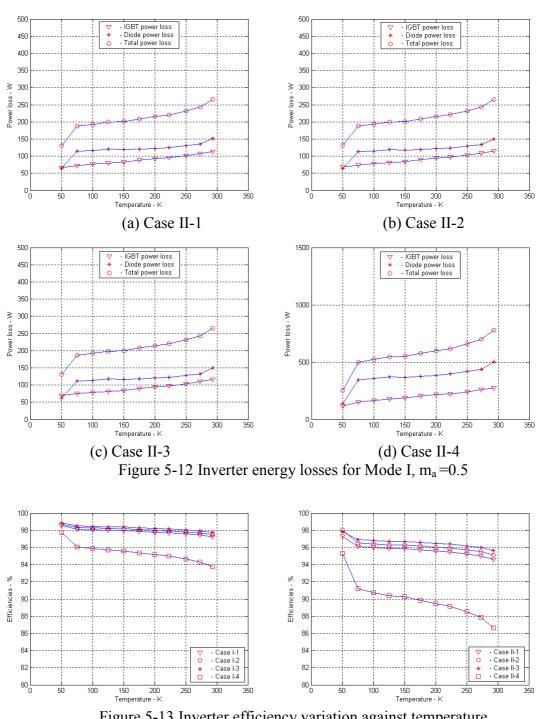

| Figure 5-12 Inverter energy losses for Mode I, m <sub>a</sub> =0.5                     |     |

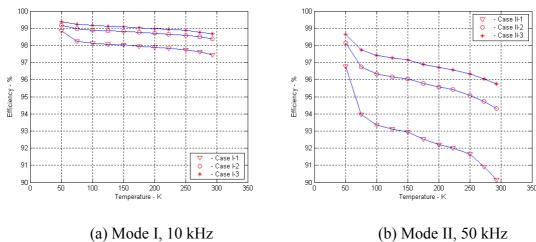

| Figure 5-13 Inverter efficiency variation against temperature                          |     |

| L)                                                                                     |     |

| Table 2-1 Temperature effect on the reverse recovery characteristics of a 1200V, 30 |     |  |

|-------------------------------------------------------------------------------------|-----|--|

|                                                                                     | 38  |  |

| Table 2-2 Comparison of three IGBTs                                                 |     |  |

| Table 3-1 Sensor diode specifications                                               | 64  |  |

| Table 3-2 IGBT specifications                                                       | 66  |  |

| Table 3-3 Curve tracer information                                                  | 67  |  |

| Table 5-1 Parameters for the converter simulation                                   | 149 |  |

| Table 5-2 Parameters for the inverter leg simulation                                | 160 |  |

# **List of Abbreviations and Symbols**

| Abbreviation | Complete forms                                         |

|--------------|--------------------------------------------------------|

| AC           | Alternating Current                                    |

| BJT          | Bipolar Junction Transistor                            |

| DC           | Direct Current                                         |

| EMC          | Electromagnetic Compatibility                          |

| HTS          | High Temperature Superconductor                        |

| IGBT         | Insulated Gate Bipolar Transistor                      |

| kW           | kilo Watt                                              |

| LDMOS        | Lateral double-diffused MOSFET                         |

| LTS          | Low Temperature Superconductor                         |

| MISFET       | Metal Insulator Semiconductor Field-Effect Transistors |

| MOSFET       | Metal Oxide Semiconductor Field Effect Transistor      |

| MRI          | Magnetic Resonance Imaging.                            |

| MW           | Mega Watt                                              |

| NPT          | Non-Punch Through                                      |

| ppm          | parts per million                                      |

| PT           | Punch Through                                          |

| PWM          | Pulse Width Modulation                                 |

| RF           | Radio Frequency                                        |

| rpm          | revolutions per minute                                 |

| SMES         | Superconducting Magnetic Energy Storage                |

| VMOS         | V-groove double-diffused MOSFET                        |

| VDMOS        | Vertical double-diffused MOSFET                        |

| Symbol         | Description                                                         | Unit               |

|----------------|---------------------------------------------------------------------|--------------------|

| $\overline{A}$ | Total active area of an IGBT                                        | cm <sup>2</sup>    |

| $A_{CE}$       | Collector emitter overlap area of an IGBT                           | cm <sup>2</sup>    |

| $A_{GC}$       | Gate collector overlap area of an IGBT                              | cm <sup>2</sup>    |

| B              | Mobility ratio $\mu_n/\mu_p$                                        | _                  |

| $BV_n$         | Breakdown voltage index                                             | -                  |

| $C_{CE}$       | Collector- emitter oxide capacitance of an IGBT                     | F                  |

| $C_f$          | Capacitance in the low-pass filter for the buck converter           | F                  |

| $C_{GE}$       | Gate- emitter capacitance of an IGBT                                | F                  |

| $C_{GC, ACT}$  | Actual gate collector capacitance of an IGBT                        | F                  |

| $C_{GC}$       | Gate collector capacitance of an IGBT from the gate charge test     | F                  |

| $C_0$          | Diode junction capacitance under zero bias                          | F                  |

| $C_{OX}$       | Capacitance per unit area of gate oxide                             | F cm <sup>-2</sup> |

| $C_i$          | Junction capacitance corresponding to a junction voltage $V_i$ in a | F                  |

| •              | diode                                                               |                    |

| D              | Duty ratio                                                          | -                  |

| d              | Half length of the i-region in an PiN diode                         | cm                 |

| $D_a$          | Ambipolar diffusion coefficient                                     | $cm^2 s^{-1}$      |

| $d_N$          | N drift region width in an IGBT                                     | cm                 |

| di <sub>r</sub> /dt | Reverse current gradient during a diode turn off transient        | A/ns               |

|---------------------|-------------------------------------------------------------------|--------------------|

| e                   | Elementary charge, 1.60×10 <sup>-19</sup>                         | C                  |

| $E_{on}$            | Switch-on energy loss                                             | J                  |

| $E_{off}$           | Switch -off energy loss                                           | J                  |

| $f_{l}$             | Fundamental frequency                                             | Hz                 |

| $f_s$               | Switching frequency in a converter                                | Hz                 |

| $f_c$               | Corner frequency of an low pass filter                            | Hz                 |

| $f_{cmax}$          | Max value for the corner frequency                                | Hz                 |

| $g_{ms}$            | IGBT transconductance                                             | $\mathbf{S}$       |

| $i_{CE}$            | IGBT collector- emitter current                                   | A                  |

| $I_{CE}$            | IGBT collector- emitter steady-state current                      | A                  |

| $I_{CE}(0)$         | IGBT collector- emitter current value after initial drop during a | A                  |

| ī                   | turn-off transient                                                | <b>A</b>           |

| $I_{CE(ON)}$        | IGBT collector- emitter on-state current                          | A                  |

| $I_{CE, sat}$       | IGBT saturated collector- emitter current                         | A                  |

| $i_{CE}(t)$         | IGBT tail current                                                 | A                  |

| $I_{MOS}$           | MOS component current in an IGBT                                  | A                  |

| $I_{PiN}$           | PiN component current in an IGBT                                  | A                  |

| $I_d$               | Diode current                                                     | A                  |

| $I_e$               | The electron current component in an IGBT                         | A                  |

| $I_{e,lin}$         | The linear electron current component in an IGBT                  | A                  |

| $I_{e,sat}$         | The saturate electron current component in an IGBT                | A                  |

| $I_F$               | Diode forward current during on-state                             | A                  |

| $I_{FO}$            | Diode forward current before turn off process                     | A                  |

| $I_{GE}$            | Gate-emitter current                                              | A                  |

| $I_h$               | The hole current component in an IGBT                             | A                  |

| $i_L$               | Inductor current                                                  | A                  |

| $I_L$               | Average value of the inductor current                             | A                  |

| $I_{rrm}$           | Diode peak reverse recovery current                               | A                  |

| $I_R$               | Reverse bias current                                              | μΑ                 |

| $I_S$               | Diode reverse leak current                                        | A                  |

| k                   | Boltzmann constant, $1.3806503 \times 10^{-23}$                   | J K <sup>-1</sup>  |

| $J_C$               | Collector current density in an IGBT                              | A cm <sup>-2</sup> |

| $J_{PiN}$           | Current density in the PiN component of an IGBT                   | A cm <sup>-2</sup> |

| $J_{MOS}$           | Current density in the MOS component of an IGBT                   | A cm <sup>-2</sup> |

| K                   | Parameter for the voltage controlled current source in the diode  | -                  |

|                     | reverse recovery model                                            |                    |

| $K_{plin}$          | Transconductance in the linear region                             | $AV^{-2}$          |

| $K_{psat}$          | Transconductance in the saturation region                         | $AV^{-2}$          |

| l                   | Length of bus bars                                                | cm                 |

| L                   | Inductor used in the diode reverse recovery model                 | Н                  |

| $L_t$               | Total stray inductance of two bus bars                            | Н                  |

| $L_i$               | Internal inductance of two bus bars                               | H                  |

| $L_e$               | External inductance of two bus bars                               | H                  |

| $L_f$               | Inductance in the low-pass filter for the buck converter          | Н                  |

| $\stackrel{'}{L_a}$ | Ambipolar diffusion length                                        | cm                 |

| $L_p^a$             | Minority carrier diffusion length                                 | cm                 |

| $L_{CH}^{ ho}$      | The gate channel length for an IGBT or MOSFET                     | cm                 |

| 1.6                                                 | A 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                               |                  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------|

| M                                                   | Avalanche multiplication coefficient                                                                  | -                |

| $m_a$                                               | Depth of amplitude modulation                                                                         | -                |

| $m_f$                                               | Depth of frequency modulation                                                                         | <del>-</del>     |

| n                                                   | Electron concentration                                                                                | cm <sup>-3</sup> |

| n(+d)                                               | Electron concentration at –d end in the i-region of a PiN diode                                       | cm <sup>-3</sup> |

| n(-d)                                               | Electron concentration at +d end in the i-region of a PiN diode                                       | cm <sup>-3</sup> |

| $N_d$                                               | Doping concentration in the drift region                                                              | cm <sup>-3</sup> |

| $n_{e\!f\!f}$                                       | Emitter efficiency                                                                                    | %                |

| $n_i$                                               | Intrinsic carrier concentration                                                                       | cm <sup>-3</sup> |

| p                                                   | Hole concentrations                                                                                   | cm <sup>-3</sup> |

| $Q_{CE}$                                            | Collector-emitter charge                                                                              | C                |

| $Q_{GC}$                                            | Gate-collector charge                                                                                 | C                |

| $Q_{GE}$                                            | Gate-emitter charge                                                                                   | C                |

| $Q_{GE(th)}$                                        | Threshold gate-emitter charge                                                                         | C                |

| $Q_{rr}$                                            | Diode reverser recovery charge                                                                        | C                |

| R                                                   | Buck converter load                                                                                   | $\Omega$         |

| $R_C$                                               | Collector resistance                                                                                  | Ω                |

| $R_E$                                               | Emitter resistance                                                                                    | $\Omega$         |

| $R_G$                                               | Gate resistance                                                                                       | Ω                |

| $R_L$                                               | Resistor used in the diode reverse recovery model                                                     | Ω                |

| $R_{on}$                                            | Diode on state resistance                                                                             | Ω                |

| S                                                   | Snappiness factor                                                                                     | _                |

| T                                                   | Absolute temperature                                                                                  | K                |

| t                                                   | Time                                                                                                  | S                |

| $t_{\scriptscriptstyle S}$                          | The moment at which the diode reverse current reaches its peak                                        | S                |

| $t_3$                                               | value Time duration for the diode current dropping from on-state to                                   | S                |

|                                                     | zero                                                                                                  |                  |

| $t_4$                                               | Time duration for the diode current dropping from zero to the peak reverse current                    | S                |

| $t_5$                                               | Time duration for the diode current reverse recovering from the peak reverse current to its 10% value | S                |

| t                                                   | Time duration when the converter switch is on                                                         | c                |

| $t_{on} \ t_{off}$                                  | Time duration when the converter switch is off                                                        | S<br>S           |

| $T_S$                                               | Converter switching time period                                                                       | S                |

| $t_{rr}$                                            | Diode reverse recovery time                                                                           | S                |

| $V_B$                                               | Breakdown voltage                                                                                     | V                |

| $V_{bi}$                                            | Junction built- in potential                                                                          | V                |

| $V_I$                                               | Voltage between the collector-gate depletion region                                                   | V                |

| $V_2$                                               | Voltage between the collector-emitter depletion region                                                | V                |

| $V_b$                                               | Junction barrier potential in a diode                                                                 | V                |

| $V_{CCI}$                                           | Voltage across the collector resistor used in the IGBT model                                          | V                |

| $V_{CC}$                                            | Power supply voltage amplitude                                                                        | V                |

| $V_{CE}$                                            | Collector- emitter voltage                                                                            | V                |

| $V_{control}^{CE}$                                  | Amplitude of the control signal for PWM                                                               | V                |

| $V_{dc}^{control}$                                  | DC input voltage for an converter or inverter leg                                                     | V                |

| $V_{dc}$                                            | Diode voltage                                                                                         | V                |

| $\stackrel{\scriptstyle V}{\scriptstyle d}_{diode}$ | Voltage across the temperature sensor diode                                                           | V                |

| r diode                                             | vortage across the temperature sensor aloue                                                           | Y                |

| $V_{FP}                                    $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $V_{EE1}$          | Voltage across the emitter resistor used in the IGBT model | V  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------|----|

| Very         Overshoot voltage during a PiN diode turn-on transient         V           Voltage across the gate resistor used in the IGBT model         V           Very         Gate-emitter voltage for an IGBT         V           Very         Gate-emitter threshold voltage         V           Valuate across the emitter of the device to conduct a full load current         V           Very         Voltage across the inductor in the buck converter         V           Valuate of the converter of the converter overser recovery model         V           Valuate across the inductor in the buck converter         V           Valuage across the inductor in the buck converter         V           Valuage across the inductor in the buck converter         V           Valuage across the inductor in the buck converter         V           Valuage across the inductor in the buck converter         V           Valuate of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $V_F$              |                                                            |    |

| Volcage         Gate-collector voltage         V           Voltage across the gate resistor used in the IGBT model         V           Volge         Gate-emitter voltage for an IGBT         V           General Gate-emitter threshold voltage         V           General Gate-emitter threshold voltage         V           Voltage Gate voltage necessary for the device to conduct a full load current         V           Voltage Instantaneous voltage across the inductor in the buck converter V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the inductor in the diode reverse recovery model V         V           Voltage drop across the Inductor in the diode reverse recovery model V         V           Vontage drop across the Inductor in the diode reverse dovernal GBT         V           Voltage drop across the Phregion in a PiN diode V         V           Vore Collecto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                  |                                                            |    |

| $V_{GGI}$ Voltage across the gate resistor used in the IGBT model         V $V_{GE}$ Gate-emitter voltage for an IGBT         V $V_{GP}$ Gate-emitter threshold voltage         V $V_{CP}$ Gate voltage necessary for the device to conduct a full load current         V $V_{I}$ Diode junction voltage         V $V_{I}$ Diode junction voltage across the inductor in the buck converter         V $V_{I}$ Voltage across the inductor in the diode reverse recovery model         V $V_{I}$ Voltage across the inductor in the diode reverse recovery model         V $V_{I}$ Voltage across the inductor in the diode reverse recovery model         V $V_{I}$ Voltage drop across the inegion of a PiN diode         V $V_{I}$ Voltage drop across the MOSFET component of an IGBT         V $V_{I}$ Voltage drop across the N+ region in a PiN diode         V $V_{I}$ Voltage across filter         V $V_{I}$ Voltage         V $V_{I}$ Voltage         V $V_{I}$ Voltage         V $V_{I}$ Voltage for pha across the P+ region in an PiN d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |                                                            |    |

| GE Gate-emitter voltage for an IGBT V GE(GB) Gate-emitter threshold voltage V GP Gate voltage necessary for the device to conduct a full load current GI Diode junction voltage Instantaneous voltage across the inductor in the buck converter V VV Voltage across the inductor in the diode reverse recovery model V Maximum reverse blocking voltage of the IGBT N- drift region V Motor Voltage drop across the i- region of a PiN diode V Maximum reverse blocking voltage of the IGBT N- drift region V Motor Voltage drop across the NP+ region in a PiN diode V Motor Voltage drop across the NP+ region in a PiN diode V Motor Instantaneous value for the converter output voltage before the low-pass filter Motor Instantaneous value for the converter output voltage before the low-pass filter Motor Voltage The amplitude of the converter output voltage V Motor Collector emitter offset voltage for an IGBT V Motor Voltage signal in the temperature regulation circuit V Motor Voltage across the P+ region in an PiN diode V Motor Voltage across the P+ region in an PiN diode V Motor Voltage across the PiN component of an IGBT V Motor Voltage across the PiN component of an IGBT V Motor Voltage across the PiN component of an IGBT V Motor Voltage across the PiN component of an IGBT V Motor Voltage across the PiN component of an IGBT V Motor Voltage across the PiN component of an IGBT V Motor Voltage across the pin component of an IGBT or MOSFET Motor Temperature demand voltage signal in the temperature regulation circuit V Motor Temperature demand voltage across a diode V Motor Temperature demand volt |                    | <u> </u>                                                   |    |

| Gate (GEth)         Gate-emitter threshold voltage         V $V_{GP}$ Gate voltage necessary for the device to conduct a full load current         V $V_{II}$ Diode junction voltage         V $V_{II}$ Unstantaneous voltage across the inductor in the buck converter V         V $V_{II}$ Voltage drop across the inductor in the diode reverse recovery model V         V $V_{II}$ Voltage drop across the inductor in the GIGBT N- drift region V         Voltage drop across the inductor in the GIGBT N- drift region V $V_{II}$ Woltage drop across the MOSFET component of an IGBT V         V $V_{II}$ Voltage drop across the N+ region in a PiN diode V         V $V_{II}$ Voltage drop across the N+ region in a PiN diode V         V $V_{II}$ Instantaneous value for the converter output voltage before the low-pass filter         V $V_{II}$ Fundamental frequency amplitude of the converter output voltage before the low-pass filter         V $V_{II}$ Fundamental frequency amplitude of the converter output voltage before the low-pass filter         V $V_{II}$ Fundamental frequency amplitude of the converter output voltage V         V $V_{II}$ Fundamental frequency amplitude of the converter output voltage V <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |                                                            |    |

| Gep Gate voltage necessary for the device to conduct a full load current  Vi Diode junction voltage  Instantaneous voltage across the inductor in the buck converter V  VI Voltage across the inductor in the diode reverse recovery model V  VI Voltage drop across the i- region of a PiN diode V  Voltage drop across the i- region of a PiN diode V  Voltage drop across the MOSFET component of an IGBT V  Voltage drop across the MOSFET component of an IGBT V  Voltage drop across the N+ region in a PiN diode V  Voltage drop across the N+ region in a PiN diode V  Voltage drop across the N+ region in a PiN diode V  Instantaneous value for the converter output voltage before the low-pass filter  Voilage  The amplitude of the converter output voltage V  Instantaneous value for the converter output voltage V  Voltage The amplitude of the converter output voltage V  Voltage The amplitude of the converter output voltage V  Voltage Tout Voltage signal in the temperature regulation circuit V  Voltage across the P+ region in an PiN diode V  Verby Voltage across the PiN component of an IGBT V  Reference voltage used in the temperature regulation circuit V  Reference voltage used in the temperature regulation circuit V  Reference voltage used in the temperature regulation circuit V  Reference voltage used in the temperature regulation circuit V  Reference voltage used in the temperature regulation circuit V  Reference voltage used in the temperature regulation circuit V  Reference voltage used in the temperature regulation circuit V  Reference voltage for the accumulation layer in an IGBT or MOSFET  Vortage Threshold voltage for the accumulation layer in an IGBT or V  MOSFET  Gate threshold voltage for an IGBT or MOSFET C  Vortage Collector-gate depletion depth cm  Gate width for an IGBT or MOSFET cm  Collector-gate depletion depth cm  Gate depth for an IGBT or MOSFET cm  Impedance of the inverter load  Common-base current gain of a transistor                                                                                           |                    | <u> </u>                                                   |    |

| Current Diode junction voltage V L Instantaneous voltage across the inductor in the buck converter V L Voltage across the inductor in the diode reverse recovery model V M Voltage drop across the i- region of a PiN diode V M Woltage drop across the i- region of a PiN diode V M Voltage drop across the MOSFET component of an IGBT V V N+ Voltage drop across the MOSFET component of an IGBT V V N+ Voltage drop across the N+ region in a PiN diode V Instantaneous value for the converter output voltage before the low-pass filter V Instantaneous value for the converter output voltage before the low-pass filter V Instantaneous value for the converter output voltage V Instantaneous value for the temperature regulation circuit V Instantaneous value for the te |                    | <u> </u>                                                   |    |

| Diode junction voltage   V   Instantaneous voltage across the inductor in the buck converter   V   Voltage across the inductor in the diode reverse recovery model   V   Voltage drop across the i-region of a PiN diode   V   Voltage drop across the inductor in the IGBT N- drift region   V   Voltage drop across the MOSFET component of an IGBT   V   Voltage drop across the MOSFET component of an IGBT   V   Voltage drop across the N+ region in a PiN diode   V   Voltage drop across the N+ region in a PiN diode   V   Voltage drop across the N+ region in a PiN diode   V   Instantaneous value for the converter output voltage before the low-pass filter   V   Voltage   V   Voltage   V   Instantaneous value for the converter output voltage   V   Voltage   V   Instantaneous value for the converter output voltage   V   Voltage   V   Voltage   V   Instantaneous value for the converter output voltage   V   Voltage   V   Voltage drop across the P+ region in an PiN diode   V   Voltage   V   Voltage across the P+ region in an PiN diode   V   Voltage   V   Voltage across the PiN component of an IGBT   V   Voltage   V   Voltage across the PiN component of an IGBT   V   Voltage    | V GP               | · · · · · · · · · · · · · · · · · · ·                      | V  |

| Instantaneous voltage across the inductor in the buck converter   V   Voltage across the inductor in the diode reverse recovery model   V   Voltage across the inductor in the diode reverse recovery model   V   Voltage across the inductor in the diode reverse recovery model   V   Voltage drop across the inductor in the diode reverse recovery model   V   Voltage drop across the MOSFET component of an IGBT   V   Voltage drop across the MOSFET component of an IGBT   V   Voltage drop across the N+ region in a PiN diode   V   Voltage drop across the N+ region in a PiN diode   V   Voltage drop across the region in a PiN diode   V   Instantaneous value for the converter output voltage before the low-pass filter   V   Voltage    | $V_i$              |                                                            | V  |

| VL         Voltage across the inductor in the diode reverse recovery model         V           VL         Voltage drop across the i- region of a PiN diode         V           VMOS         Voltage drop across the i- region of a PiN diode         V           VMOS         Voltage drop across the MOSFET component of an IGBT         V           Von         Diode turn- on voltage, corresponding to a current of 1 A         V           Von         Instantaneous value for the converter output voltage before the low-pass filter         V           Von         Fundamental frequency amplitude of the converter output voltage before the low-pass filter         V           Von         The amplitude of the converter output voltage before the low-pass filter         V           Von         That amplitude of the converter output voltage before the low-pass filter         V           Von         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Voltage signal in the temperature regulation circuit         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | · · · · · · · · · · · · · · · · · · ·                      | V  |

| V/M         Voltage drop across the i- region of a PiN diode         V           V/m         Maximum reverse blocking voltage of the IGBT N- drift region         V           V/MOS         Voltage drop across the MOSFET component of an IGBT         V           V/N+         Voltage drop across the N+ region in a PiN diode         V           Von         Diode turn- on voltage, corresponding to a current of 1 A         V           Vol         Instantaneous value for the converter output voltage before the low-pass filter         V           Voil         Fundamental frequency amplitude of the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Voltage drop across the Pin converter output voltage         V           Voltage drop across the Pin converter output voltage         V         V           Voltage drop across the Pin converter output volta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    | <del>_</del>                                               |    |

| V         Maximum reverse blocking voltage of the IGBT N- drift region         V           V         V         Voltage drop across the MOSFET component of an IGBT         V           V         Voltage drop across the N+ region in a PiN diode         V           Vol         Diode turn- on voltage, corresponding to a current of 1 A         V           Vol         Instantaneous value for the converter output voltage before the low-pass filter         V           Vol1         Fundamental frequency amplitude of the converter output voltage before the voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Instantaneous value for the converter output voltage         V           Vol         Voltage drop across the P+ region in a PiN diode         V           Very                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                                                            |    |

| $V_{N+}$ Voltage drop across the MOSFET component of an IGBT         V $V_{N+}$ Voltage drop across the N+ region in a PiN diode         V $V_{OI}$ Diode turn- on voltage, corresponding to a current of 1 A         V $V_{OI}$ Instantaneous value for the converter output voltage before the low-pass filter         V $V_{OI}$ Fundamental frequency amplitude of the converter output voltage         V $V_O$ The amplitude of the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Unity voltage signal in the temperature regulation circuit         V $V_O$ Reference voltage used in the temperature regulation circuit         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                    |                                                            |    |

| $V_{N+}$ Voltage drop across the N+ region in a PiN diode         V $V_{On}$ Diode turn- on voltage, corresponding to a current of 1 A         V $V_{Ol}$ Instantaneous value for the converter output voltage before the low-pass filter         V $V_{Ol}$ Fundamental frequency amplitude of the converter output voltage         V $V_O$ The amplitude of the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Instantaneous value for the converter output voltage         V $V_O$ Voltage across the PiN converter output voltage         V $V_P$ Voltage across the PiN converter output voltage         V $V_P$ Voltage across the PiN conponent of an IGBT         V $V_P$ Voltage across the PiN component of an IGBT         V $V_P$ Voltage across th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                                            |    |

| Von         Diode turn- on voltage, corresponding to a current of 1 A         V           Voi         Instantaneous value for the converter output voltage before the low-pass filter         V           Voi)1         Fundamental frequency amplitude of the converter output voltage         V           Vo         The amplitude of the converter output voltage         V           Vo         Instantaneous value for the converter output voltage         V           Vo         Collector emitter offset voltage for an IGBT         V           Vout         Output voltage signal in the temperature regulation circuit         V           Vp+         Voltage drop across the P+ region in an PiN diode         V           Vp+         Voltage across the PiN component of an IGBT         V           Ve         Reference voltage used in the temperature regulation circuit         V           Vset         Temperature demand voltage signal in the temperature         V           Vset         Temperature demand voltage signal in the temperature         V           Vset         Temperature demand voltage signal in the temperature         V           Vset         Temperature demand voltage signal in the temperature         V           Vset         Temperature demand voltage signal in the temperature         V           Vset         Temperature demand voltage sig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                                            |    |

| Instantaneous value for the converter output voltage before the low-pass filter $V_{oi}$ ) Fundamental frequency amplitude of the converter output voltage $V_{o}$ The amplitude of the converter output voltage $V_{o}$ Instantaneous value for the converter output voltage $V_{o}$ Instantaneous value for the converter output voltage $V_{o}$ Collector emitter offset voltage for an IGBT $V_{out}$ Output voltage signal in the temperature regulation circuit $V_{P+}$ Voltage drop across the P+ region in an PiN diode $V_{PiN}$ Voltage across the PiN component of an IGBT $V_{o}$ Reference voltage used in the temperature regulation circuit $V_{o}$ Set $V_{o}$ Temperature demand voltage signal in the temperature  regulation circuit $V_{o}$ Reverse blocking voltage $V_{o}$ Reverse recovery peak voltage across a diode $V_{o}$ Threshold voltage for the accumulation layer in an IGBT or $V_{o}$ MOSFET $V_{o}$ Gate threshold voltage for an IGBT or MOSFET $V_{o}$ Amplitude of the triangular signal for PWM $V_{o}$ Width of the bus bars $V_{o}$ Gate width for an IGBT or MOSFET $V_{o}$ Collector-emitter depletion width $V_{o}$ Collector-gate depletion depth $V_{o}$ Gate depth for an IGBT or MOSFET $V_{o}$ Collector-gate depletion depth $V_{o}$ Gate depth for an IGBT or MOSFET $V_{o}$ Collector-gate depletion depth $V_{o}$ Gate depth for an IGBT or MOSFET $V_{o}$ Collector-gate depletion depth $V_{o}$ Collector-gate de                                           |                    |                                                            |    |