# Acceleration of the Discrete Element Method on a Reconfigurable Co-processor

by

Benjamin Carrión Schäfer

A thesis submitted to the School of Engineering of

The University of Birmingham

for the degree of

DOCTOR OF PHILOSOPHY

School of Engineering

Department of Electronic, Electrical and Computer Engineering

The University of Birmingham

February 2002

### **Abstract**

Granular materials are important for many different disciplines, e.g. geomechanics, civil engineering and chemical engineering. Many approaches have been used to model their behaviour, but one of the best and most important is the Discrete Element Method (DEM). The DEM was first developed during the 70's, but its widespread use has been hampered by its extremely computationally demanding nature.

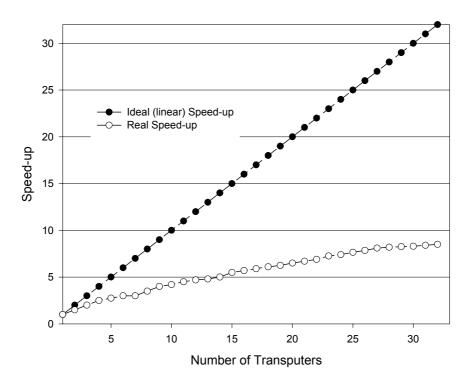

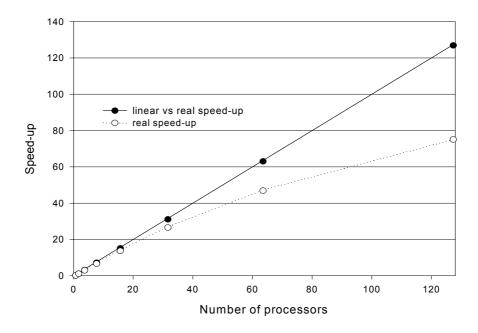

The DEM can be run on a parallel computer by farming out different sub-domains onto different processors. However, particles transiting from one sub-domain to another create communication and synchronisation overheads which limit the speed-up achieved by parallel processing. Also, if some cells become much more heavily populated than others, then there will be inefficiencies due to load imbalance between the processors. As a result of these effects, the speed-up achieved by running the DEM on parallel processor computers is far less than linear.

This thesis describes work on the acceleration of the DEM using reconfigurable computing. A custom hardware architecture for the DEM has been designed and implemented on a Field Programmable Gate Array (FPGA) mounted on a reconfigurable computing card. The design exploits the low level parallelism of the DEM by using long, wide computational pipelines that compute many arithmetic operations concurrently. It also exploits the high level parallelism by overlapping the main computational tasks using domain decomposition techniques. Speed-ups of a factor of at least 30 per FPGA have been achieved for simulations involving 25,000 to 200,000 particles. A multi-FPGA system has been implemented that allows the full overlap of computation with communication, so that an almost linear speed-up can be achieved as the number of FPGAs is increased. The effect of the short wordlength arithmetic used in the FPGA has been investigated, and the accuracy of the simulations has been found to be acceptable.

To my brother Norbert,

Thank you very much for everything

## **Acknowledgments**

This research has been supported financially by the University of Birmingham's interdisciplinary research fund, the Department of Electronic, Electrical and Computer Engineering and the Department of Civil Engineering.

I would first of all like to thanks my two supervisors Dr. Andrew H.C. Chan and Dr. Steven F. Quigley for all their support. Thank you very much for everything, which is quite a lot.

I would also want to thank Dr. Alonso Corona and Dr. Ignacio Llamas for their friendship. This would have not been the same without them.

To all the colleagues in room 439. Thank you very much for making the time spent in Birmingham so enjoyable.

Last but far from least, thank you very much to my family for their support from the far distance.

# **Contents**

| $\mathbf{CH}$ | APTER 1 INTRODUCTION                             | 1  |

|---------------|--------------------------------------------------|----|

| 1.1           | INTRODUCTION                                     | 1  |

| 1.2           | CONTRIBUTION OF THIS THESIS                      | 3  |

| 1.3           | THESIS ORGANISATION                              | 4  |

| 1.4           | REFERENCES                                       | 7  |

| <u>СН</u> 2   | APTER 2 THE DISCRETE ELEMENT METHOD              | 8  |

| 2.1           | INTRODUCTION                                     | 8  |

| 2.2           | ANALYSIS OF THE BEHAVIOUR OF GRANULAR MEDIA      | 10 |

| 2.3           | SIMULATIONS                                      | 10 |

| 2.4           | ADVENT OF THE DISCRETE ELEMENT METHOD (DEM)      | 12 |

| 2.5           | CONCEPTS OF THE DISCRETE ELEMENT MEHTOD          | 13 |

| 2.6           | DEM ANALYSIS                                     | 17 |

| 2.7           | PARALLEL ANALYSIS                                | 24 |

| 2.8           | SUMMARY AND CONCLUSIONS                          | 28 |

| 2.9           | REFERENCES                                       | 30 |

| <u>СН</u>     | APTER 3 SOFTWARE IMPLEMENTATION OF THE DEM       | 32 |

| 3.1           | INTRODUCTION                                     | 32 |

| 3.2           | INITIALISATION OF THE SIMULATION                 | 34 |

| 3.3           | SIMULATOR FEATURES                               | 42 |

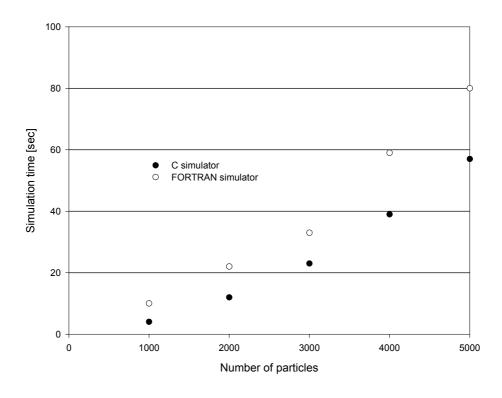

| 3.4           | RUNTIME COMPARISON BETWEEN THE FORTRAN AND THE C | 45 |

|               | SIMULATOR                                        |    |

| 3.5           | VALIDATION OF THE SIMULATOR                      | 47 |

| 3.6           | DISCUSSION                                       | 49 |

| 3.7           | SUMMARY AND CONCLUSIONS                          | 50 |

| 3.8           | REFERENCES                                       | 50 |

| <u>CHA</u> | APTER 4 REVIEW AND ANALYSIS OF PARALLEL DEM IMPLEMENTATIONS | <u>52</u> |

|------------|-------------------------------------------------------------|-----------|

| 4.1        | INTRODUCTION                                                | 52        |

| 4.2        | BASIC IDEAS ABOUT PARALLELISM                               | 53        |

| 4.3        | PARALLEL DEM IMPLEMENTATIONS                                | 57        |

| 4.4        | MODELLING OF A MULTIPROCESSOR SYSTEM                        | 69        |

| 4.5        | SUMMARY OF THE PARALLEL DEM IMPLEMENTATIONS                 | 79        |

| 4.6        | USE OF FIELD PROGRAMMABLE GATE ARRAYS FOR THE DEM           | 80        |

| 4.7        | SUMMARY AND CONCLUSIONS                                     | 81        |

| 4.8        | REFERENCE                                                   | 82        |

| <u>CHA</u> | APTER 5 HARDWARE IMPLEMENTATION OF THE DEM ON A FPGA        | 84        |

| 5.1        | INTRODUCTION                                                | 84        |

| 5.2        | MOTIVATION                                                  | 85        |

| 5.3        | FIELD PROGRAMMABLE GATE ARRAYS (FPGAS)                      | 85        |

| 5.4        | RECONFIGURABLE COMPUTING PLATFORM                           | 89        |

| 5.5        | HARDWARE IMPLEMENTATIONS                                    | 91        |

| 5.6        | DATA FORMAT                                                 | 93        |

| 5.7        | IMPLEMENTATION CLASSIFICATIONS                              | 95        |

| 5.8        | LOW LEVEL PARALLELISM IMPLEMENTATION                        | 95        |

| 5.9        | HIGH AND LOW LEVEL IMPLEMENTATION                           | 104       |

| 5.10       | VALIDATION OF THE HARDWARE DESIGNS                          | 120       |

| 5.11       | DISCUSSION                                                  | 124       |

| 5.12       | SUMMARY AND CONCLUSIONS                                     | 125       |

| 5.13       | REFERENCES                                                  | 127       |

| <u>CHA</u> | APTER 6 SOFTWARE AND HARDWARE ANALYSIS                      | 128       |

| 6.1        | INTRODUCTION                                                | 128       |

| 6.2        | SPEED-UP                                                    | 129       |

| 6.3        | DATA PRECISION                                              | 133       |

| 6.4        | ERRORS IN ARITHMETIC OPERATIONS                             | 137       |

| 6.5        | ERROR PROPAGATION IN COMPUTER ARITHMETIC                    | 140       |

| 6.6        | ARITHMETIC ERROR ANALYSIS OF TE HARDWARE IMPLEMENTATION     | 145  |

|------------|-------------------------------------------------------------|------|

| 6.7        | COMPARISON OF BULK ERRORS IN SW AND HW                      | 155  |

| 6.8        | DISCUSSION                                                  | 166  |

| 6.9        | SUMMARY AND CONCLUSIONS                                     | 168  |

| 6.10       | REFERENCES                                                  | 168  |

|            |                                                             |      |

| <u>CHA</u> | APTER 7 SUITABILITY OF THE HW DESIGN FOR A MORE COMPLEX DEM | 170  |

| 7.1        | INTRODUCTION                                                | 170  |

| 7.2        | INSERTION OF WALLS                                          | 171  |

| 7.3        | MULTIPLE RADII                                              | 182  |

| 7.4        | 3-DIMENSIONS                                                | 185  |

| 7.5        | SUMMARY AND CONCLUSIONS                                     | 200  |

| 7.6        | REFERENCES                                                  | 201  |

|            |                                                             |      |

| <u>CHA</u> | APTER 8 SCALABLE AND ALTERNATIVE IMPLEMENTATIONS OF THE DEM | 202  |

| 8.1        | INTRODUCTION                                                | 202  |

| 8.2        | MULTI-FPGA DISTRIBUTED MEMORY SYSTEM                        | 203  |

| 8.3        | SHARED MEMORY SYSTEM                                        | 2012 |

| 8.4        | ALTERNATIVE SINGLE FPGA IMPLEMENTATION                      | 215  |

| 8.5        | SUMMARY AND CONCLUSIONS                                     | 227  |

| 8.6        | REFERENCES                                                  | 228  |

|            |                                                             |      |

| <u>CHA</u> | APTER 9 CONCLUSIONS AND FUTURE WORK                         | 229  |

| 9.1        | CONCLUSIONS                                                 | 229  |

| 9.2        | FUTURE WORK                                                 | 233  |

|            |                                                             |      |

# Appendix A.1: Publication List

# **Table of Figures**

| CHAPTER 2THE DISCRETE ELEMENT METHOD (DEM)                                                                                                                        | 8              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 2–1 Examples of Storage and transportation of granular media                                                                                               | 9              |

| Figure 2–2 Dem Flow chart                                                                                                                                         | 13             |

| Figure 2–3 Balls in contact                                                                                                                                       | 14             |

| Figure 2–4 Screenshots of two system (without and with grid)                                                                                                      | 17             |

| Figure 2–5 Modified DEM flow chart with domain decomposition                                                                                                      | 18             |

| Figure 2–6 Two cases if different number of balls in contact                                                                                                      | 19             |

| Figure 2–7 Geometrical deduction of the maximum number of balls in contact for                                                                                    | 22             |

| balls of same radius                                                                                                                                              |                |

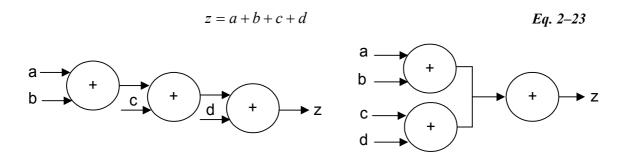

| Figure 2–8 Graphical representation of the force update equations                                                                                                 | 25             |

| Figure 2–9 Example of a serial and parallel graphical representation of an algorithm                                                                              | 25             |

| Figure 2–10 Graphical representation of the position update equations                                                                                             | 26             |

| Figure 2–11 Examples of domain decomposition in order to make use of the high level                                                                               | 27             |

| parallelism of the DEM                                                                                                                                            |                |

|                                                                                                                                                                   |                |

| CHAPTER 3 SOFTWARE IMPLEMENTATION OF THE DEM                                                                                                                      | 32             |

| Figure 3–1 DEM Flow chart                                                                                                                                         | 34             |

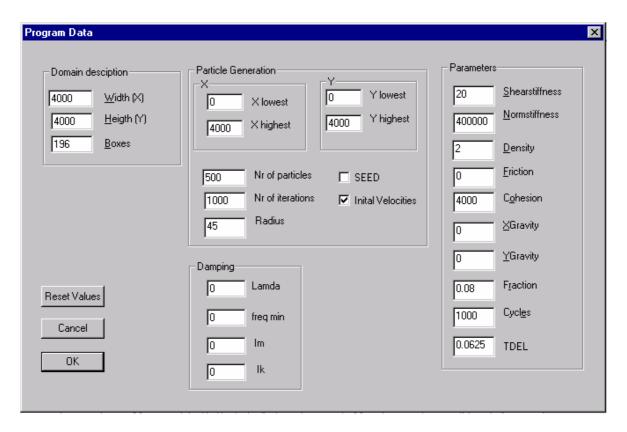

| Figure 3–2 Example of the simulator initialisation file                                                                                                           | 35             |

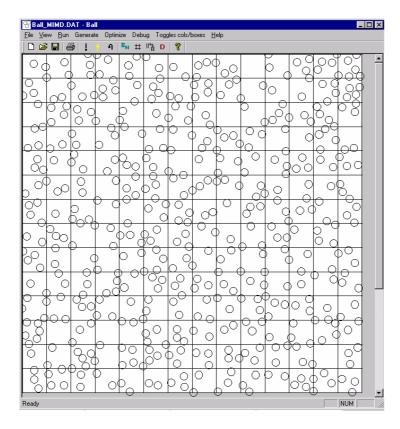

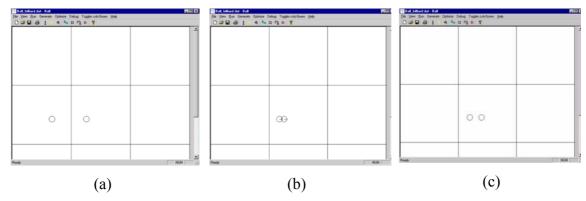

| Figure 3–3 Screenshots of the simulators initial data after the particles have been                                                                               | 38             |

| generated                                                                                                                                                         |                |

| Figure 3–4 Screenshots of an initial state of the simulator after reading in the data file                                                                        | 39             |

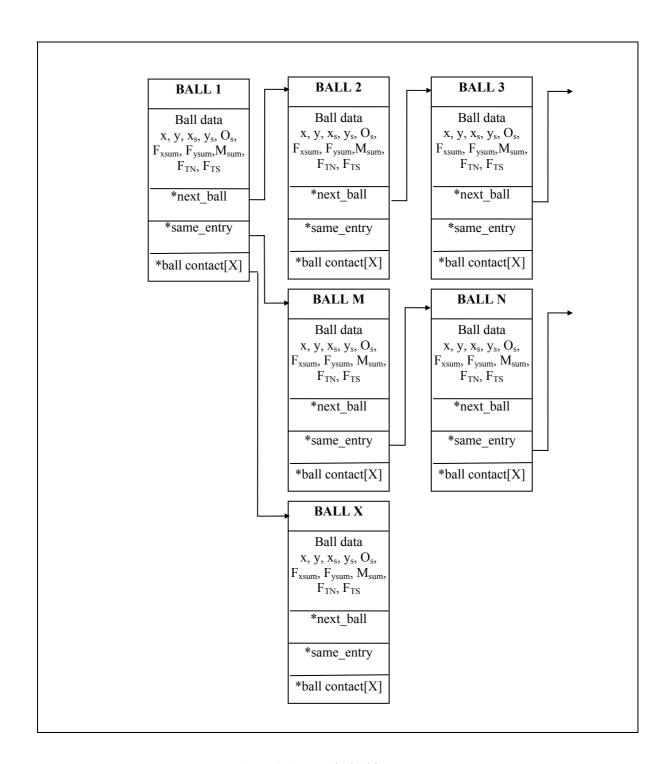

| Figure 3–5 Data structure of the particles                                                                                                                        | 40             |

|                                                                                                                                                                   |                |

| Figure 3–6 Data linked list structure                                                                                                                             | 41             |

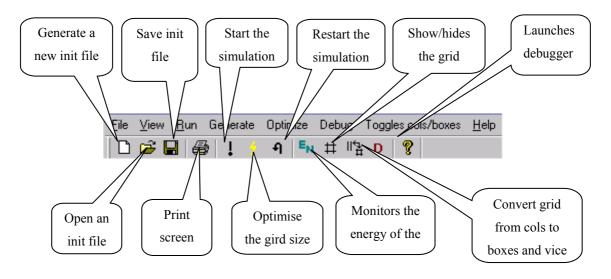

| Figure 3–6 Data linked list structure  Figure 3–7 Simulator's tool bar                                                                                            | 41<br>42       |

|                                                                                                                                                                   |                |

| Figure 3–7 Simulator's tool bar                                                                                                                                   | 42             |

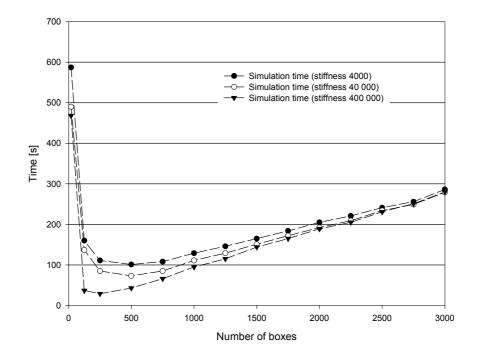

| Figure 3–7 Simulator's tool bar  Figure 3–8 Run time graph as a function of the number of boxes                                                                   | 42             |

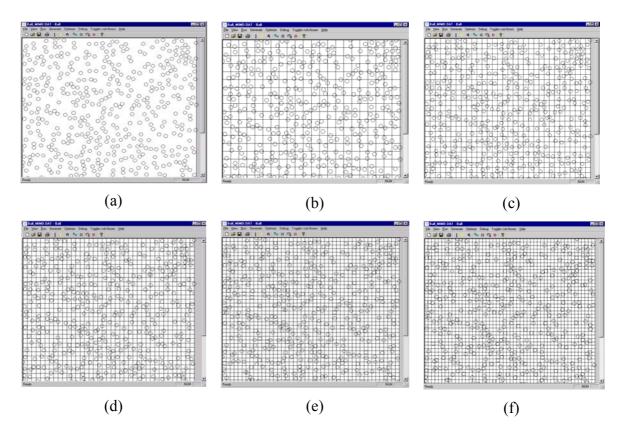

| Figure 3–7 Simulator's tool bar  Figure 3–8 Run time graph as a function of the number of boxes  Figure 3–9 Screenshot of the simulator with different grid sizes | 42<br>43<br>44 |

| Figure 3–13 Initial and final state of the simulation                                | 48        |

|--------------------------------------------------------------------------------------|-----------|

| CHAPTER 4 REVIEW AND ANALYSIS OF PARALLEL DEM IMPLEMENTATIONS                        | <u>52</u> |

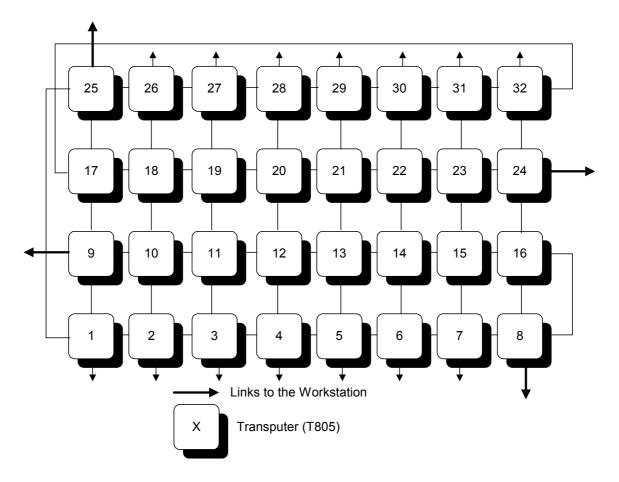

| Figure 4–1 Transputer Network Configuration                                          | 58        |

| Figure 4–2 Pseudo Code for the Multi processor systems                               | 59        |

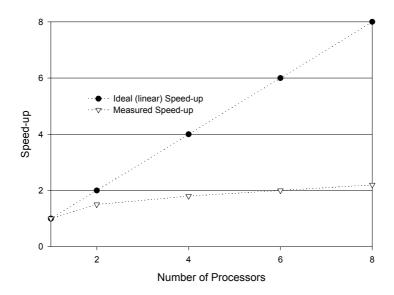

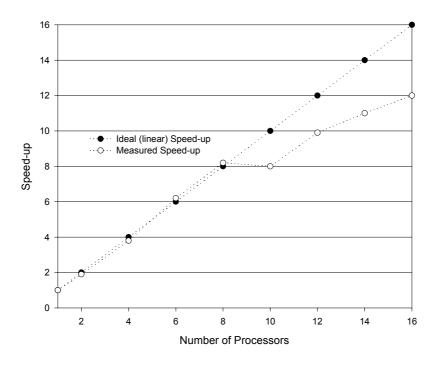

| Figure 4–3 Measured speed-up                                                         | 60        |

| Figure 4–4 Speed-up of the parallel implementation as a function of the number of    | 62        |

| processors                                                                           |           |

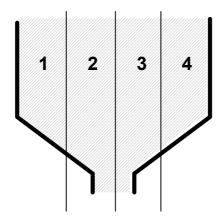

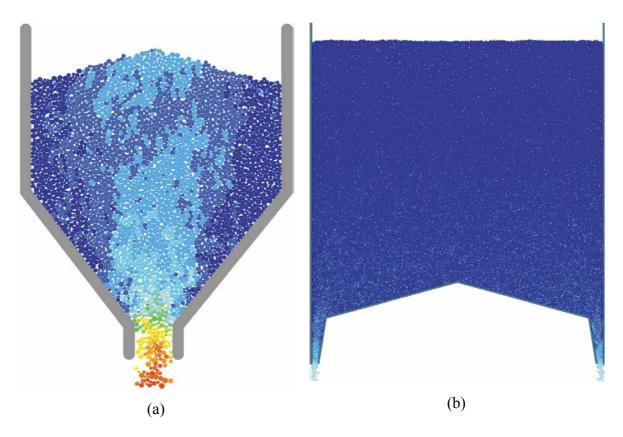

| Figure 4–5 Domain decomposition for the Hopper discharge                             | 63        |

| Figure 4–6 Single-port and dual-port hopper                                          | 64        |

| Figure 4–7 Computation time required for the individual tasks of the DEM simulation  | 65        |

| of the single-port hopper                                                            |           |

| Figure 4–8 Computation time required for the individual tasks of the DEM simulation  | 65        |

| of the dual-port hopper                                                              |           |

| Figure 4–9 Measured speed-up for the DEM simulations of the single-port hopper       | 66        |

| Figure 4–10 Measured speed-up for the DEM simulations for the dual-port hopper       | 67        |

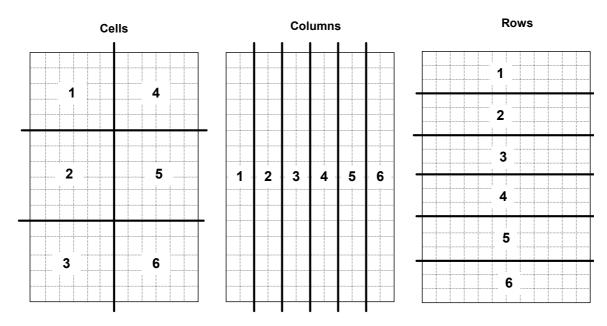

| Figure 4–11 Example of the different regular domain decomposition types              | 70        |

| Figure 4–12 Domain decomposition types in the multi-procession modelling SW          | 73        |

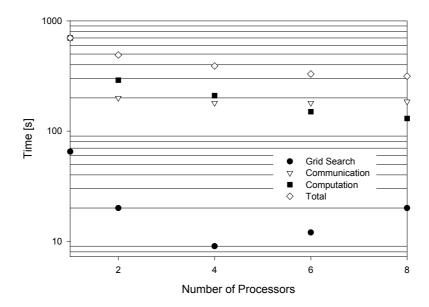

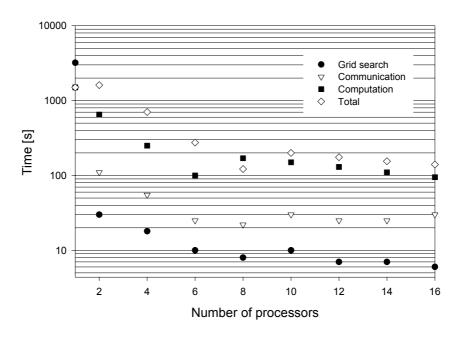

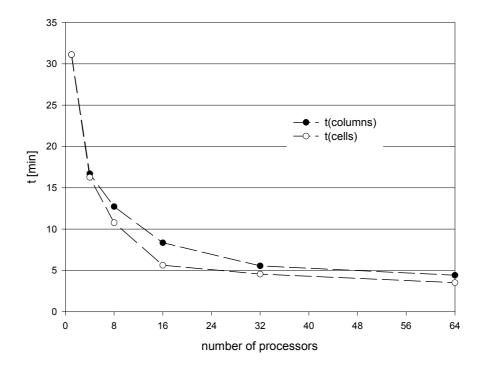

| Figure 4–13 Simulation time for different number of processor systems                | 74        |

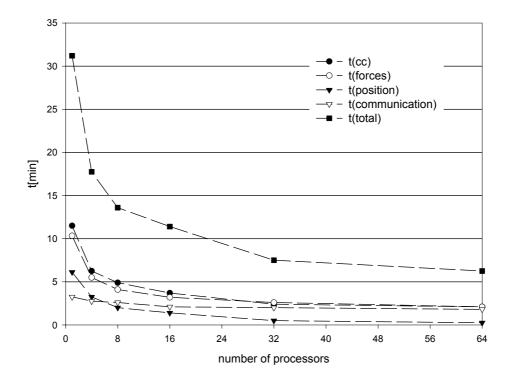

| Figure 4–14 Simulation time for different number of processor showing the time spent | 75        |

| by each unit(domain split into cells)                                                |           |

| Figure 4–15 Initial and final conditions for a simulation decomposing the domain in  | 76        |

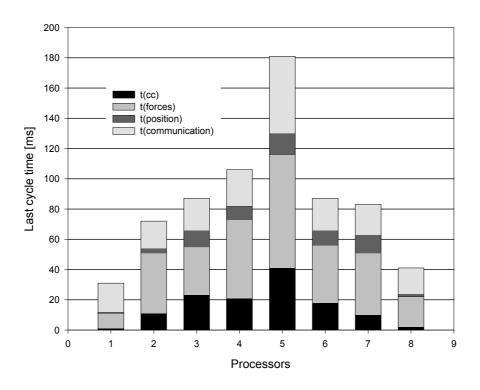

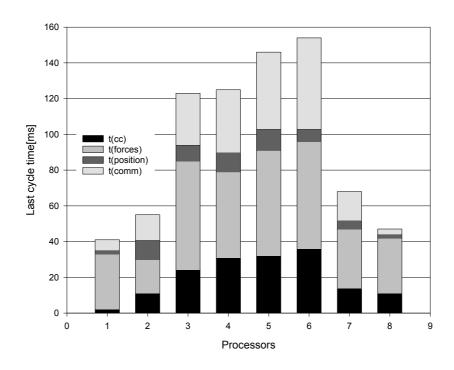

Figure 4–16 Time needed to perform the last cycle in a simulation with 8 processors

Figure 4–17 Time needed to perform the last cycle in a simulation with 8 processors

decomposition the domain in columns

decomposition the domain in cells

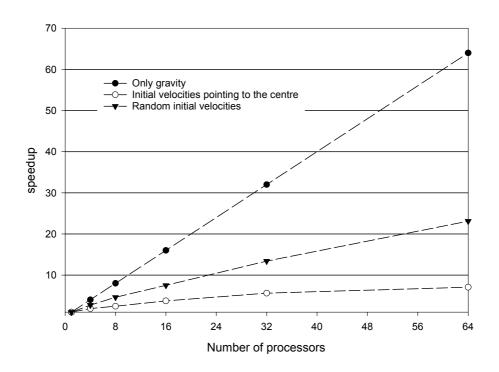

Figure 4–16 Speed-up for different initial velocities

77

77

79

columns and cells

| CHAPTER 5 HARDWARE IMPLEMENTATION OF THE DEM ON A FPGA                                 | 84  |

|----------------------------------------------------------------------------------------|-----|

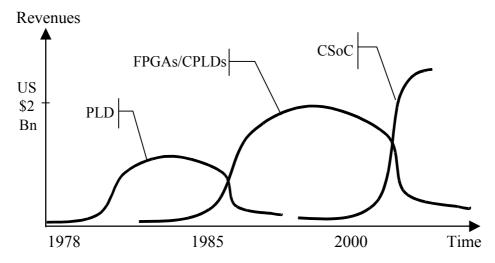

| Figure 5–1 Three FPL waves, PLDs, FPGAs/CPLD and CSoC                                  | 87  |

| Figure 5–2 Field Programmable Gate Array (FPGA) internal structure                     | 89  |

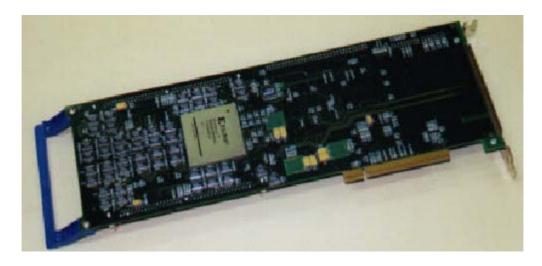

| Figure 5–3 RC100-PP Picture                                                            | 90  |

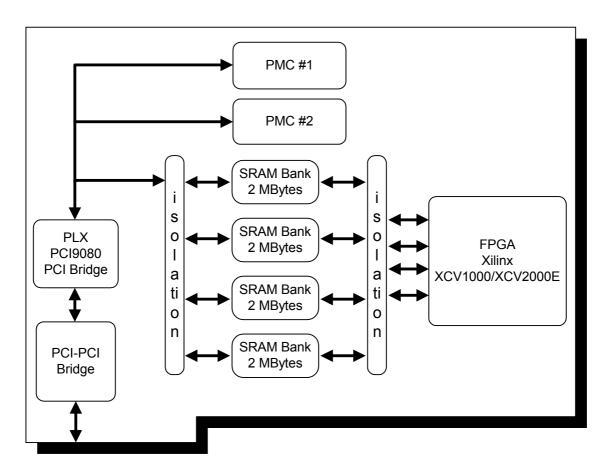

| Figure 5–4 RC100-PP Block Diagram                                                      | 91  |

| Figure 5–5 System layout                                                               | 92  |

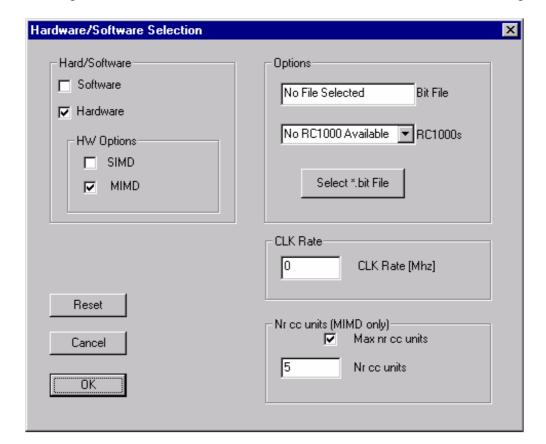

| Figure 5–6 Hardware Software selection                                                 | 93  |

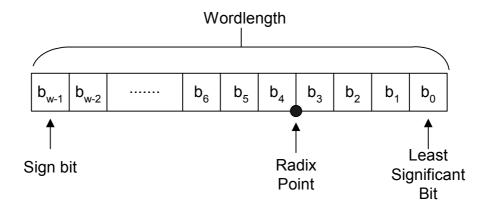

| Figure 5–7 Data format                                                                 | 94  |

| Figure 5–8 Low level parallelism FPGA Implementation block diagram                     | 95  |

| Figure 5–9 Balls in contact                                                            | 96  |

| Figure 5–10 Neighbour check model                                                      | 97  |

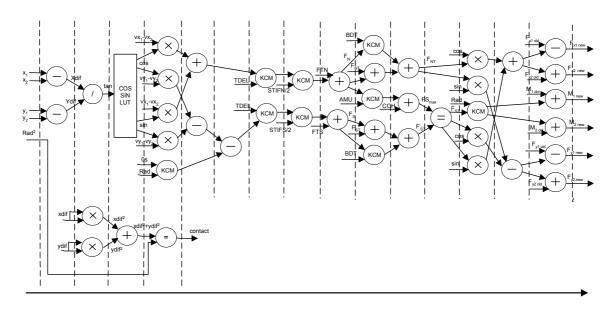

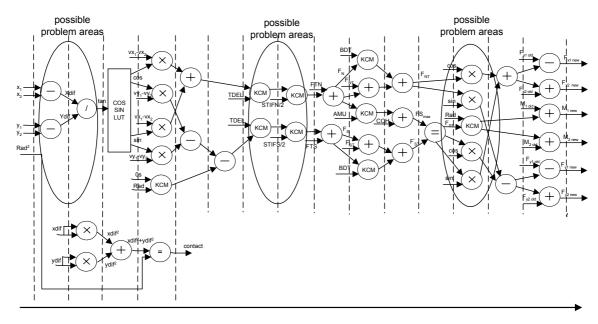

| Figure 5–11 Forces update unit internal structure                                      | 99  |

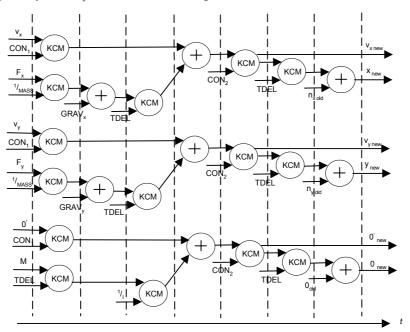

| Figure 5–12 Velocity and Position update unit internal structure                       | 100 |

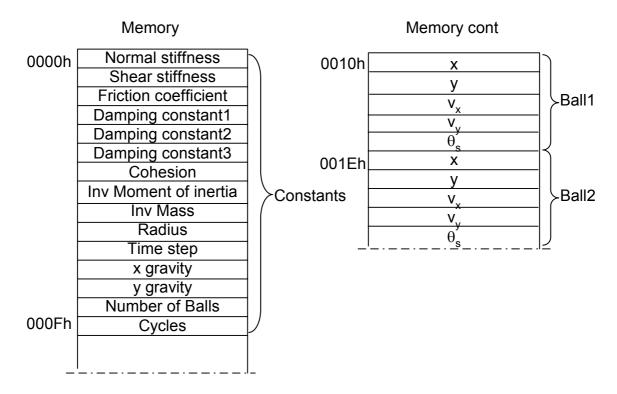

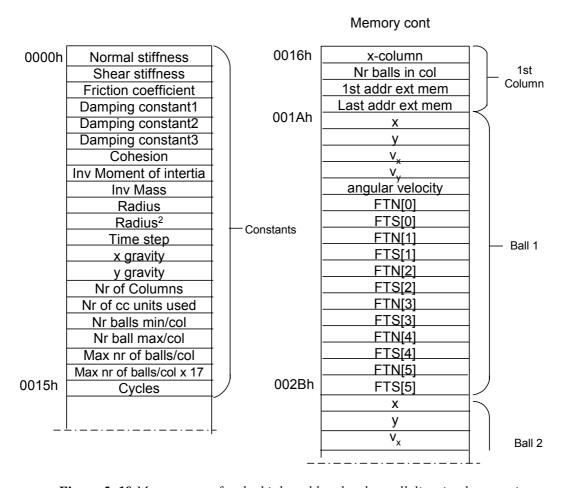

| Figure 5–13 Memory map for the low level parallelism implementation                    | 102 |

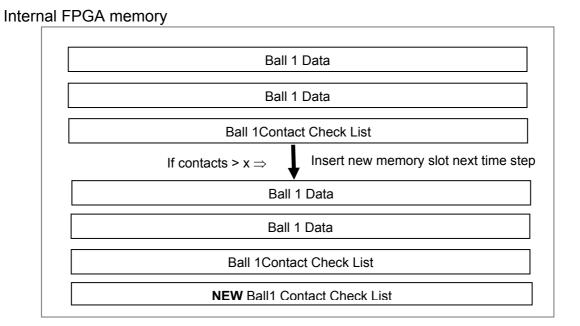

| Figure 5–14 FPGA's internal memory map                                                 | 103 |

| Figure 5–15 Domain decomposition                                                       | 105 |

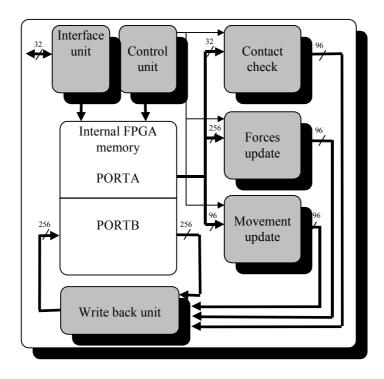

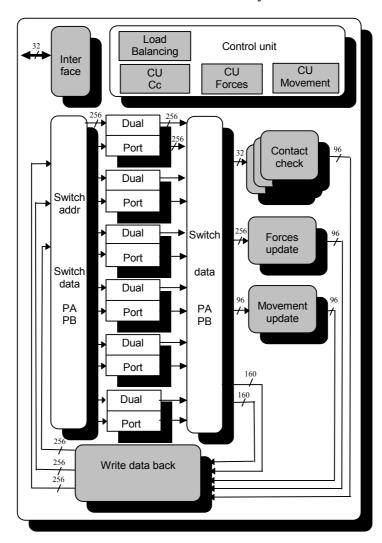

| Figure 5–16 High and low level parallelism FPGA implementation block diagram           | 106 |

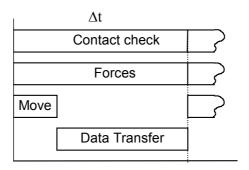

| Figure 5–17 Scheduling of the computation                                              | 107 |

| Figure 5–18 Simulation example of the adaptive cell boundaries                         | 110 |

| Figure 5–19 Memory map for the high and low level parallelism implementation           | 111 |

| Figure 5–20 High and low level parallelism scheduling                                  | 113 |

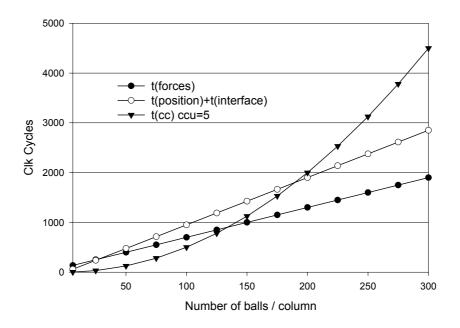

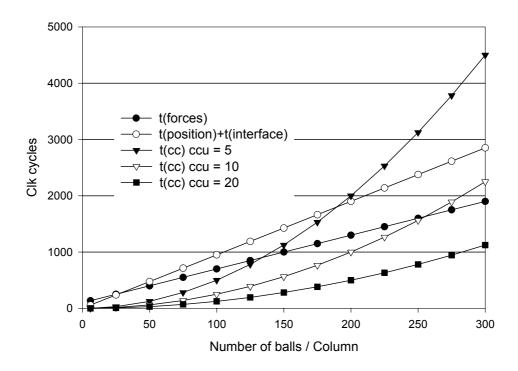

| Figure 5–21 Time needed for each task                                                  | 113 |

| Figure 5–22 Graph of clock cycles needed to compute t(forces) t (pos)+t(interface) and | 116 |

| t(cc) for a different number of contact check units.                                   |     |

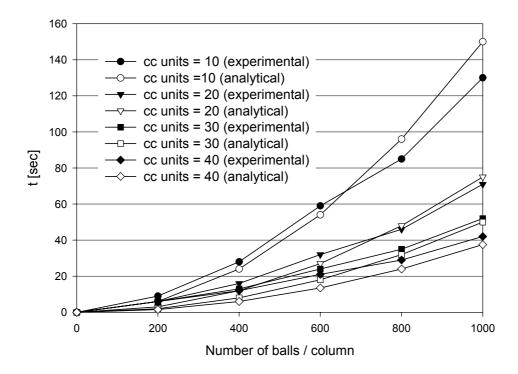

| Figure 5–23 Comparisons of experimental and analytical values to compute the contact   | 117 |

| checking for different number of contact check units.                                  |     |

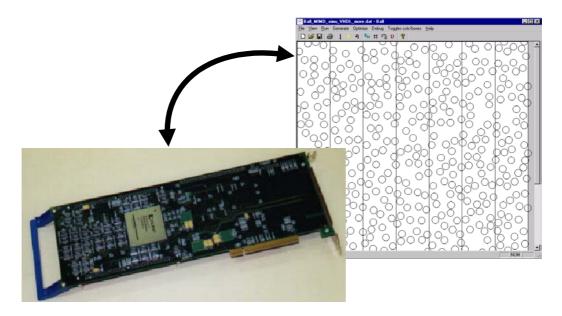

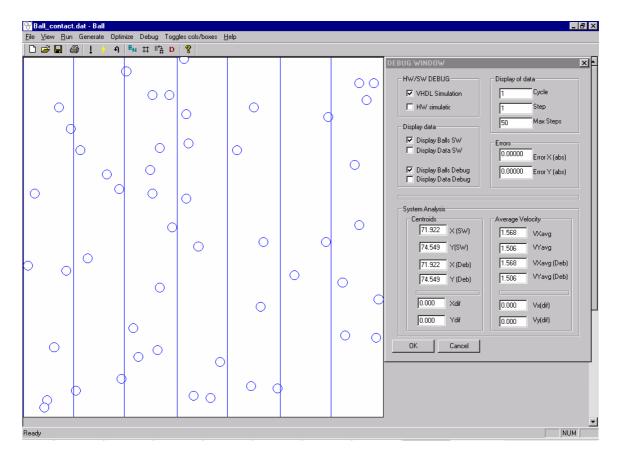

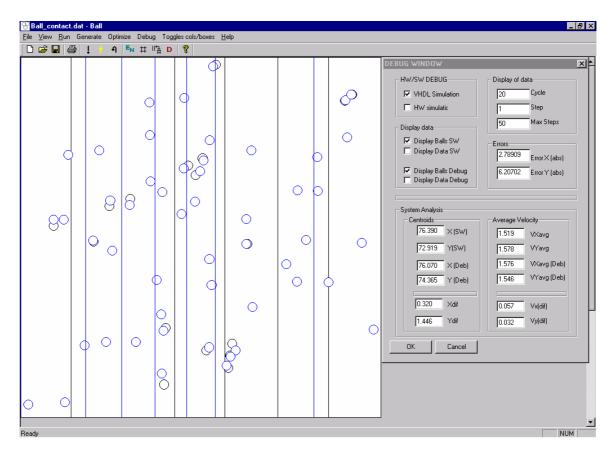

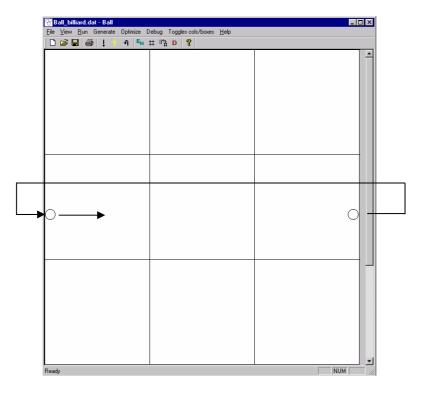

| Figure 5–24 Screen shot of the initial state of the hardware debugger                  | 121 |

| Figure 5–25 Screen shot of a debugged system of 50 balls after 20 cycles               | 122 |

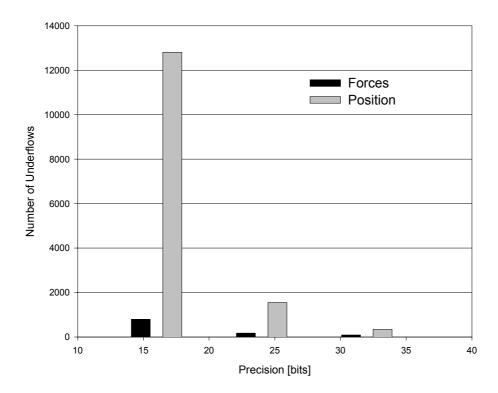

| Figure 5–26 pseudo code of under and overflow registration                             | 123 |

| Figure 5–27 Underflows in the forces and position update units as a function of the    | 124 |

| number of bits                                                                         |     |

| CHAPTER 6 SOFTWARE AND HARDWARE ANALYSIS                                                         | 128 |

|--------------------------------------------------------------------------------------------------|-----|

| Figure 6–1 Initial state of the 500 domain assembly for the SW (a) and for the HW (b)            | 130 |

| Figure 6–2 Initial state of the system of 50,000 particles                                       | 131 |

| Figure 6–3 Graphical representation of the measured and ideal speed-up                           | 132 |

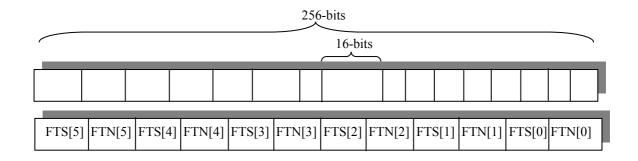

| Figure 6–4 16-bit data format                                                                    | 133 |

| Figure 6–5 Chopping example                                                                      | 136 |

| Figure 6–6 Rounding example and comparison with chopping                                         | 136 |

| Figure 6–7 Rounding carry example                                                                | 137 |

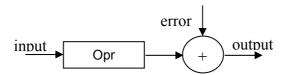

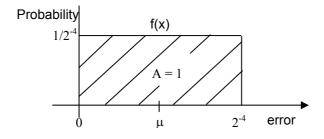

| Figure 6–8 Truncation/Round off propagation model                                                | 140 |

| Figure Error! No text of specified style in document1 Noise distribution model                   | 140 |

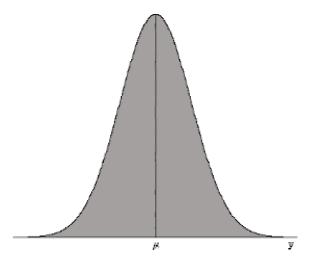

| Figure Error! No text of specified style in document10 Normal distribution function              | 142 |

| Figure 6–11 Velocity and Position update unit internal structure                                 | 146 |

| Figure 6–12 Forces update unit internal structure                                                | 147 |

| Figure 6–13 Special cases for cosine and sin                                                     | 148 |

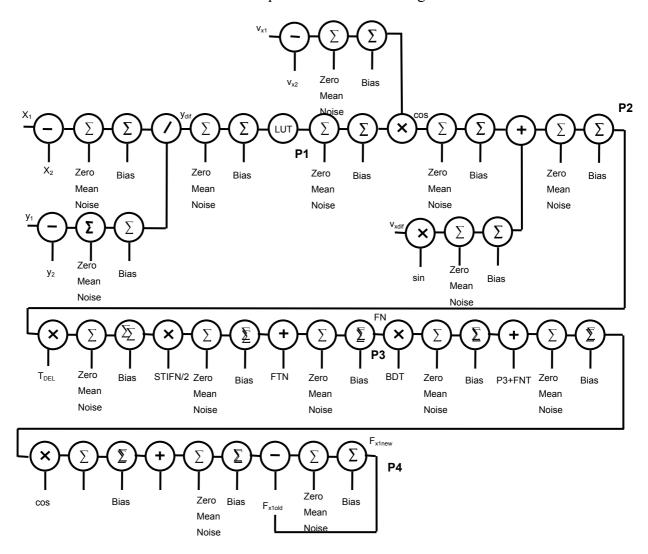

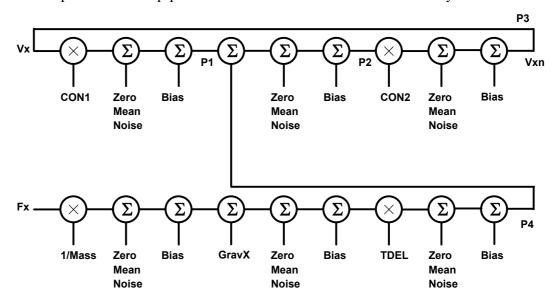

| Figure Error! No text of specified style in document2 Expanded flow graph for the F <sub>x</sub> | 149 |

| force pipeline in the forces update unit                                                         | 151 |

| Figure Error! No text of specified style in document3 Expanded flow graph for the x              | 154 |

| coordinate pipeline in the position update unit                                                  |     |

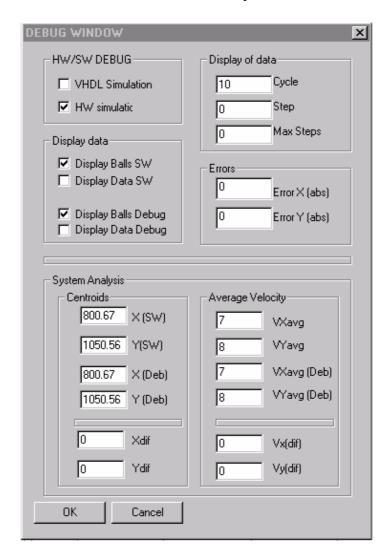

| Figure 6–16 SW window to measure the difference between the SW and the HW                        | 155 |

| simulation                                                                                       |     |

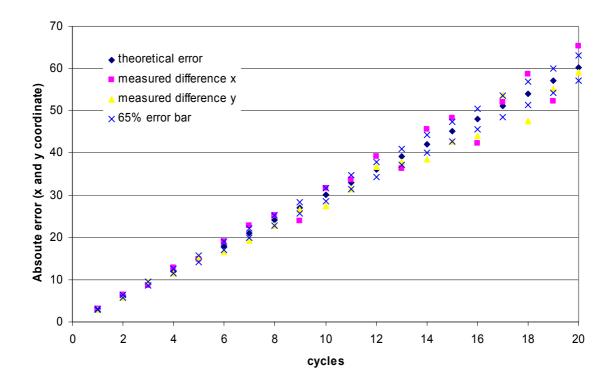

| Figure 6–17 Error accumulation in the hardware implementation compared to the                    | 157 |

| software implementation for the x and y coordinates                                              | 158 |

| Figure 6–18 Initialisation file for the simulations                                              | 159 |

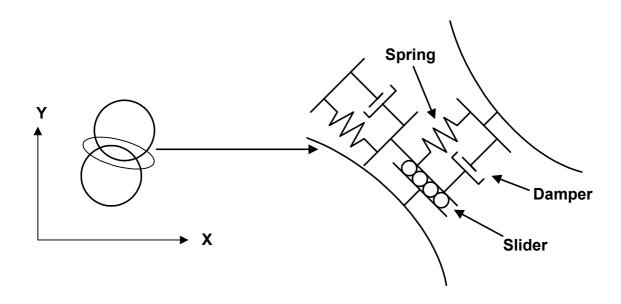

| Figure 6–19 Balls' contact model                                                                 | 159 |

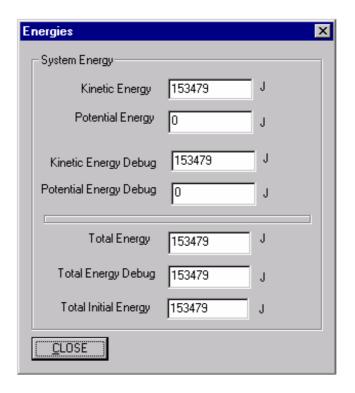

| Figure 6–20 Energy window once the software and hardware system have been generated              |     |

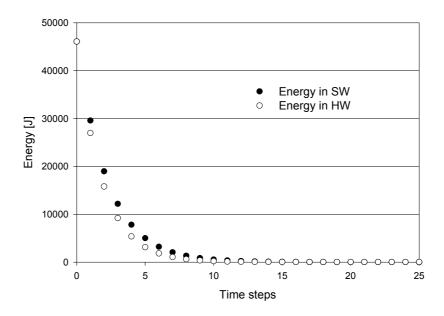

| Figure 6–21 System's Energy progression with damping for the software and the                    | 160 |

| hardware implementation                                                                          |     |

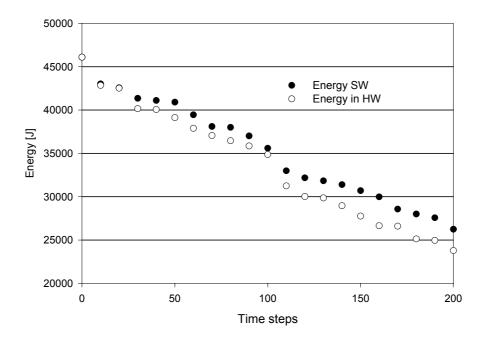

| Figure 6–22 Systems Energy progression without damping for the software and                      | 162 |

| hardware implementation                                                                          |     |

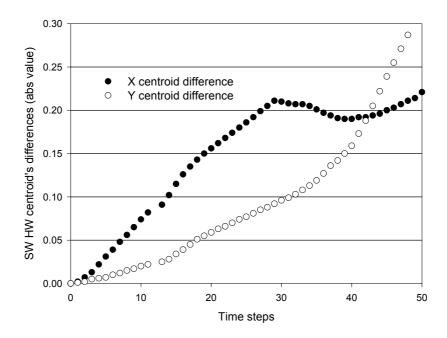

| Figure 6–23 Behaviour of the centroids difference between the software and the                   | 163 |

| hardware implementation                                                                          | 164 |

| Figure 6–24 Periodic domain example                                                              | 165 |

Figure 6–25 Average velocity progression

Figure 6–26 System energy for float and double SW simulation

| CHAPTER 7 SUITABILITY OF THE HW DESIGN FOR A MORE COMPLEX DEM                              | 170  |

|--------------------------------------------------------------------------------------------|------|

| Figure 7–1 Dataflow diagram for the DEM with walls                                         | 171  |

| Figure 7–2 Wall description                                                                | 172  |

| Figure 7–3 Ball-Wall contact detection                                                     | 174  |

| Figure 7–4 Ball-Wall contact for Vertical/Horizontal walls                                 | 175  |

| Figure 7–5 Equations to compute the forces between a wall and a ball                       | 176  |

| Figure 7–6 Equations to compute the new position of the wall                               | 177  |

| Figure 7–7 Balls in contact with different radii                                           | 182  |

| Figure 7–8 Contact detection for particles of different radius                             | 183  |

| Figure 7–9 Suggested Contact balls' data structure for systems with balls                  | 184  |

| of different radii in the FPGA                                                             |      |

| Figure 7–10 3-D Contact checks                                                             | 187  |

| Figure 7–11 Equations to compute the forces between two particles in 3-D                   | 190  |

| Figure 7–12 Equations for the 3-D Position Update                                          | 191  |

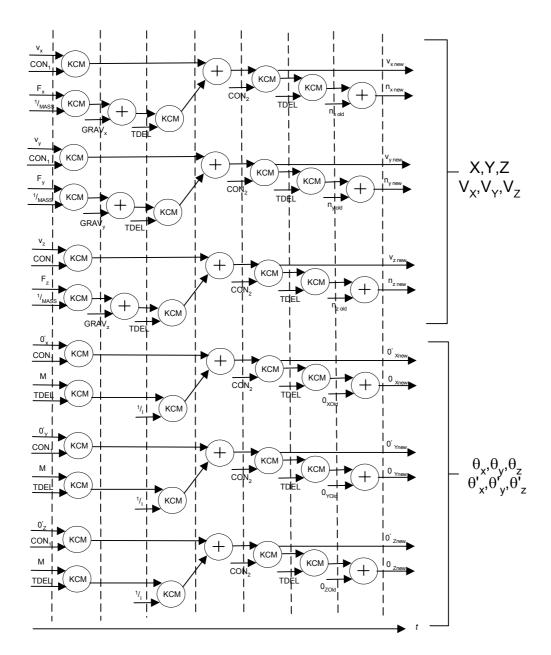

| Figure 7–13 Graphical Representations of the 3-D position update equations                 | 193  |

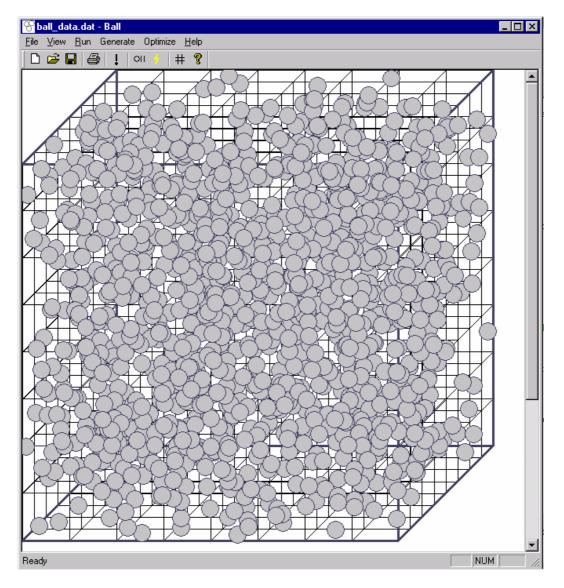

| Figure 7–14 Screen-shot of the 3-D software simulator                                      | 197  |

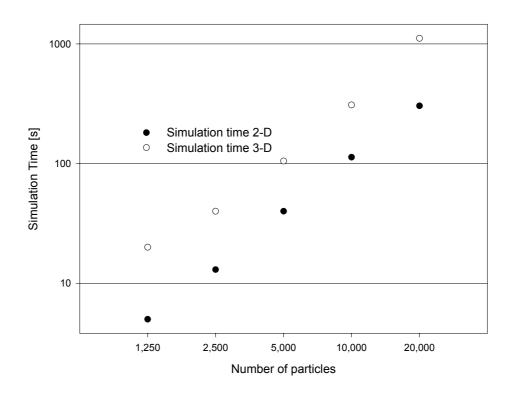

| <b>Figure 7–15</b> Graphical representation of the Simulation time of 2-D and 3-D system   | 198  |

| CHAPTER 8 SCALABLE AND ALTERNATIVE IMPLEMENTATIONS OF THE DEM                              | 202  |

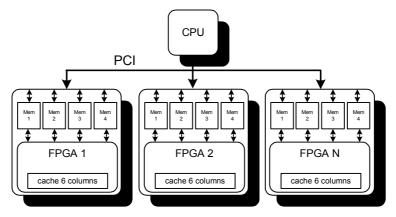

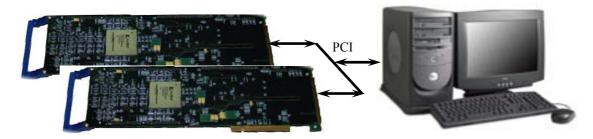

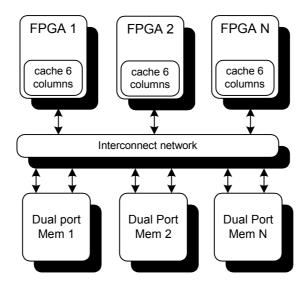

| Figure 8–1 Distributed Memory Multi-FPGA system                                            | 204  |

| Figure 8–2 Two RC1000-PP system                                                            | 204  |

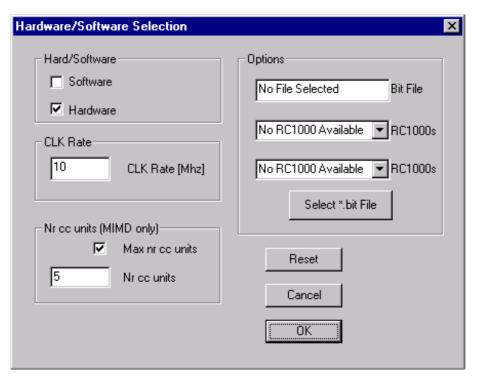

| Figure 8–3 Board selection for the Multiple FPGA design                                    | 205  |

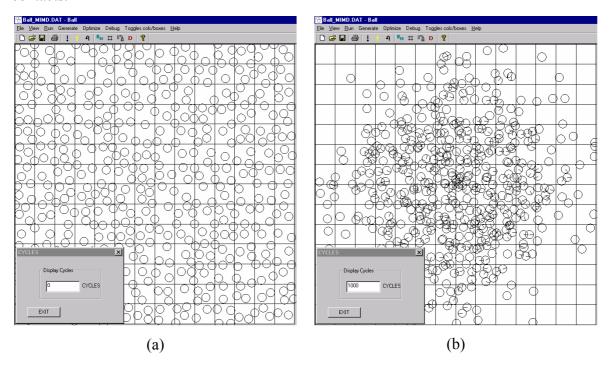

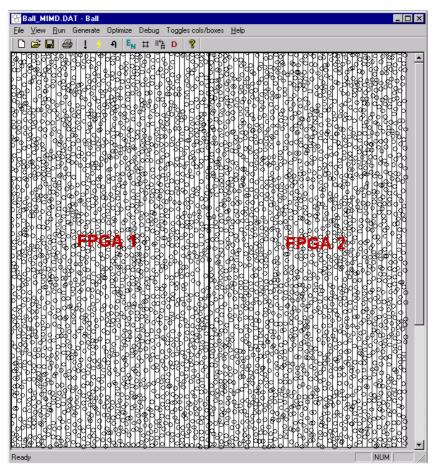

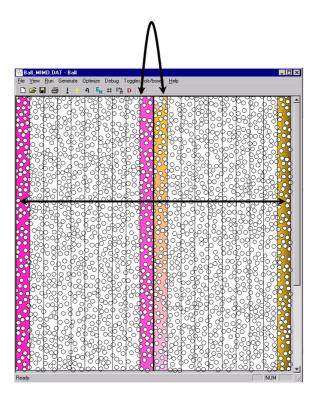

| Figure 8–4 Screenshot of the software program for the multiple FPGA design. The            | 206  |

| domain is split in two equally loaded parts                                                |      |

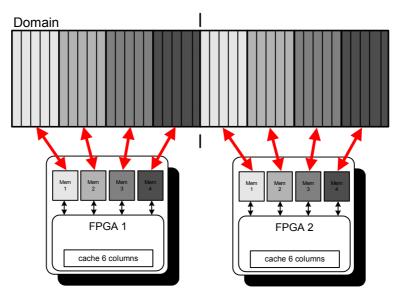

| Figure 8–5 Columns that need to be transferred from one board to another after every cycle | 207  |

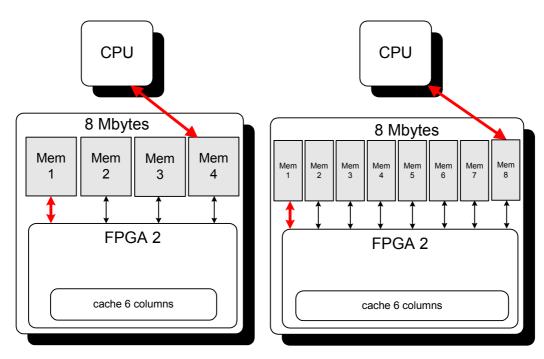

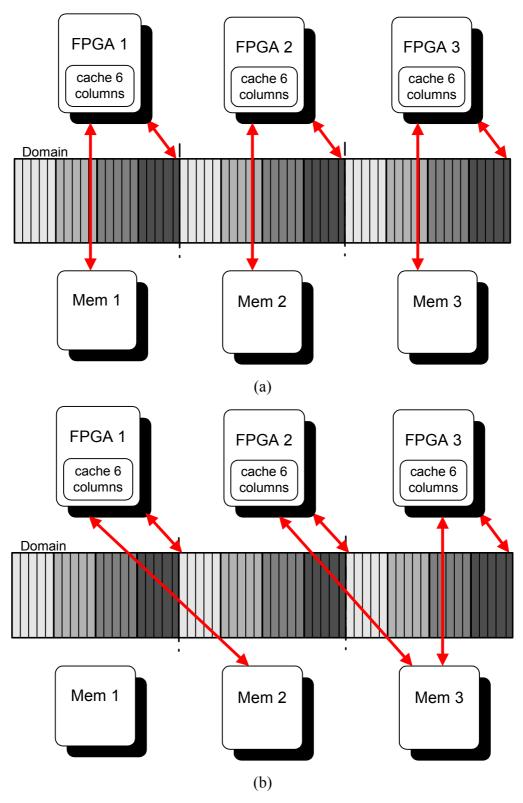

| <b>Figure 8–6</b> Domain mapping to the 4 memory units of RC1000-PP board.                 | 207  |

| Figure 8–7 Influence of a finer and coarse grained board memory                            | 210  |

| Figure 8–8 Example of a shared memory system                                               | 2012 |

| Figure 8–9 FPGAs' memory accesses                                                     | 214 |

|---------------------------------------------------------------------------------------|-----|

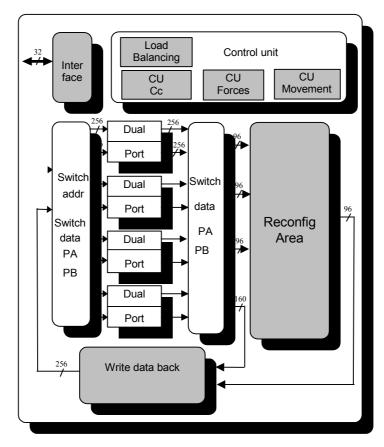

| Figure 8–10 Runtime reconfigurable architecture                                       | 217 |

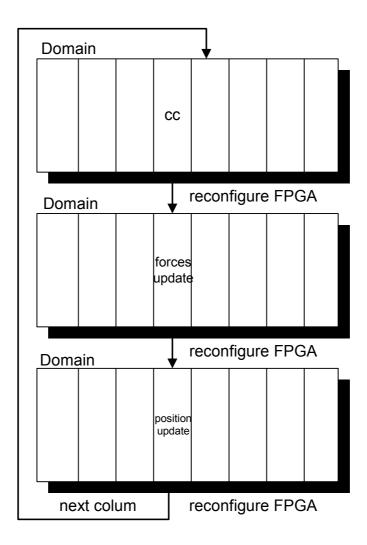

| Figure 8–11 Reconfigurable sequence                                                   | 218 |

| Figure 8–12 Number of columns to be cached into the FPGA                              | 219 |

| Figure 8–13 Internal FPGA structure with microprocessors                              | 222 |

| Figure 8–14 Hardware implementation using an FPGA with embedded microprocessors       | 223 |

| Figure 8–15 Computation time of the three main task, replacing the forces update unit | 225 |

| with 4 microprocessors                                                                |     |

| CHAPTER 9 CONCLUSIONS AND FUTURE WORK                                                 | 229 |

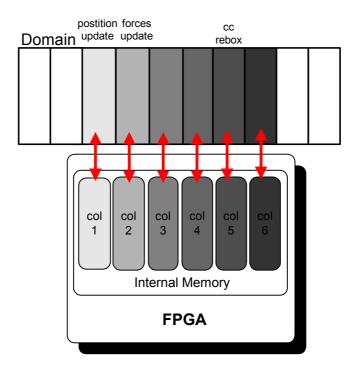

| Figure 9–1 Mapping of the domain decomposition on the FPGA's internal memory          | 230 |

# **List of Tables**

| CHAPTER 2 THE DISCRETE ELEMENT METHOD (DEM)                                                   | 8     |

|-----------------------------------------------------------------------------------------------|-------|

| <b>Table 2–1</b> Timing analysis for a system with 500 particles ran for 1000 time steps with | 18    |

| and without grid                                                                              |       |

| Table 2–2 Arithmetic operations needed for the contact check                                  | 19    |

| Table 2–3 Arithmetic operations of the force update functions                                 | 22    |

| Table 2–4 Arithmetic operations of the coordinate and velocity update function                | 23    |

| CHAPTER 3 SOFTWARE IMPLEMENTATION OF THE DEM                                                  | 32    |

| <b>Table 3–1</b> Comparison of the simulation time needed for an assembly of 500 particles    | 61    |

| ran for 1000 cycles depending on the amount of times the assembly is re-                      |       |

| drawn.                                                                                        |       |

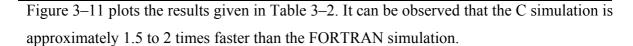

| <b>Table 3–2</b> Runtime comparison between the FORTRAN and the C simulator                   | 46    |

| Table 3-3 Energy comparison between the original FORTRAN and the new C                        | 49    |

| simulator                                                                                     |       |

| CHAPTER 4 REVIEW AND ANALYSIS OF PARALLEL DEM IMPLEMENTATIONS                                 | 52    |

| Table 4–1 Listing of the low and high implementations of the DEM on different HW              | 69    |

| platforms                                                                                     |       |

|                                                                                               |       |

| CHAPTER 5 HARDWARE IMPLEMENTATION OF THE DEM ON A FPGA                                        | 84    |

| Table 5–1 Hardware requirements for the low level parallelism units                           | 101   |

| Table 5–2 Hardware resources used for by this implementation                                  | 117   |

| Table 5-3 Growth of ideal number of balls/column as a function of the number of               | 1 119 |

| contact check units to make $t(cc) = t(position)+t(r/w)$ .                                    |       |

| Table 5-4 Relation of number of balls allowed in the system to make t(cc)=t(pos)+             | 120   |

| t(interface) and its memory requirements                                                      |       |

|                                                                                               |       |

| CHAPTER 6 SOFTWARE AND HARDWARE ANALYSIS                                                                                    | 128 |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Table 6–1 Simulation time for the SW and the HW implementation for 500 particles                                            | 130 |

| Table 6–2 Run time for the software and hardware simulation and speed-up results                                            | 131 |

| Table 6–3 Worst case analysis for the multiplication as a function of the input values                                      | 138 |

| Table 6–4 Worst case analysis for the division as a function of the input values                                            | 138 |

| Table 6–5 Worst case analysis for the subtraction as a function of the input values                                         | 139 |

| Table 6–6 Simulation time for 10,000 and 20,000 particles for 1000 cycles in single and                                     | 166 |

| double precision floating-point arithmetic                                                                                  |     |

| CHAPTER 7 SUITABILITY OF THE HW DESIGN FOR A MORE COMPLEX DEM                                                               | 170 |

| Table 7–1 Minimum set of parameters to describe a wall                                                                      | 172 |

| Table 7–2 Rest of parameters needed once the wall is interacting will the balls                                             | 173 |

| Table 7–3 Arithmetic operations needed the check for contacts between walls and balls                                       | 174 |

| Table 7-4 Number and types of arithmetic operations to check for contacts between balls                                     | 175 |

| and walls, only for vertical and horizontal walls.                                                                          |     |

| Table 7–5 Additional arithmetic operations needed to calculate the forces between a wall                                    | 177 |

| and a ball, compared to the arithmetic operations needed forces between two balls.                                          |     |

| <b>Table 7–6</b> Arithmetic operations needed to compute the new position of a wall                                         | 178 |

| Table 7–7 Number of Xilinx slices needed to perform different arithmetic operations                                         | 178 |

| <b>Table 7–8</b> Number of Xilinx slices needed for the additional arithmetic operations to include walls                   | 179 |

| Table 7–9 Variables to describe a 3-D particle                                                                              | 185 |

| Table 7–10 Number of arithmetic operations needed for the contact check in 3-D                                              | 187 |

| <b>Table 7–11</b> Number of Arithmetic operations involved in the 3-D forces update units for particles of the same radius. | 190 |

| Table 7–12 Number of Arithmetic operations involved in the 3-D position update units                                        | 192 |

| for particles of the same radius                                                                                            |     |

| <b>Table 7–13</b> Comparison between the arithmetic operations for the 2-D and the 3-D case in each task                    | 194 |

| Table 7–14Slices needed to accommodate arithmetic operations for 3D                                                         | 195 |

| Table 7–15 Runtime simulation results for 2-D and 3-D assemblies with the same                                              | 198 |

| properties |

|------------|

|------------|

design 1

| CHAPTER 8 SCALABLE AND ALTERNATIVE IMPLEMENTATIONS OF THE DEM                         | 202 |  |  |  |

|---------------------------------------------------------------------------------------|-----|--|--|--|

| Table 8–1 Example of the number of boards that can work in parallel without having to | 209 |  |  |  |

| stall any operation in any of the FPGAs.                                              |     |  |  |  |

| Table 8–2 Example of the number of boards that can work in parallel without having to | 210 |  |  |  |

| stall the operation of any FPGA for 8 memory units instead of                         |     |  |  |  |

| Table 8–3 Comparisons of speed-up obtained by hardware DEM for a single FPGA and      | 211 |  |  |  |

| two FPGAs compared to an optimised software version.                                  |     |  |  |  |

| Table 8–4 Number of units that can be implemented in the reconfigurable area          |     |  |  |  |

| Table 8-5 Values of the time needed to compute the cc, forces and position update     |     |  |  |  |

| versus the time needed to reconfigure the 50% of the Xilinx XCV2000E.                 |     |  |  |  |

| Table 8–6 Number of arithmetic operations involved in the forces update unit          |     |  |  |  |

| Table 8–7 Number of operations needed for each arithmetic operation.                  |     |  |  |  |

| <b>Table 8–8</b> List with the number of units implemented in parallel.               | 224 |  |  |  |

**Table 7–16** Theoretical speed-up of the 3-D SW simulator and the theoretical HW

199

## **Glossary of Abbreviations**

**2-D** Two **D**imensional

**3-D** Three **D**imensional

ASIC Application Specific Integrated Circuit

CC Contact Check

CISC Complex Instruction Set Computer

CLB Configurable Logic Block

**DEM** Discrete Element Method

**FPGA** Field Programmable Gate Array

GUI Graphical User Interface

HDL Hardware Description Language

HW Hardware

IC Integrated Circuit

IP Intellectual Property

I/O Input/Output

KCM Constant Coefficient Multiplier

LAB Logic Array Block

LC Logic Cell

LUT Logic Element

LUT Look Up Table

MISD Multiple Instructions Single Data

MIMD Multiple Instructions Multiple Data

PAL Programmable Array Logic

PC Personal Computer

PCI Peripheral Component Interconnect

PLD Programmable Logic Device

Ulp Unit of Least Precision

RISC Reduced Instruction Set Computer

RTR Run Time Reconfiguration

SIMD Single Instructions Multiple Data

SISD Single Instructions Single Data

SW Software

VHDL Very High Speed Integrated Circuit Hardware Description Language

# CHAPTER 1

### Introduction

### 1.1 Introduction

The number of transistors that can be integrated onto a single silicon die tends to double approximately every 18 months, just as Intel's co-founder Gordon Moore predicted more than 20 years ago [1]. This increase in density is accompanied by a corresponding improvement in speed. This has led to a widespread availability of very powerful computer equipment at low cost, a development that has affected the design approaches used in many branches of engineering. One important consequence is that much wider use is made of simulator programs. Simulators have the great advantage of being able to test a system without having to actually build it. This saves an enormous amount of time and therefore money. Nevertheless, there are still some applications where the available computing power of standard computers is still not sufficient to perform many of the desired simulations. One of these application areas is the use of the Discrete Element Method for modelling the behaviour of granular materials.

Granular materials can be found everywhere in life, and their study is important to many different disciplines, such as geomechanics, civil engineering and chemical engineering. There are many different approaches to model their behaviour (e.g. analytical, physical and

numerical). The numerical techniques are the most powerful, as they have the greatest flexibility, and they also provide full visibility of the internal behaviour of the medium at every stage.

The Discrete Element Method (DEM) is a numerical method to model the behaviour of particle assemblies. The DEM was first developed in the 1970's, but its widespread use has been hampered by its extremely computationally demanding nature. The DEM considers every particle as an individual body and computes the total force applied to each particle. From this, using Newton's second law, the acceleration of each particle is established; this can be integrated to give each particle's velocity; this in turn can be integrated to provide an updated position. Each particle's force interaction, acceleration and position are calculated individually at each time step. The assumptions underlying the method are only correct if no disturbances can travel beyond the immediate neighbours of a particle within one time step. This generally means that the time step must be limited to a very small value, thus making the DEM *extremely* computationally expensive.

The particles may be bonded together to represent, for example, rock, or they may remain unbonded to represent, for example, soil. Bonded together they can represent entire structures, such as dams or bridges. It is has even been suggested [2] that the DEM may in future replace the more popular continuum methods such as the Finite Element Method and the Finite Difference Method, as these have two main drawbacks. Firstly a suitable stress-strain law may not exist; secondly, localised features, such as cracks, are difficult to model with the continuum approaches. However in order to use the DEM to simulate entire engineering structures, which may involve millions of particles, enormous computing power is required.

Although the DEM is extremely computationally expensive, it exhibits an extraordinarily high degree of parallelism. Many attempts have therefore been made to run the DEM on multiprocessor computer systems. Ideally, one would hope to achieve a speed-up of the simulation that is proportional to the number of processors used (linear speed-up). However, synchronization and communication overheads, as well as load balancing problems, mean that these systems underachieve the ideal limit when the number of

processors is large. Other approaches to allow the simulation of realistic particle problems (typically hundreds of thousands of particles) are therefore needed.

The impact of Moore's law has been felt not only by computer processor chips, but also by programmable logic. Originally programmable logic was used only for small-scale glue logic applications. However, the complexity and speed of programmable logic, in particular Field Programmable Gate Arrays (FPGAs), has increased enormously over the last decade. FPGAs have now achieved sufficient logic density that they can be used to implement an entire complex system with minimal off-chip resources.

One promising application area for these devices is to form FPGA-based reconfigurable co-processors within standard computers, which can be used for algorithm acceleration. This approach is known as *reconfigurable computing*<sup>1</sup>. FPGA co-processors have much lower cost and greater flexibility than ASIC hardware (albeit with inferior performance). For the right type of application, a reconfigurable computer can rival the expensive parallel computers that are normally used to accelerate computationally expensive algorithms. FPGAs thus open a new window to low cost hardware acceleration.

The DEM has properties that suggest that it may be suitable for acceleration using FPGAs: it exhibits a enormous degree of parallelism, and can be processed using short wordlength arithmetic. It is therefore tempting to examine how well this algorithm would map into an FPGA coprocessor.

### 1.2 Contribution of this Thesis

This thesis presents a study of the use of reconfigurable computing using FPGAs to accelerate the DEM. The major contributions made by this work are as follows:

<sup>&</sup>lt;sup>1</sup> Some authors use the term *reconfigurable computing* to refer only to approaches which use run-time reconfiguration of the FPGA, whereas others apply the term to any use of an FPGA co-processor. For most of this work, the second definition is used. However, in chapter 8 an investigation is presented into the application of run time reconfiguration to the DEM problem.

- 1. A novel approach was taken to accelerate the 2-D DEM by designing a dedicated hardware architecture on an FPGA. A simpler architecture was developed first, which only made use of the low level parallelism of the DEM. Subsequently, a more sophisticated architecture was designed, which exploits not only the low level, but also the high level parallelism, and involves decomposing the domain into different regions. This decomposition is adaptively optimised in order to provide good load balancing.

- 2. In order to achieve even greater speed-ups, a multi-FPGA design has been implemented. This shows that communication and computation by the FPGAs can be completely overlapped, thus achieving good scalability of the speed-up.

- 3. Predictions are presented as to how well the hardware architecture would map onto more sophisticated FPGAs. The effects of additional resources, such as embedded multipliers and embedded microprocessors are considered.

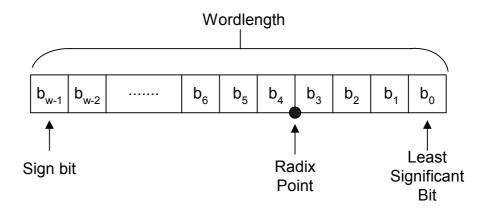

- 4. The effects of short wordlength arithmetic on the DEM results has been investigated, and performance of hardware based on 16-bit fixed point arithmetic has been found to be acceptable. For DEM simulations the result of interest is the behaviour of the bulk, not the behaviour of the individual particles. For the bulk behaviour, the DEM is to a large extent a self-correcting algorithm, thus making low numerical precision tolerable. A relatively low wordlength was necessitated by the limitations of the FPGA hardware available.

- 5. The prototypes built for the hardware implementations were limited by the available FPGA resources, and therefore a relatively simple DEM problem was implemented (using a 2-D domain containing no walls, with all particles having the same radius, and using a simple interaction law). An analysis has been carried out that demonstrates the resource requirements that would be needed to extend the architecture to a more complicated DEM problem.

### 1.3 Thesis Organisation

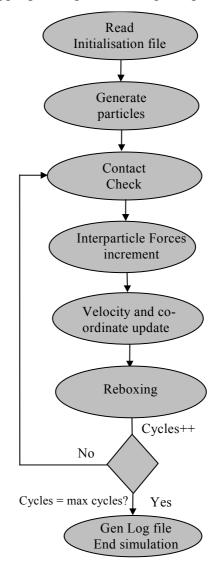

Chapter 2 introduces the basic concepts of the Discrete Element Method (DEM). The principle stages of the algorithm are formulated, and their asymptotic complexity is discussed. The most time consuming task involves a search of the domain for contacts between particles, which has a complexity of  $O(N^2)$ , where N is the number of particles in

the domain. If the one large domain is decomposed into multiple smaller domains, the expense of the  $O(N^2)$  search is greatly reduced. Domain decomposition also provides an obvious and natural way to parallelise the DEM, by allocating different domains to different processors. However, processing the different domains on different processors leads to a communication overhead as particles transition from one domain to another, which slows down the speed-up achievable by parallel computers. Chapter 2 discusses approaches to domain decomposition, and illustrates the effectiveness of the method. It also provides an assessment of the expenses associated with domain decomposition.

Chapter 3 presents the development of the software DEM simulator used in this work. This is based on a standard public domain FORTRAN code for the DEM, but is re-written in C, and contains numerous enhancements and improvements. These include the use of C's superior data structures to accelerate the simulation, a visual interface, an interface to the hardware version, and a debug mode in which the hardware and software versions can be run in synchrony and their results compared. Also, the software written for this project has the ability to emulate the performance of the code on parallel machines of different capabilities (e.g. processor speed, and inter-processor communications bandwidth). The simulator tracks the time taken and the amount of communication generated for the processing of each sub-domain, and uses this to produce reports on how well the simulation would speed up on various types of parallel machine.

Chapter 4 presents a brief review of issues influencing speed-up in parallel processing. It then surveys the various attempts at parallelisation of the DEM that can be found in the literature. Most of these attempts have chosen problems that are anomalously favourable for parallel processing, e.g. domains decomposed into vertical strips in which particles fall under gravity. This gives rise to very few transitions between subdomains, which means that communications overhead is very low, and good load balance is always achieved. In these "nice" problems, high speed-ups can be achieved, but for more realistic problems the speed-up is far less than linear. At the end of chapter 4, the simulator developed in chapter 3 is used to assess the "niceness" of a variety of problem types, domain decompositions, and initial conditions. The dependence of the communication and synchronisation overheads on the choice of problem and domain decomposition is quantitatively assessed.

Chapter 5 describes two hardware designs that were implemented in a reconfigurable computing board. The first is a simpler implementation, which only makes use of the low level parallelism of the algorithm. The second is a more complex implementation, which exploits not only the low level parallelism, but also the higher level by performing the major tasks in parallel using domain decomposition techniques. In order to allow the hardware implementation to fit on the available FPGA boards, a number of compromises had to be made. A limited formulation of the DEM was implemented, which performed only 2-D simulations of assemblies whose constituent particles all have the same radius and whose domains contain no walls. Also, 16 bit fixed point arithmetic was used.

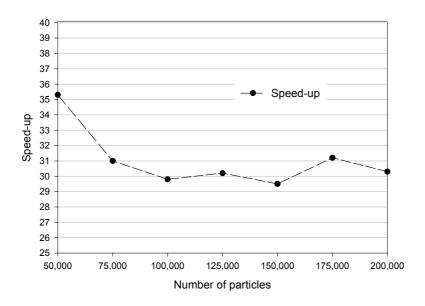

In chapter 6 both hardware implementations are compared with the software implementation in terms of speed-up and numerical precision. The complex hardware version gives a factor of 30 speed-up compared to the software version, for a simulation scenario that was deliberately chosen to be as favourable as possible for the software. For other scenarios, the speed-up achieved by the hardware is much greater. Chapter 6 also provides a review of issues underlying error propagation in finite precision arithmetic, and demonstrates that the hardware is free of pathological cases that cause catastrophic loss of accuracy. The actual loss of precision caused by the 16-bit arithmetic is estimated, and the estimate is confirmed by measurement of simulations running on the hardware.

Chapter 7 describes how the design can be modified to relax some of the restrictions that were used for the design in chapter 5. The use of 3-D, variable particle radius, and walls within the domain are considered. Projections are made as to how much hardware is required, and what speed-up can be expected.

Chapter 8 presents a design of a system using multiple FPGA boards to achieve a higher speed-up. A system using two FPGAs was actually implemented, and its results are used to project how well the design could scale to a system using many FPGA boards. Chapter 8 also discusses how well the design could be adapted to take advantage of the properties of more sophisticated FPGAs. Application of run-time reconfiguration and embedded microprocessors and multipliers is considered.

Chapter 9 discusses the conclusions of the study, and offers some directions for possible future work.

### 1.4 References

- [1] Moore, G. "Cramming more components onto integrated circuits", Electronics, Volume 38 Number 8, April 19, 1965

- [2] Cundall, P.A. "A discontinuous future for numerical modelling in geomechanics?" Proceedings of the Institution of Civil Engineers, Geotechnical Engineering 149, Issue 1 Pages 41-47, January 2001.

# Chapter 2

# THE DISCRETE ELEMENT METHOD (DEM)

### 2.1 Introduction

Granular materials can be found everywhere in life. They appear in civil engineering structures in the form of, for example, sand and gravel, in the chemical and pharmaceutical industry, e.g. pills, and in the agricultural industry as all kinds of grain. Their behaviour has always interested human beings, but their study has been hampered because of their distinctive properties. Numerical techniques started to appear in the early 1970's [1], but the lack of computational power made it impossible to simulate real problems in sufficient detail. With the increase of computing power these numerical techniques have become more and more important, but there is still not enough computing power to solve large problems, which involve millions of particles in 2-D and in 3-D.

Granular materials can be defined as large conglomerations of discrete non-biological macroscopic particles. (For biological entities a number of difficulties arise. Firstly, for collections of animals or plants, individual entities may be capable of autonomous self-directed motion. For macromolecules, interactions forces are non-local, e.g. Van der Waal forces). Typically the radius of such particles has to be at least 1 µm. Granular materials

behave differently from any other familiar form of matter. Like a liquid, they can flow and assume the shape of the container, and like a solid, they can support weight; some can support a tensile stress; others cannot [2]. They can therefore be considered as a state of matter in their own right.

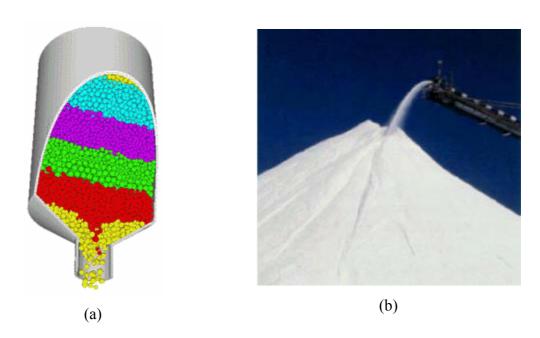

Many of the raw materials used in the food, chemical and pharmaceutical industries are granular media (illustrated in Figure 2–1). With the advent of modern machinery, the speed at which granular raw materials are processed has increased dramatically. This increase in speed has greatly increased the chance of damage to the fine particles during processing. In order to optimise the speed of production, and to reduce the amount of damage caused to

Figure 2–1 Examples of storage and transportation of granular media

(a) Particles in a hopper (b) Transporting particles in conveyer belt

the particles, the effect of these mechanical interactions needs to be known. In many cases, for the purpose of processing speed-up, water and other fluid may be added which would alter the surface energy and adhesion between particles. Other manufacturing processes, e.g. in the automotive industry, rely on casting large metal parts in carefully packed beds of sand. Yet the technology for handling and controlling granular materials is poorly developed. Estimates show that 60% of the capacity of many industrial plants is wasted due to problems related to the transport of these materials from one part of the factory floor

to another [3]. Hence even a small improvement in our understanding of how granular media behave should have a profound impact for industry. All these require an understanding of the microscopic mechanical properties and the behaviour of their interactions so that the macroscopic behaviour of the bulk can be understood.

### 2.2 Analysis of the Behaviour of Granular Media

Granular materials are formed of distinct particles, which displace independently from one another and interact with each other only at the contact points [5]. The discrete nature of the granular materials leads to a complex behaviour under conditions of loading and unloading.

Real physical tests on granular materials have the advantage of getting precise results, but have some serious drawbacks. Primarily, the internal stresses cannot be measured accurately and must be estimated from the boundary conditions. Secondly it is almost impossible to repeat two completely identical experiments. These drawbacks led to the development of theoretical models in order to study the behaviour of these materials. These models consist of assemblies of discs or polygons (in 2 dimensions) or spheres or polyhedra (in 3 dimensions). These models are simulated using physical, analytical or numerical means [4].

The numerical modelling approach is the most powerful of the modelling techniques as it is more flexible than analytical modelling and has the advantage over physical modelling that any data can be accessed at any stage of the experiment. The major drawback of this method is that it is computationally very expensive and therefore very time consuming.

#### 2.3 Simulations

In order to simulate the behaviour of a granular material, a suitable model has to be developed first. A model is a mathematical representation of a physical problem in a certain context. Models vary in their accuracy, but no model is perfect: the only perfect model would be the real system itself. Once the model is generated it has to be validated with real experiments in order to check for its correctness and robustness in the area of interest. A simulation can therefore be defined as the implementation of a particular model

in a computer. The solution of a typical model will take a predictable period of time before it delivers a result. It is therefore necessary to distinguish between:

- The real time that a physical process requires to complete a given action

- The computation time, which is the time needed by the computer to simulate the same physical action.

A process that happens in nature in a few seconds may take hours or even days to be simulated on a computer. The simulation time is of course software and hardware dependent. The same software simulator will run much faster on a faster workstation. However, an optimised software version can run faster on a slower workstation in terms of real time, than an un-optimised software version running on a fast workstation. In order to have a fast simulation, software and hardware have to be matched as much as possible.

The first numerical simulations of granular materials appeared at the end of the 1970's [5]. Two approaches were taken:

- The continuum approach, which considered the granular assembly as a continuum. (The success of the continuum approach for civil engineering problems reflects the fact that problems involving soils are of a large scale, for which the discrete nature of the soil does not seem to play an important role). This approach is only valid for certain types of problem.

- The discrete approach, which considered each individual particle as an individual entity.

The disadvantage of the continuum approach is that the discrete nature of the particles is not captured, and that cracks and rupture surfaces are not well captured by this approach [6]. On the other hand, discontinuous models, while treating these issues much better, are computationally very expensive, with simulations of thousands of particles taking hours and even days to finish. In the discrete approach every single particle is considered as an entity by itself, which moves following the physical laws of the domain.

### 2.4 Advent of the Discrete Element Method (DEM)

Cundall introduced the Discrete Element Method (DEM) in 1971 [7]. This numerical method considers every particle as a separate entity. The interaction force, acceleration and movement of each particle are calculated individually at each time step. The assumptions underlying the method are only correct if no disturbance can travel beyond the immediate neighbours of a particle within one time step. This is due to the explicit nature of the method. This generally means that the time step must be limited to a very small value. There are two main types of numerical time integration scheme:

- Explicit

- Implicit

An explicit method does not require the solution of the global equation. Therefore the information is transmitted from one point to another one time step at a time. If the time step is too large, excessive extrapolation would result, and the method can become unstable. There is therefore a critical maximum time step. Implicit methods, by contrast, involve the solution of the global equation, but have superior numerical stability.

As computing power increases, so does the number of applications that can be modelled reasonably using the DEM. An even higher growth is expected during this decade as computing power keeps growing, and as the method starts to be used in order to model entire engineering structures (such as dams and tunnels), built of particles bonded together to represent solid material. It is further suggested that continuum methods will be replaced by particle approaches in the future [6], as these capture the behaviour of localized cracks much better than the continuum approach, and a suitable stress-strain law for the material may not exist or the law may be excessively complicated with many obscure parameters.

The main drawback to the application of particle methods to large-scale problems is that their very high computational demands limit the size of system that can be simulated within a feasible timescale. Also, time must be spent calibrating the laws by which the micro-structure affects the overall macro-structure behaviour.

### 2.5 Concepts of the Discrete Element Method

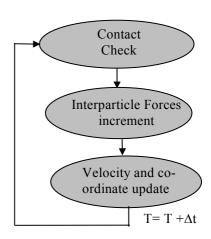

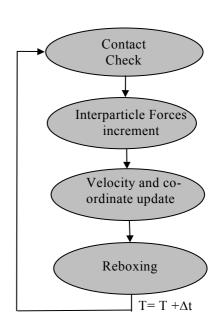

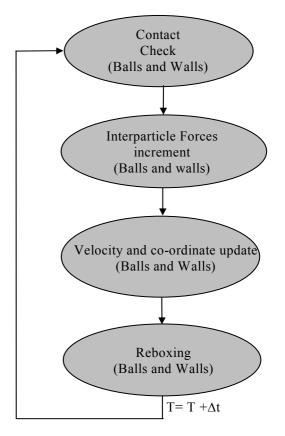

Cundall and his co-worker Strack [1][5][7] developed the Discrete Element Method (DEM) in the seventies to model the behaviour of granular materials. The method is based on the assumption that particles only exert forces on one another when they are in contact. A simulation starts by assuming some initial configuration of particle positions, and then computes which of the particles are touching. The simulation then proceeds by stepping in time, applying the sequence of operations in Figure 2–2 at each step. The force between

two particles can be calculated from the strength of the contact between them. The resultant force on a particle is the vector sum of the forces exerted by each of its neighbours. Once the resultant force on each particle has been computed, it is simple to compute the acceleration, the velocity and the position increment for each particle. Finally, the list of which particles are in contact must be recomputed. The force interaction, acceleration and movement of each particle are calculated individually at each time step. The assumptions underlying the

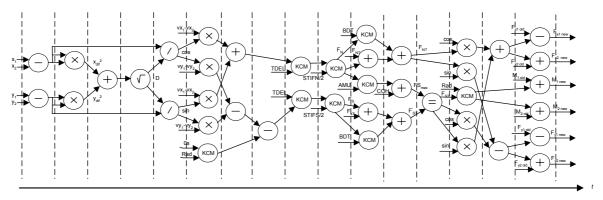

Figure 2-2 DEM Flow chart

method are only correct if no disturbance can travel beyond the immediate neighbours of a particle within one time step. This generally means that the time step must be limited to a very small value (of the order of milliseconds for the stiffness and density of a typical material, though using scaled stiffness or density can change its value). This restriction is due to the explicit nature of the method and it makes the DEM extremely computationally expensive, since many time steps are needed if the dynamic behaviour of the system is required to be modelled accurately.

This method has been widely used in many applications, such as silo flows [8], rock fracture and the collapse of buildings [9]. A detailed description of the three main steps involved in the DEM is given in the next section for a two-dimensional case. For the purpose of this explanation, the domain is assumed to be two dimensional, and the particles are assumed to circular discs. The extension to three dimensions is discussed in chapter 7.

#### 2.5.1 Contact Check

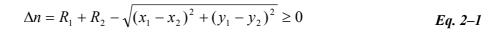

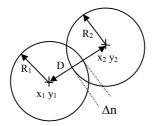

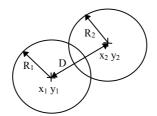

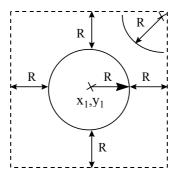

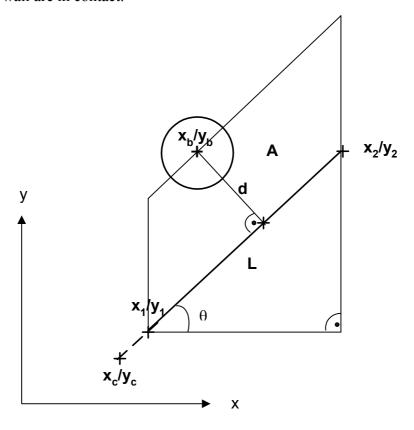

In order to detect if two particles are in contact the following equation has to be solved for circular discs in 2-D:

Figure 2–3 Balls in contact

Here  $x_i$  and  $y_i$  are the co-ordinates of each particle centre and  $R_1$  and  $R_2$  are the respective radii, D is the distance between the centres and  $\Delta n$  the separation or overlap of the two particles. If  $\Delta n$  is positive or zero, then the balls are in contact, whereas a negative value of  $\Delta n$  indicates that the balls are not in contact.

### 2.5.2 Inter-particle Forces Increment

Once the contact list for a particle has been established, the total force acting on it can be determined. For every contact identified between two particles, the resulting force can be calculated once the force-displacement law is known. For this study, the simplest possible force-displacement law is adopted: the resulting force between two balls is linearly proportional to the indentation  $\Delta n$  between the balls. (This is not exactly correct in reality, as the contact area will increase with the amount of contact thus rendering the force-displacement law non-linear. Although many advanced interaction laws, such as the Hertzian law, have been proposed [10], they add to the complexity to the calculations, but do not alter substantially the arguments put forward in this thesis). The force displacement law used for each ball is as follows:

$$F_{xi} = k_n \Delta n_{xi}$$

Eq. 2-2

$F_{yi} = k_s \Delta n_{yi}$  Eq. 2-3

$$M_i = F_{si} R$$

Eq. 2-4

where  $k_i$  is the stiffness (subscript n for normal and s for shear),  $n_{xi}$  and  $n_{yi}$  are respectively the x and y components of the current ball indentation against particle i,  $F_{xi}$  and  $Fy_i$  are the components of the force caused by the interaction with ball i,  $M_i$  is the moment acting on the current ball due to the i<sup>th</sup> ball,  $F_{si}$  is the shear force acting on the current ball due to the i<sup>th</sup> ball and R is the ball's radius. The index i runs from the first to the last ball on the present ball's adjacency list, so the resultant force on a ball is the vector sum of the forces caused by each contact with its neighbours.

$$F_x = \sum_i F_{xi} \qquad Eq. 2-5$$

$$F_y = \sum_i F_{yi} \qquad Eq. 2-6$$

$$M = \sum_{i} F_{si} R$$

Eq. 2–7

It should be noted that Eq. 2-7 is only correct if the rotation involved is small, since the direction of  $F_{si}$  changes with the rotation.

### 2.5.3 Velocity and Co-ordinate Update

Once the resultant forces of each ball have been calculated by summing the forces of all contacts in vectorial form for every ball, these forces can be used to find the new accelerations using Newton's second law:

$$a_x = \frac{F_x}{m}$$

Eq. 2-8

$$a_{y} = \frac{F_{y}}{m}$$

Eq. 2–9

Where  $F_x$  is the resultant force in the x-direction,  $F_y$  is the resultant force in the y-direction, m is the mass of the particle and  $a_x$  and  $a_y$  are the acceleration in the x and y-directions respectively.

These accelerations are integrated to obtain the velocities in the x and y directions as well as the rotational velocity using the moment of inertia of the particle I:

$$v_{x} = v_{x0} + a_{x}\Delta t$$

$$v_{y} = v_{y0} + a_{y}\Delta t$$

$$\dot{\theta} = \dot{\theta}_{0} + \left(\frac{M}{I}\right)\Delta t$$

Eq. 2-12

The time step, as is the case for all explicit time integration schemes, has to be limited to a small value in order to retain numerical stability. For the DEM, the constraint is that the time step must be sufficiently small that no disturbances can travel beyond one contact in one time step. The critical time step for each particle can be calculated from its stiffness and mass properties as shown in Eq. 2–13.

$$T_{critical} = 2\sqrt{\frac{mass}{stiffness}}$$

Eq. 2–13

The critical time step of the whole system is limited by the smallest of the critical time steps of the individual particles. The new coordinates can be found by adding the original coordinates to the incremental displacement obtained by integrating the calculated velocities.

$$u_{x} = u_{x0} + v_{x}\Delta t$$

Eq. 2–14

$$u_{y} = u_{y0} + v_{y}\Delta t$$

Eq. 2–15

$$\theta = \theta_{0} + \dot{\theta}\Delta t$$

Eq. 2–16

It should be noted that both displacements and accelerations are defined at the time points which are at the beginning and the end of the time steps, and the velocities are defined at the mid-point of the time intervals.

### 2.6 DEM Analysis

As can be seen from Figure 2–2 the DEM consists of three basic steps:

- 1. **Contact checking:** to detect the particles that are in contact

- 2. **Forces update:** to compute the resultant force applied to each particle by other particles in contact with it

- 3. **Velocity and coordinate update:** in order to recalculate the particles' new velocities and coordinates.

Issues governing the number of arithmetic operations and amount of computer time required for each of these stages are discussed in detail in the following sub-sections.

### 2.6.1 Contact Checking Analysis

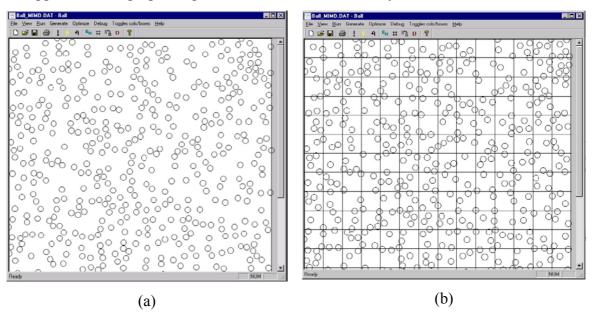

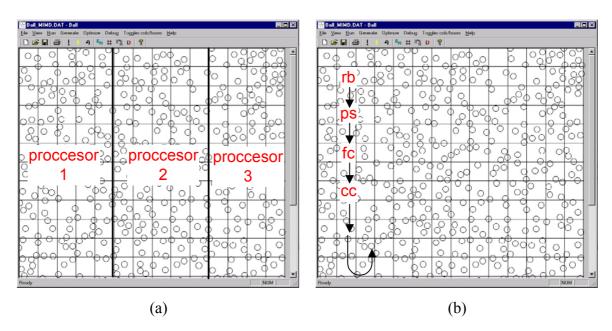

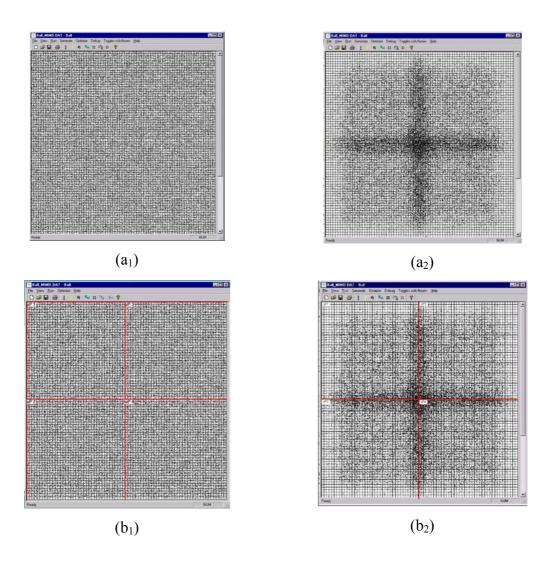

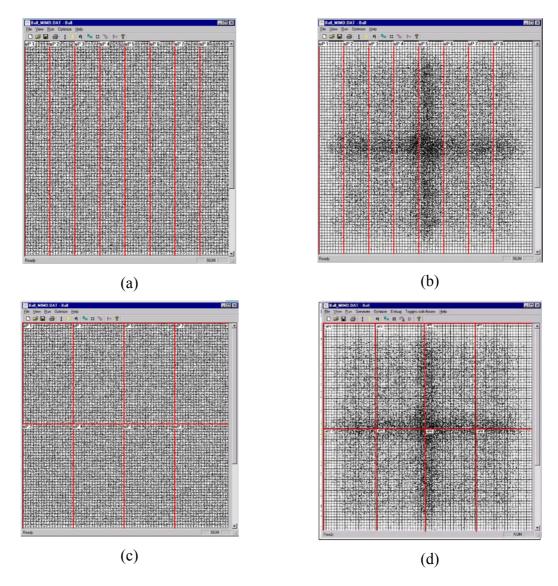

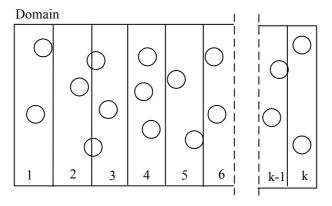

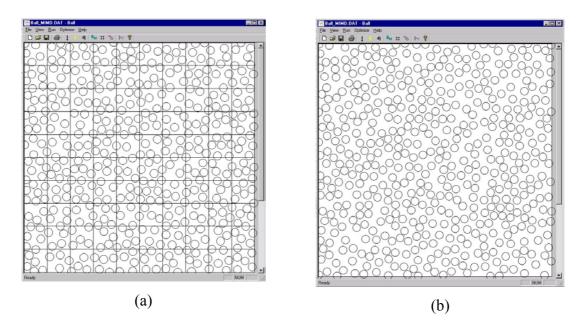

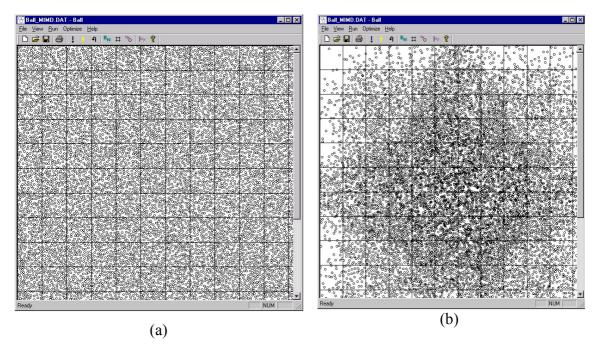

The identification of which particles are in contact with each is the most time consuming operation of the three stages. It requires that each possible pairing of balls be examined, which for N particles requires  $O(N^2)$  operations. Thus, for large problem sizes, contact identification dominates the complexity of the problem. Dividing the domain up into cells (see Figure 2–4) using the domain decomposition method can alleviate this. Each particle is tagged as belonging to a particular cell, and it will only be checked for contacts with

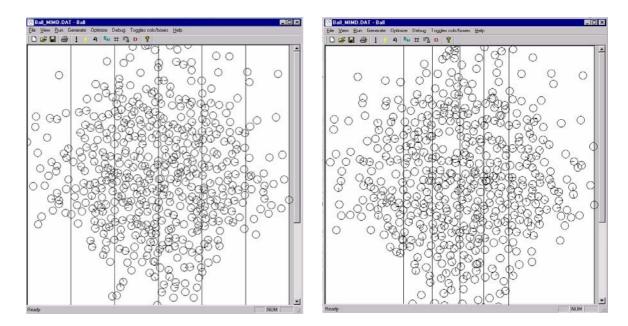

Figure 2–4 Screenshots of two syste . (a) Without grid (b) with grid

particles within the same cell and adjacent cells. If the number of particles per cell is c, then the execution time is proportional to  $\frac{N}{c}O(c^2)$ .

Occasionally a particle may transition from one cell to another, or may straddle the boundary between two cells. A new sub-step has to be included in the data flow of the DEM as *reboxing* of the particles is now necessary whenever a particle moves to an adjacent box (see Figure 2–5).

In order to illustrate the impact of the domain decomposition, a set of experiments was performed using the software described in the next chapter, in order to determine the CPU time spent by the software simulator on each of the steps of the DEM method. An example domain with 500 particles was generated and ran once with domain decomposition and once without. Table 2–1 shows the difference between the two cases. As can be seen, with the new *reboxing* step introduced in the data flow for the case where the domain is decomposed, the contact detection time falls dramatically and the total time needed to perform the contact detection plus reboxing is

Figure 2–5 Modified DEM flow chart with domain decomposition

much smaller than the time needed to produce the contact detection without grid.

**Table 2–1** Timing analysis for a system with 500 particles ran for 1000 time steps with and without a grid

| Time        | Forces Update | Coordinates Update | Contact check | Rebox  |

|-------------|---------------|--------------------|---------------|--------|

| t [No grid] | 1.64 s        | 0.313 s            | 70.39 s       | 0      |

| t [Grid]    | 1.64 s        | 0.313 s            | 2.23 s        | 0.13 s |

In addition to analysing the timing characteristics of the contact check stage, it is also necessary to analyse the arithmetic complexity of this stage. The number of arithmetic operations needed to compute Eq. 2–1 is given below in Table 2–2.

Table 2–2 Arithmetic operations needed for the contact check

|                      | Additions and | Multiplications | Square Roots |

|----------------------|---------------|-----------------|--------------|

|                      | Subtractions  |                 |              |

| Number of Arithmetic | 5             | 2               | 1            |

| operations           |               |                 |              |

#### 2.6.2 Forces Update Analysis

For every contact identified between two particles, the contact force has to be calculated. This is assumed to be linearly proportional to the indentation between the balls. The resultant force on a particle is the vector sum of the forces caused by each contact with its neighbours.

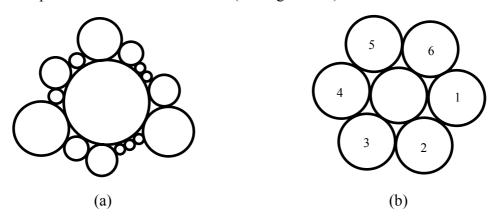

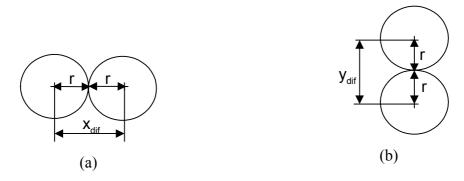

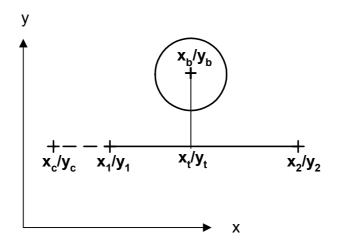

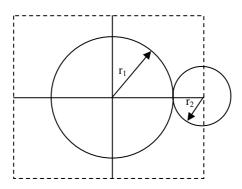

The model used throughout this thesis considers a granular medium with all of its particles having identical radius R. This greatly simplifies the hardware implementation of the algorithm, because it means that for a 2-D implementation, a particle can have a maximum of six other particles in contact with itself (see Figure 2–6).

Figure 2–6 Two cases of different number of balls in contact (a) Balls in contact with different radii (b) Balls in contact with the same radius

If the particles had varying radii (see Figure 2–6a) there could be in principle be an unlimited number of balls in contact (if  $R_{largest} \gg R_{average}$  and  $R_{smallest} \ll R_{average}$ , where  $R_{largest}$  is the larges radius in the system,  $R_{smallest}$  is the smallest radius in the system and  $R_{average}$  is the radius of the average sized particles). This would necessitate the use of complicated data structures, such as linked lists, which are difficult to handle efficiently in hardware.

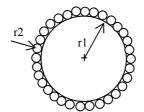

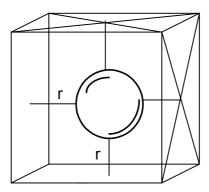

That a maximum of six discs can be in contact with a certain disc can be derived mathematically in a very simple manner (see Figure 2–7 and Eq. 2–17 and Eq. 2–18).

$$\alpha = \sin\left(\frac{R}{2 \times R}\right)^{-1} = 30^{\circ}$$

$$2 \times \alpha = 60 \Rightarrow \frac{360^{\circ}}{60^{\circ}} = 6$$

Eq. 2-18

**Figure 2–7** Geometrical deduction of the maximum number of balls in contact for balls of the same radius

Having all particles of the same radius R means that adjacency information can be represented by a very simple data structure (a 6xN matrix) and that the maximum number of interparticle forces computation required is 6N, for the worst case in which all particles have the maximum number of particles in contact.

After determining which particles are in contact, the forces and moments between the particles is calculated. The pseudo code for the calculation of the forces and moments is given below. As mentioned earlier, the forces between the two balls are assumed to be directly proportional to the amount of indentation between the two balls [7].

```

FOR Ball 1:last

WHILE Ball has balls in contact

x_{dif} = x_1 - x_2 (x-coordinate difference)

y_{dif} = y_1 - y_2 (y-coordinate difference)

D = \sqrt{{x_{dif}}^2 + {y_{dif}}^2} (distance between particle centroids)

\sin(\alpha) = \frac{y_{dif}}{D}

\cos(\alpha) = \frac{x_{dif}}{D}

v_{xdif} = v_{x1} - v_{x2} (x-direction relative velocity)

v_{vdif} = v_{v1} - v_{v2} (y-direction relative velocity)

D_N = \left[ \left( v_{vdif} \times \cos(\alpha) \right) + \left( v_{vdif} \times \sin(\alpha) \right) \right] \times \Delta t

D_{S} = \left[ \left( v_{xdif} \times \sin(\alpha) \right) + \left( v_{ydif} \times \cos(\alpha) \right) - \left( \theta_{s1} \times R_{1} \right) - \left( \theta_{s2} \times R_{2} \right) \right] \times \Delta t

D_{FN} = D_N \times k_N / 2 (Incremental normal force)

D_{FS} = D_S \times k_S / 2 (Incremental shear force)

F_{\scriptscriptstyle N} = F_{\scriptscriptstyle Ncontact} + D_{\scriptscriptstyle FN} (New total normal force in contact)

F_{NT} = F_N + (D_{FN} \times BDT) (BDT is the damping contribution)

F_{\scriptscriptstyle S} = F_{\scriptscriptstyle Scontact} + D_{\scriptscriptstyle FS} (New total shear force in contact)

(Restoring of normal and shear force in x and y

directions)

F_x = F_{NT} \times \cos(\alpha) + F_{ST} \times \sin(\alpha) (Restore normal force to x)

F_{v} = F_{NT} \times \sin(\alpha) - F_{ST} \times \cos(\alpha) (Restore shear force to y)

M = F_{ST} \times R (Compute moment)

F_{xnew1} = F_{xold1} - F_x (Add force increment in x direction)

F_{\mathit{ynew1}} = F_{\mathit{yold1}} - F_{\mathit{y}} (Add force increment in y direction)

M_{newl} = M_{old1} - M (Add moment increment)

F_{xnew2} = F_{xold2} - F_x (Same for 2<sup>nd</sup> particle)

```

$$F_{ynew2} = F_{yold2} - F_y$$

$$M_{new2} = M_{old2} - M$$

Next Ball in contact

Next Ball

Where  $\Delta t$  is the time step and  $k_n$  and  $k_s$  are the normal and shear stiffness of the system. Table 2–3 gives an overview of the total number of arithmetic operations needed to compute the force between two balls in contact.

*Table 2–3 Arithmetic operations of the force update function*

|                | Additions and | Multiplications | Divisions | Square Roots |

|----------------|---------------|-----------------|-----------|--------------|

|                | Subtractions  |                 |           |              |

| Number of      | 20            | 18              | 2         | 1            |

| Arithmetic ops |               |                 |           |              |

In addition to the equations given above, the maximum shear force before the particles start sliding is computed ( $F_{smax}$ ). In the case that the shear force ( $F_s$ ) is larger than this maximum shear force ( $F_{smax}$ ), the particle will slide instead of rotating with the particle in contact, and the shear force will be set equal to the absolute value of  $F_{smax}$  preserving the sign of  $F_s$ .

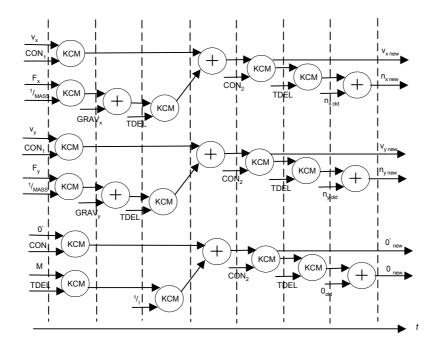

#### 2.6.3 Coordinate Update Calculation Analysis

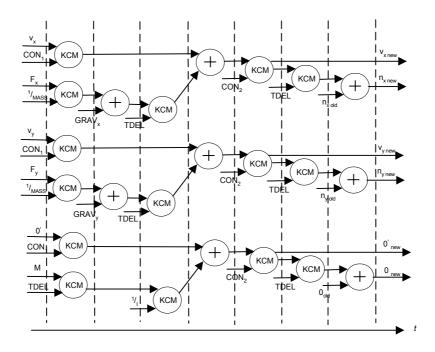

Movement update entails the solution of Newton's second law for each of the N particles. This requires O(N) operations. This is the fastest of the three stages that are performed for each time step. The equations that describe how the particles' new velocities ( $v_{xnew}$ ,  $v_{ynew}$ , and  $\theta'_{snew}$ ) and coordinates ( $v_{xnew}$ ,  $v_{ynew}$  and  $v_{ynew}$ ) are calculated are given below:

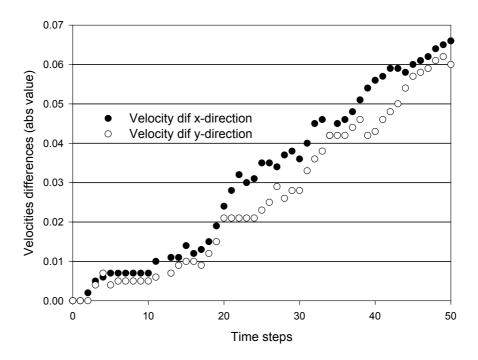

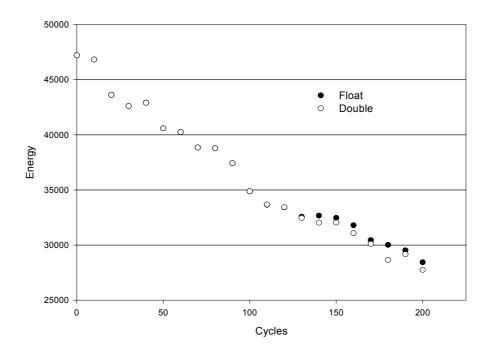

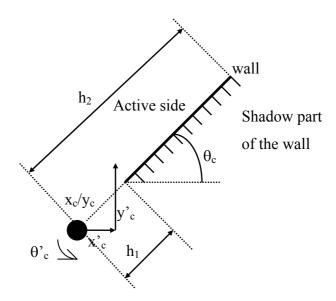

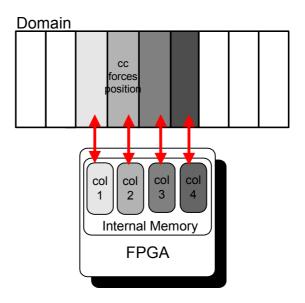

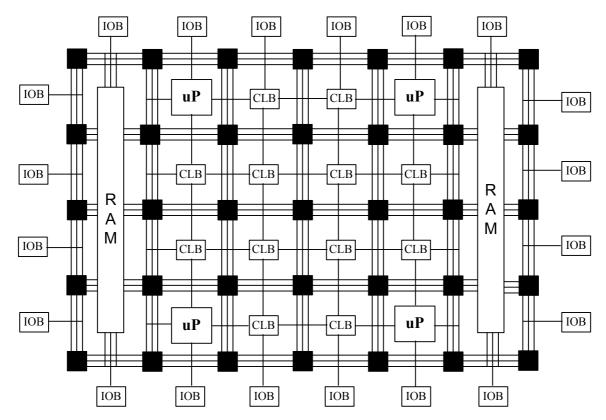

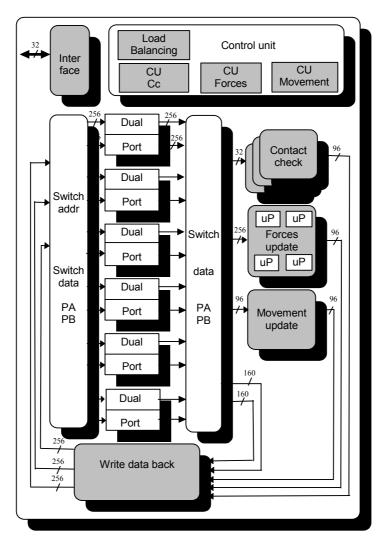

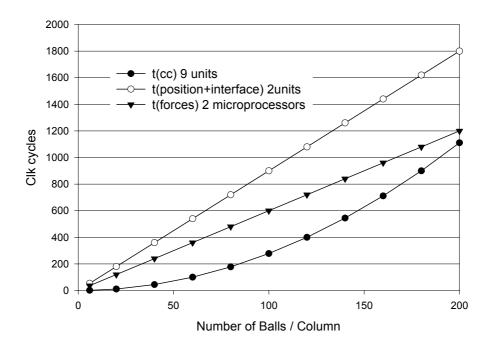

FOR Ball 1 until last