# REAL-TIME FPGA-BASED CO-SIMULATION OF LARGE SCALE POWER SYSTEMS

by

#### **CONGHUAN YANG**

A thesis submitted to

The University of Birmingham for the degree of

DOCTOR OF PHILOSOPHY

Department of Electronic, Electrical and Systems Engineering School of Engineering University of Birmingham September 2017

# UNIVERSITY<sup>OF</sup> BIRMINGHAM

## **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

## **ABSTRACT**

Real-time Electromagnetic Transient (EMT) simulation plays an important role in the planning, operation and analysis of electrical power systems. However, with the rapid increase of size and complexity of modern electrical power systems, 1) the simulation accuracy and 2) the capability of simulating large power systems have become two conflicting objectives. Sacrificing accuracy can lead to inappropriate component designs (for example incorrect insulation level due to inaccurate simulation results), incorrect control & relay settings and less optimized planning (for example less optimized planning & design of harmonic filters due to inaccurate simulation of harmonics) [1, 2]. Sacrificing efficiency can discourage technology innovation, slow down concept validation and the speed of product prototyping. It is therefore highly desirable and advantageous that the accuracy and the efficiency of simulating large power systems can be achieved simultaneously. This thesis proposes a new co-simulation platform by integrating Field Programmable Gate Array (FPGA) with Real-Time Digital Simulator (RTDS) to achieve these two conflicting objectives.

As the basis of the co-simulation platform, a library of power system components using EMT models is developed in FPGA, including most of the common power system elements (synchronous machines, transmission lines, passive elements, voltage/current sources and circuit breakers) and control systems (excitation systems and governor systems). The

modelling and hardware implementation of each component are described and simulation results are compared with SIMULINK to verify the accuracy of the developed models.

By integrating FPGA with RTDS, the FPGA-RTDS co-simulator is developed which combines the advantages of 1) paralleled architecture and high clock speed from FPGA and 2) better modelling flexibility and user-friendly Graphical User Interface (GUI) from RTDS together. The use of detailed EMT models for all electrical components and control systems achieves a high level of accuracy of simulation, and the interface error is eliminated in the proposed method comparing with the conventional method of interfacing Transient Stability (TS) program with EMT program as only the EMT models are used on both RTDS and FPGA sides. Deeply pipelined and massively paralleled computation algorithms in FPGA are developed. Real-time EMT simulation of power systems with more than 400 nodes is presented to demonstrate the simulation capability. Comparisons are made with SIMULINK and RTDS to verify the accuracy of the proposed co-simulator. Modular design of the hardware components and the pipelined computations significantly facilitate the system expansion with minimized hardware requirement.

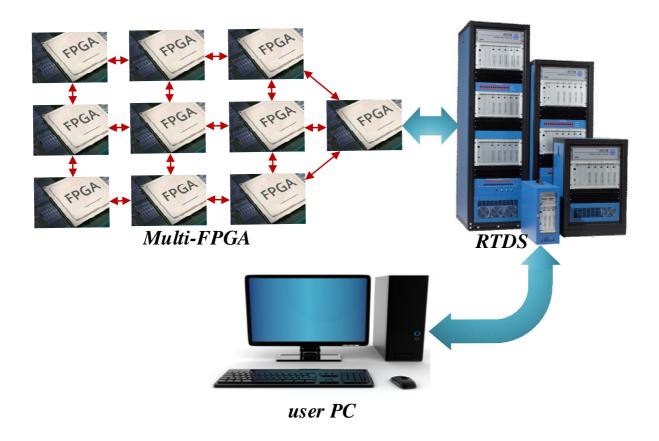

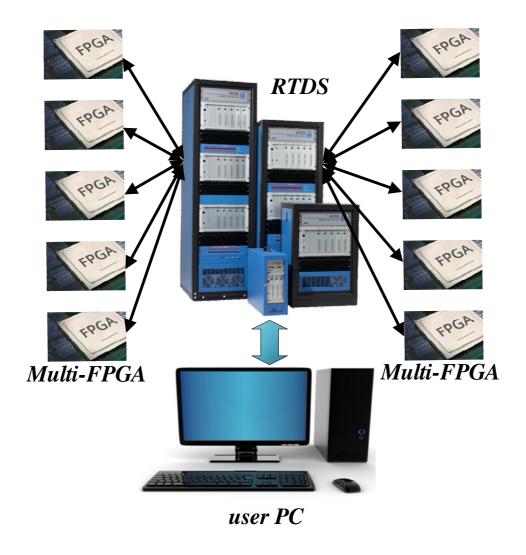

To further improve the simulation capability of the proposed co-simulator, multi-FPGA structure is introduced. In this structure, the large power system to be simulated is partitioned into subsystems and each FPGA simulates one subsystem. The partition of the system is carried out in such a way that each FPGA and RTDS are decoupled and run in parallel. Thus great expandability is achieved as the system size can be easily expanded by

adding additional FPGAs without affecting the existing ones. A case study utilizing 10 FPGAs to simulate a large scale power system with more than 4000 nodes is presented to demonstrate the capability of the proposed co-simulator.

# **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my PhD supervisor Professor Xiao-Ping Zhang. It was his innovative ideas that motivated me to start my PhD topic. His encouragement and support helped me through the four years of study. The research would not be the same level as it is today without his help.

I also want to thank all my colleagues from the research group for the interesting discussions and memorable dinners. They made my research years more enjoyable.

I would like to extend my deepest gratitude to my boyfriend and colleague, Dr. Ying Xue. Without his encouragement, understanding and support, this thesis would not have been completed. I want to thank all my friends for their company and friendship over all these years.

Finally I would like to express my gratitude to my parents for their love, support and understanding since the first day of my life. Without you, I would not be the person I am today.

# TABLE OF CONTENTS

| Chapter 1 | INTRODUCTION                                                 | 1       |

|-----------|--------------------------------------------------------------|---------|

| •         | search Background                                            |         |

| 1.1.1     | Evolution of Modern Electrical Power Systems                 |         |

| 1.1.2     | The Need for Accurate Simulation Technology                  |         |

|           |                                                              |         |

| 1.1.3     | The Need for the Efficient Simulation of Larger Systems      |         |

| 1.1.4     | Opportunities and Challenges                                 |         |

| 1.2 Lite  | erature Review                                               | 7       |

| 1.2.1     | Improvement of Simulation Capability for Large Power Systems | 8       |

| 1.2.2     | Improvement of Simulation Accuracy                           | 10      |

| 1.2.3     | FPGA Technology                                              | 14      |

| 1.2.4     | Application of FPGA in Real-Time Simulation                  | 18      |

| 1.3 Pro   | oject Objective, Contributions and Thesis Outline            | 20      |

| 1.3.1     | Project Objectives                                           | 20      |

| 1.3.2     | Contributions of the Thesis                                  | 21      |

| 1.3.3     | Thesis Outline                                               | 21      |

| 1.3.4     | Logical Relationships between Chapters                       | 23      |

| Chapter 2 | MODELLING AND HARDWARE IMPLEMENTATION OF                     | F POWER |

| SYSTEM E  | LEMENTS                                                      | 24      |

| 0.1       |                                                              | 2.4     |

|           | roduction                                                    |         |

| 2.2 Pov   | wer System Elements                                          | 24      |

| 2.2.1     | Synchronous Machines                                         | 24      |

| 2.2.2     | Transmission Lines                                           | 45      |

| 2.2.3     | Passive Elements56                                                          |

|-----------|-----------------------------------------------------------------------------|

| 2.2.4     | Voltage and Current Sources63                                               |

| 2.2.5     | Circuit Breakers                                                            |

| 2.2.6     | Loads67                                                                     |

| 2.3 P     | ower System Controllers67                                                   |

| 2.3.1     | Excitation System                                                           |

| 2.3.2     | Governor/Turbine System80                                                   |

| 2.4 N     | Iodel Verification84                                                        |

| 2.4.1     | Case 1: Synchronous Machine with Constant Excitation and Governor Inputs 84 |

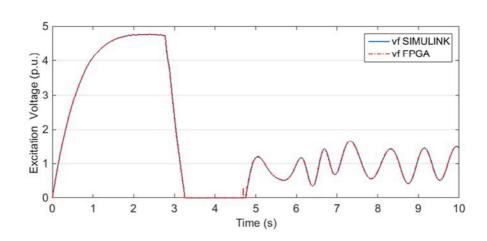

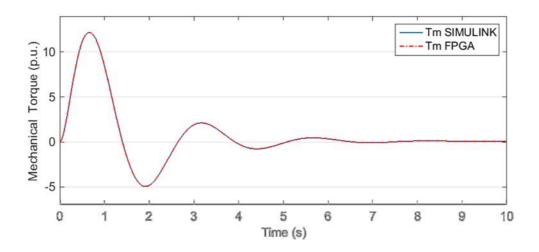

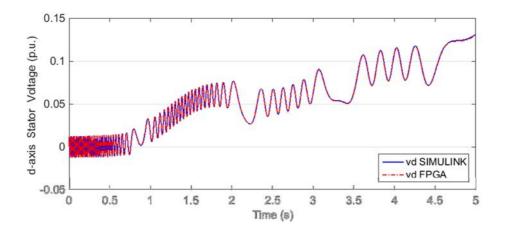

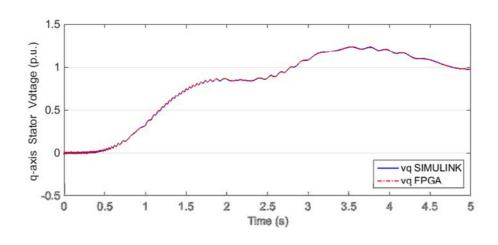

| 2.4.2     | Case 2: Synchronous Machine with Excitation and Governor Systems87          |

| 2.4.3     | Case 3: Model Verification of Transmission Lines, Passive Elements, Voltage |

| Sourc     | es and Circuit Breakers91                                                   |

| 2.5 S     | ummary96                                                                    |

| Chapter 3 | FPGA BASED REAL-TIME EMT SIMULATOR97                                        |

| 3.1 Ir    | itroduction97                                                               |

| 3.2 C     | omputational Architecture97                                                 |

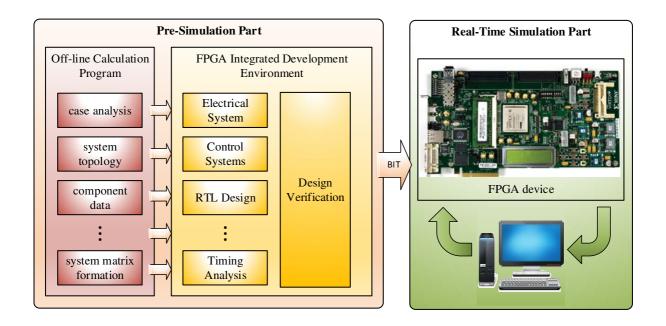

| 3.2.1     | Pre-Simulation Part98                                                       |

| 3.2.2     | Real-Time Simulation Part                                                   |

| 3.3 S     | imulator Global Controller104                                               |

| 3.3.1     | Module Coordination                                                         |

| 3.3.2     | Hardware Implementation                                                     |

| 3.4 P     | ower System Solver106                                                       |

| 3.4.1     | Network Solution                                                            |

| 3.4.2     | Non-Linear Elements: Compensation Method                                    |

| 3.4.3     | Hardware Implementation                                                     |

| 3.5    | Cas  | se Study                                         | 114   |

|--------|------|--------------------------------------------------|-------|

| 3.     | .5.1 | Case 1                                           | 114   |

| 3.     | .5.2 | Case 2                                           | 118   |

| 3.6    | Sur  | nmary                                            | 121   |

| Chapte | er 4 | REAL-TIME FPGA-RTDS CO-SIMULATOR                 | 122   |

| 4.1    | Inti | roduction                                        | 122   |

| 4.2    | FP   | GA vs RTDS                                       | 122   |

| 4.3    | Arc  | chitecture of the FPGA-RTDS Co-Simulator         | 123   |

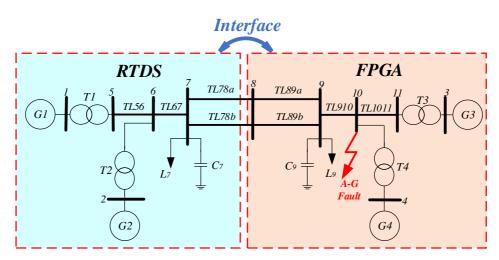

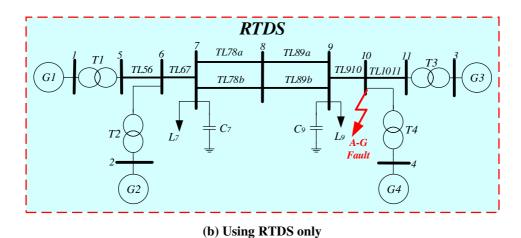

| 4.     | .3.1 | Study System & External System                   | 124   |

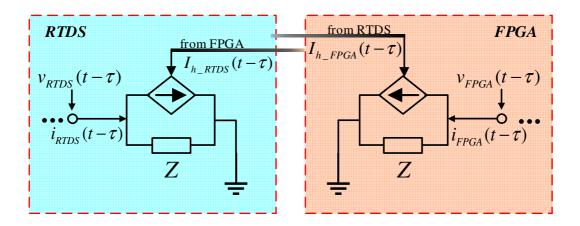

| 4.     | .3.2 | Interface Design                                 | 126   |

| 4.     | .3.3 | Parallel Computation Schemes                     | 129   |

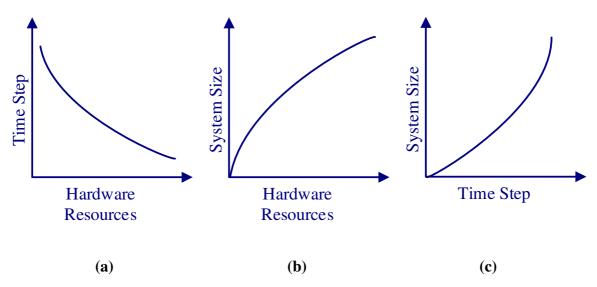

| 4.     | .3.4 | Platform Expandability                           | 133   |

| 4.4    | Cas  | se Study                                         | 135   |

| 4.     | 4.1  | Case 1                                           | 135   |

| 4.     | .4.2 | Case 2                                           | 140   |

| 4.     | 4.3  | Case 3                                           | 144   |

| 4.     | 4.4  | Discussions                                      | 148   |

| 4.5    | Sur  | nmary                                            | 150   |

| Chapte | er 5 | SIMULATION OF LARGE SCALE POWER SYSTEMS USING MU | ILTI- |

| FPGA   | BASI | ED CO-SIMULATOR                                  | 151   |

| 5.1    | Intı | roduction                                        | 151   |

| 5.2    | Exp  | pansion to Multi-FPGA                            | 151   |

| 5.3    | Me   | thodology of Network Partition                   | 152   |

| 5.4    | Inte | erface Design                                    | 154   |

| 5.5    | Sin  | gulator Canability                               | 157   |

| 5.6 Cas     | se study                                           | 9 |

|-------------|----------------------------------------------------|---|

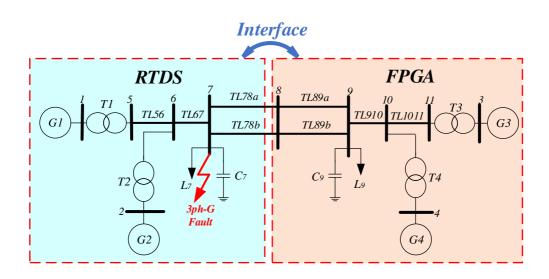

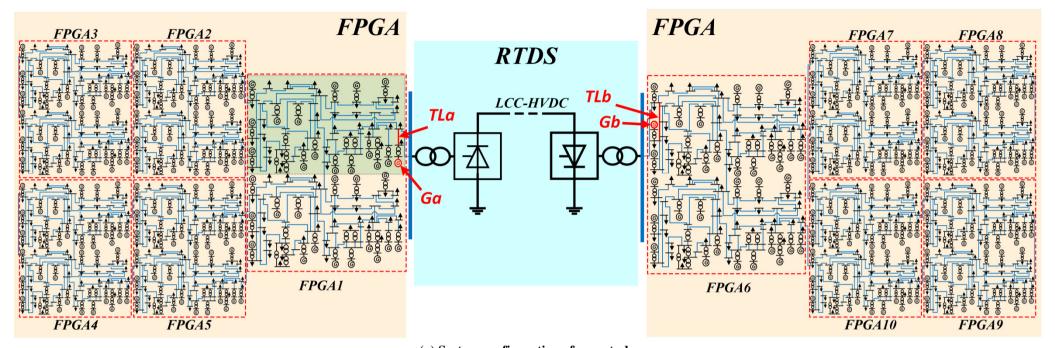

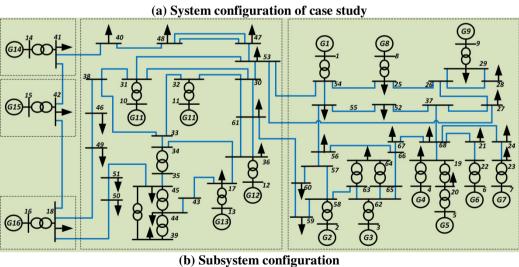

| 5.6.1       | Network Configuration                              | 9 |

| 5.6.2       | Hardware Implementation                            | 1 |

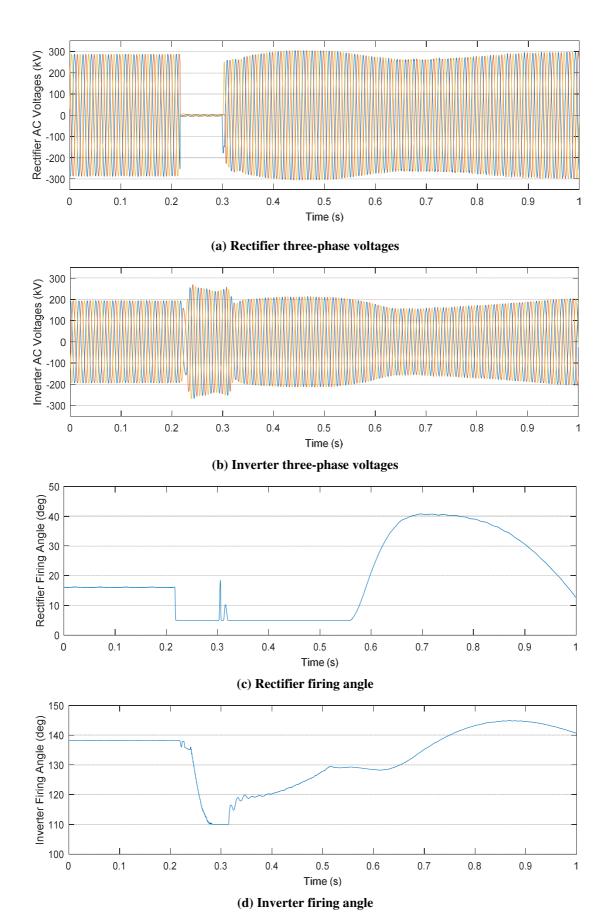

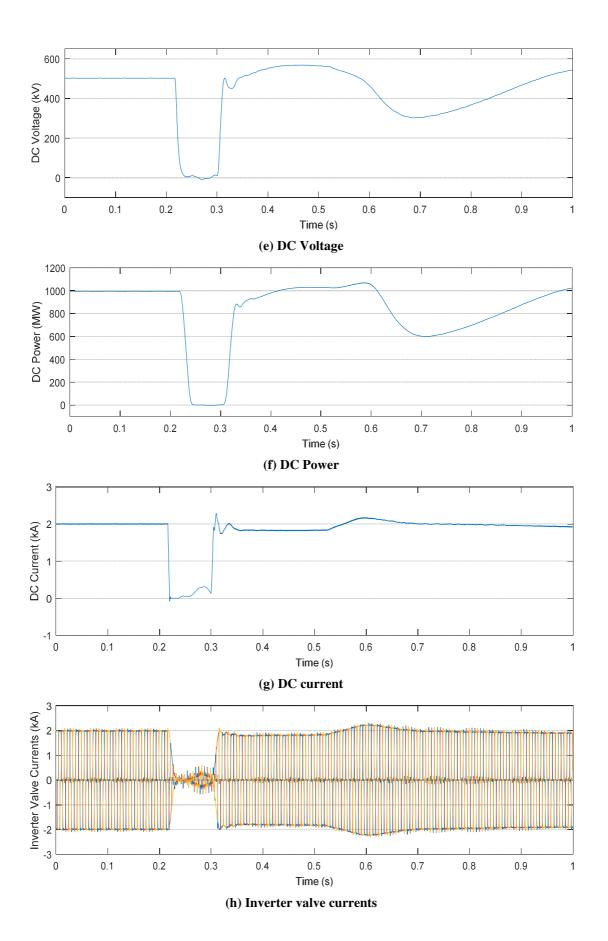

| 5.6.3       | Simulation Results                                 | 2 |

| 5.6.4       | Discussions                                        | 0 |

| 5.7 Sur     | nmary17                                            | 1 |

| Chapter 6   | CONCLUSIONS AND FUTURE WORKS                       | 2 |

| 6.1 Con     | nclusions                                          | 2 |

| 6.2 Fut     | ure Work                                           | 6 |

| LIST OF PU  | UBLICATIONS                                        | 7 |

| REFERENC    | EES                                                | 9 |

| Appendix A  | . Data of Case Study in Chapter 2                  | 0 |

| Appendix B. | Data of Two-Area Four-Machine Power System [147]19 | 3 |

| Appendix C. | Data of IEEE 68-Bus, 16-Machine System [154]19     | 4 |

| Appendix D  | . Xilinx ISE Design Suite Environment              | 9 |

| Appendix E. | Sample VHDL Codes                                  | 7 |

# LIST OF FIGURES

| FIGURE 1-1 INSTALLED CAPACITY OF RENEWABLE SOURCES IN UK [27]        | 2  |

|----------------------------------------------------------------------|----|

| FIGURE 1-2 GENERAL FPGA ARCHITECTURE                                 | 17 |

| FIGURE 2-1 BLOCK DIAGRAM REPRESENTATION OF SYNCHRONOUS MACHINE       | 25 |

| FIGURE 2-2 SYNCHRONOUS MACHINE SCHEMATIC                             | 26 |

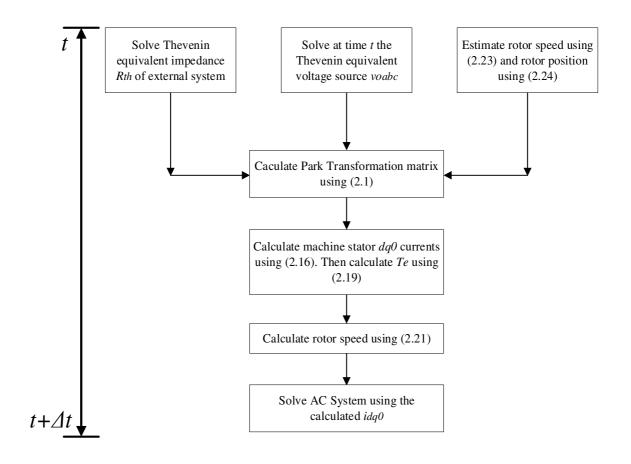

| FIGURE 2-3 SOLUTION STEPS FOR SYNCHRONOUS MACHINE                    | 34 |

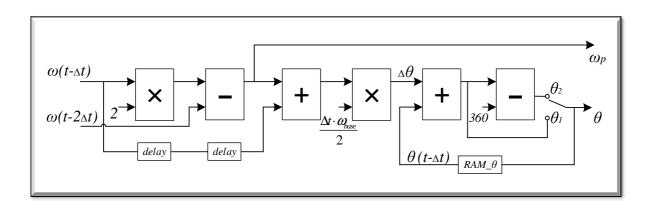

| FIGURE 2-4 ROTOR SPEED AND POSITION PREDICTION MODULE                | 35 |

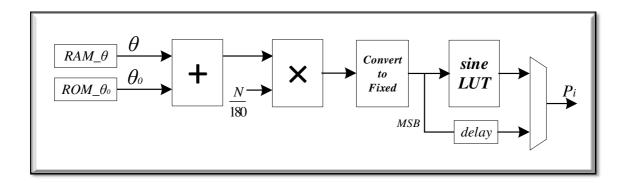

| FIGURE 2-5 PARK TRANSFORMATION MODULE                                | 36 |

| FIGURE 2-6 READ-ONLY MEMORY OF PARK TRANSFORMATION MODULE            | 37 |

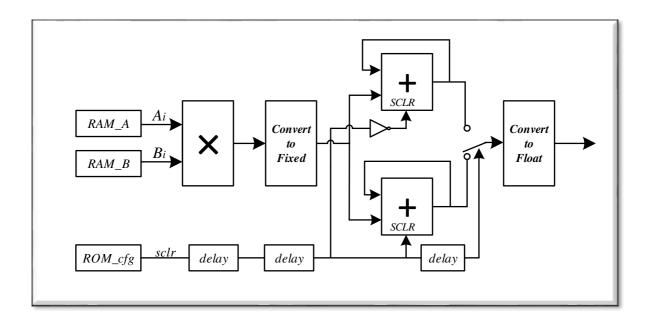

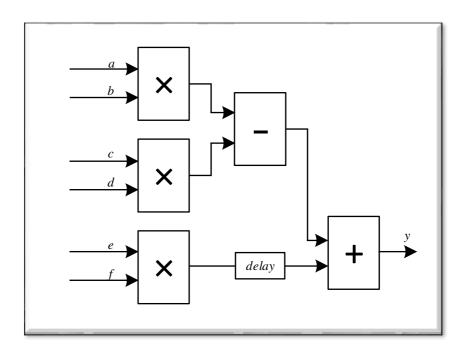

| FIGURE 2-7 MATRIX MULTIPLICATION MODULE                              | 38 |

| FIGURE 2-8 XY MATRIX FORMAT                                          | 41 |

| FIGURE 2-9 STATOR CURRENT SOLVING MODULE                             | 43 |

| FIGURE 2-10 ELECTROMAGNETIC TORQUE & ROTOR SPEED MODULE              | 44 |

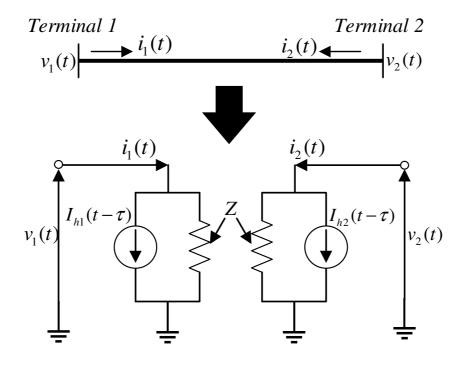

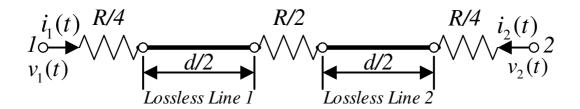

| FIGURE 2-11 EQUIVALENT CIRCUIT FOR LOSSLESS TRANSMISSION LINE        | 47 |

| FIGURE 2-12 REPRESENTATION OF TRANSMISSION LINE WITH LOSSES          | 47 |

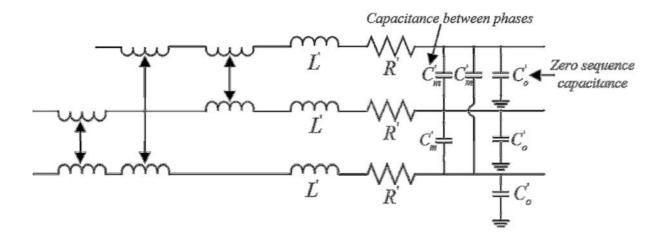

| FIGURE 2-13 A SEGMENT OF THREE-PHASE MUTUALLY COUPLED LINE [42]      | 49 |

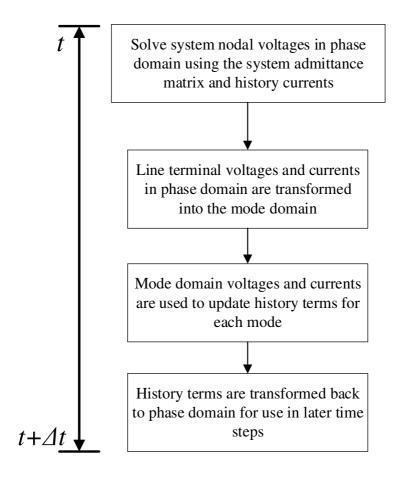

| FIGURE 2-14 SOLUTION STEPS FOR MULTIPHASE COUPLED TRANSMISSION LINES | 53 |

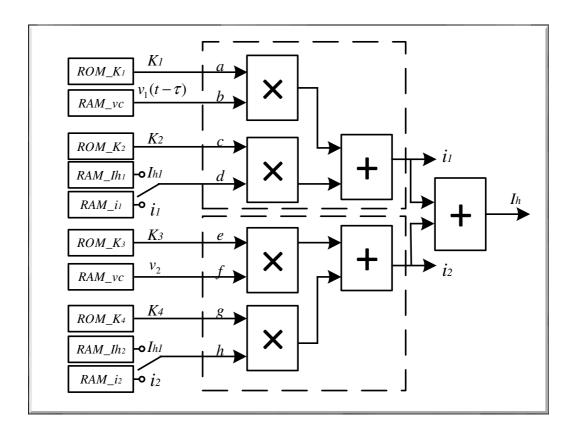

| FIGURE 2-15 TRANSMISSION LINE MODULE                                 | 55 |

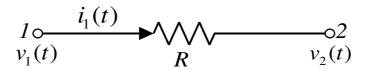

| FIGURE 2-16 RESISTOR BRANCH                                          | 56 |

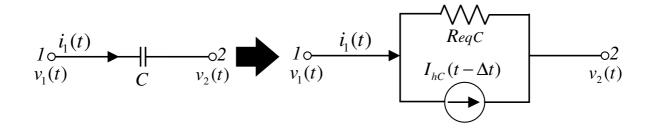

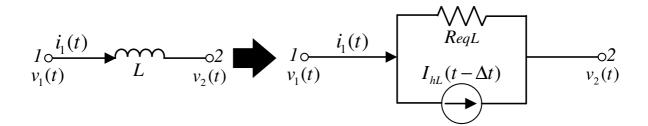

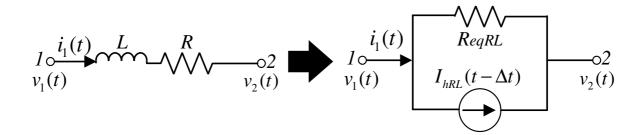

| FIGURE 2-17 CAPACITOR BRANCH                                         | 57 |

| FIGURE 2-18 INDUCTOR BRANCH                                          | 58 |

| Figure 2-19 Series <i>RL</i> branch                                  | 59 |

| FIGURE 2-20 PASSIVE ELEMENTS MODULE                                  | 62 |

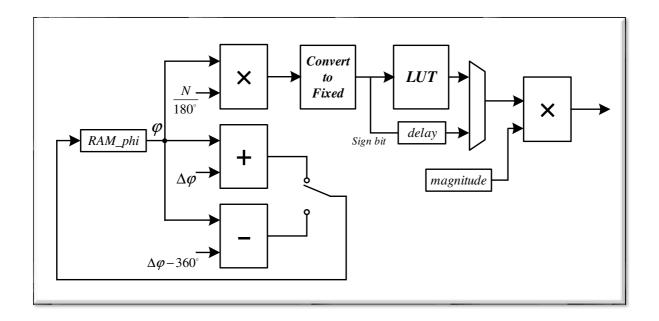

| FIGURE 2-21 SOURCE MODULE                                            | 65 |

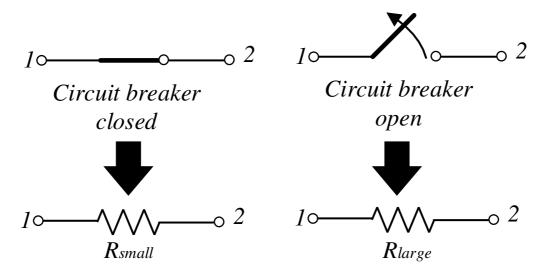

| FIGURE 2-22 CIRCUIT BREAKER MODEL                                    | 66 |

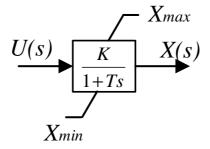

| FIGURE 2-23 GENERIC TRANSFER FUNCTION BLOCK                                     | 68  |

|---------------------------------------------------------------------------------|-----|

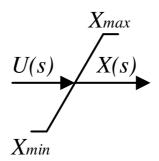

| FIGURE 2-24 NON-WINDUP LIMITER                                                  | 70  |

| FIGURE 2-25 WINDUP LIMITER                                                      | 71  |

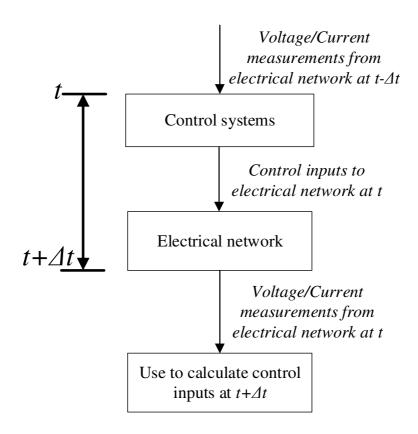

| FIGURE 2-26 INTERFACE BETWEEN CONTROL SYSTEM AND ELECTRICAL NETWORK             | 72  |

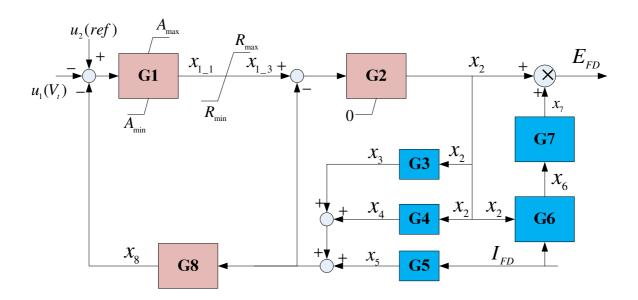

| FIGURE 2-27 BLOCK DIAGRAM REPRESENTATION OF AC1A EXCITER BLOCK                  | 74  |

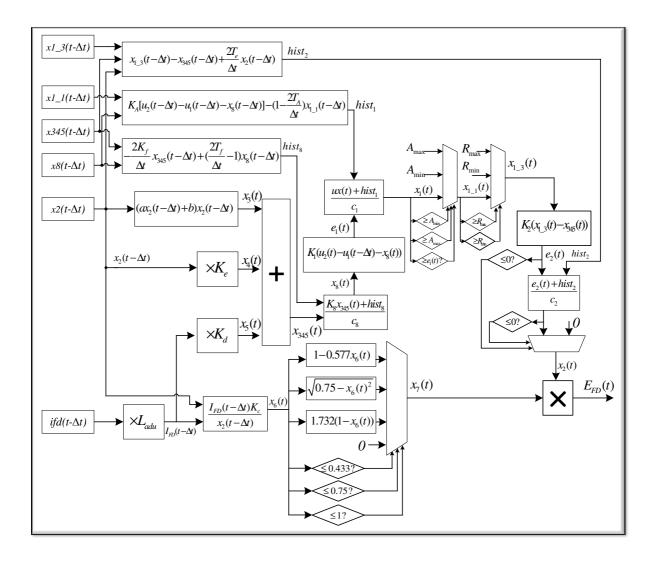

| FIGURE 2-28 SOLUTION STEPS FOR EXCITATION SYSTEM                                | 77  |

| FIGURE 2-29 EXCITATION MODULE                                                   | 77  |

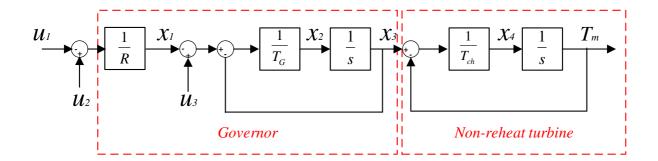

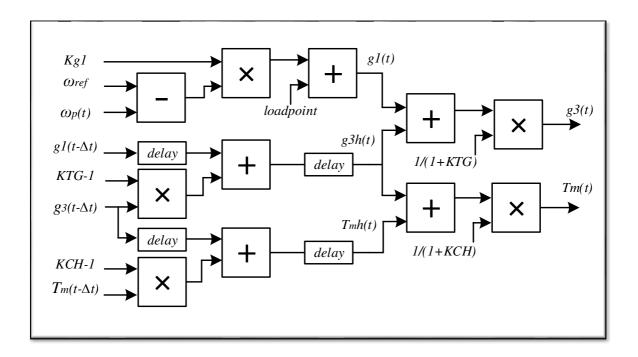

| FIGURE 2-30 GOVERNOR/TURBINE SYSTEMS                                            | 80  |

| FIGURE 2-31 SOLUTION STEPS FOR GOVERNOR/TURBINE SYSTEM                          | 82  |

| FIGURE 2-32 GOVERNOR MODULE                                                     | 83  |

| FIGURE 2-33 VERIFICATION OF SYNCHRONOUS MACHINE MODEL                           | 84  |

| FIGURE 2-34 STARTING PROCESS FOR SYNCHRONOUS MACHINE WITH CONSTANT EXCITATION   |     |

| VOLTAGE AND MECHANICAL TORQUE.                                                  | 86  |

| FIGURE 2-35 VERIFICATION OF CONTROL SYSTEMS FOR SYNCHRONOUS MACHINE             | 87  |

| FIGURE 2-36 STARTING PROCESS FOR SYNCHRONOUS MACHINE WITH EXCITATION SYSTEM AND |     |

| GOVERNOR SYSTEM                                                                 | 90  |

| FIGURE 2-37 THREE PHASE DIAGRAM OF TEST SYSTEM                                  | 91  |

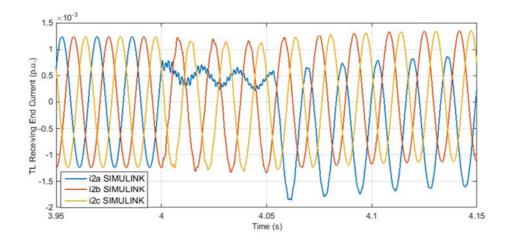

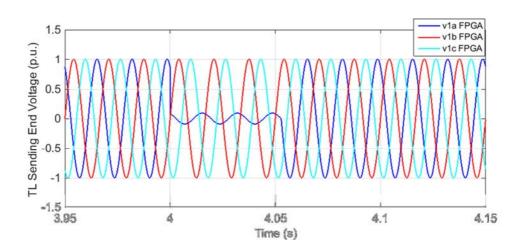

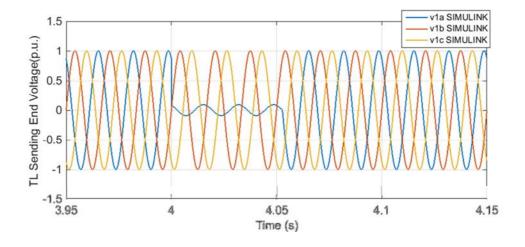

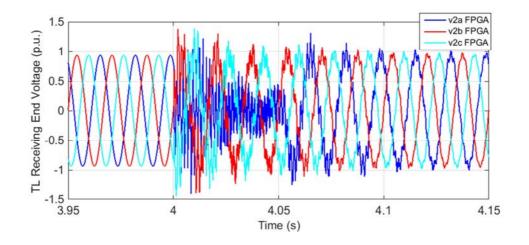

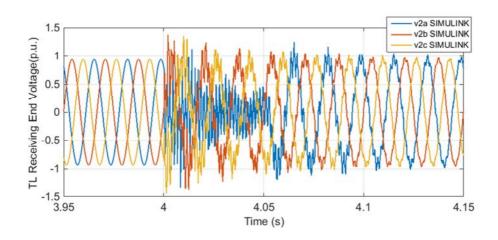

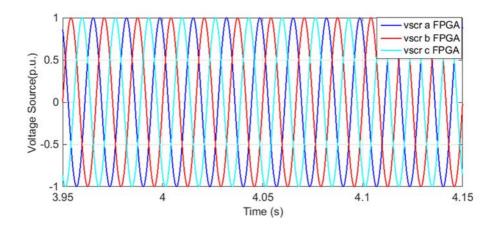

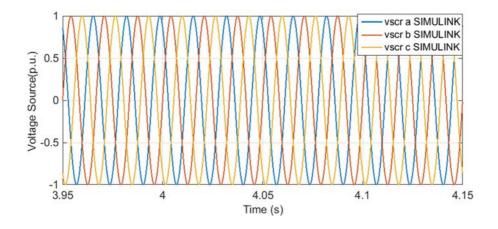

| FIGURE 2-38 COMPARISONS OF SIMULATION RESULTS OF THE TEST SYSTEM                | 95  |

| FIGURE 3-1 COMPUTATIONAL ARCHITECTURE                                           | 98  |

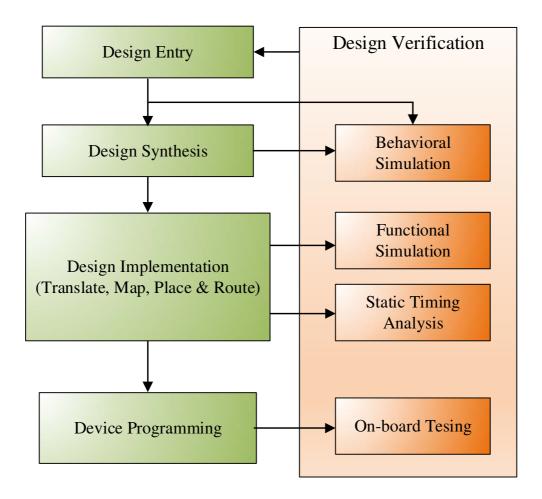

| Figure 3-2 Design flow                                                          | 99  |

| FIGURE 3-3 COMPUTATION SCHEME OF REAL-TIME SIMULATION PART                      | 101 |

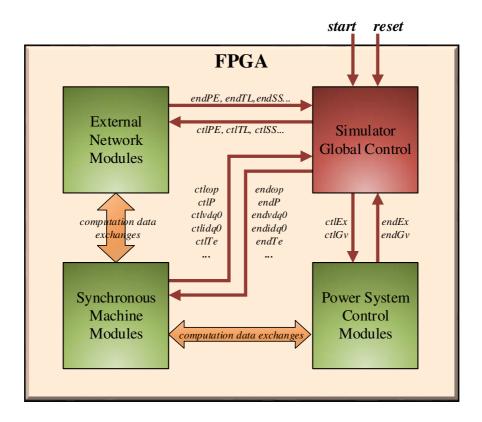

| FIGURE 3-4 COMMUNICATION SIGNALS BETWEEN MODULES                                | 104 |

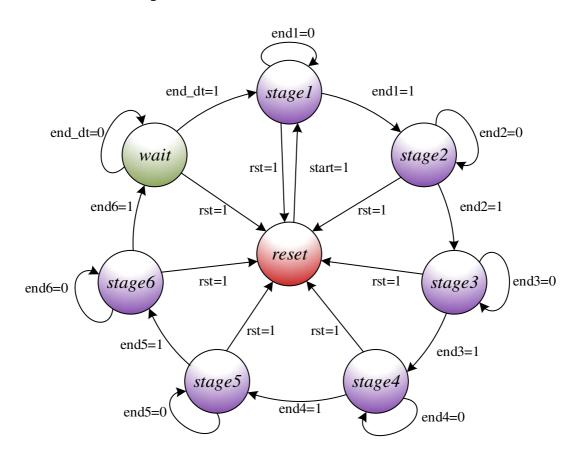

| FIGURE 3-5 GLOBAL CONTROL MODULE FSM                                            | 105 |

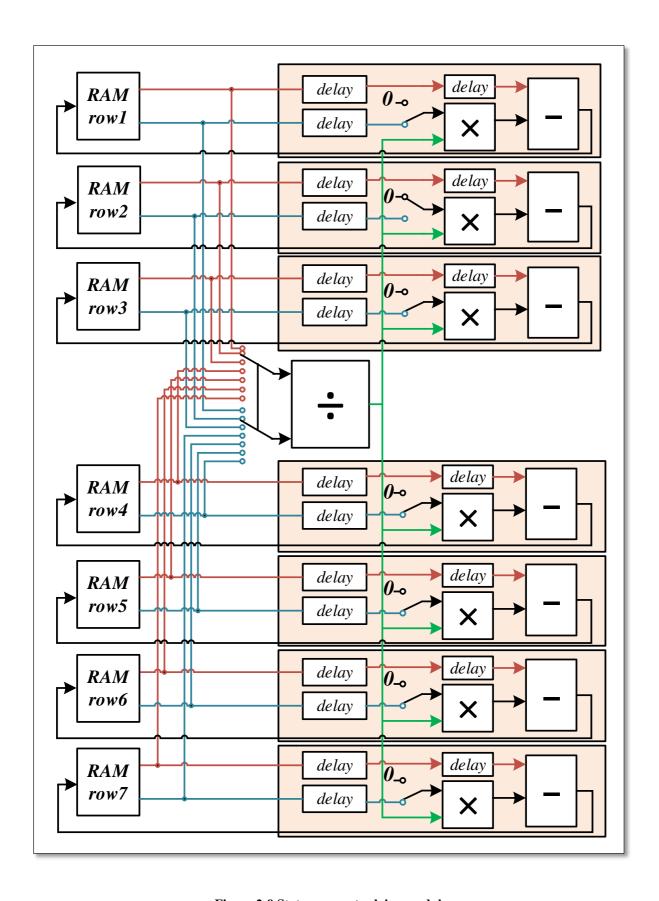

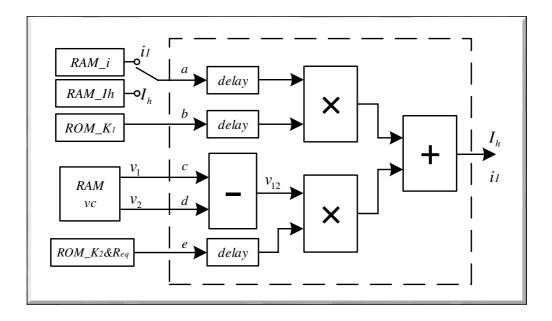

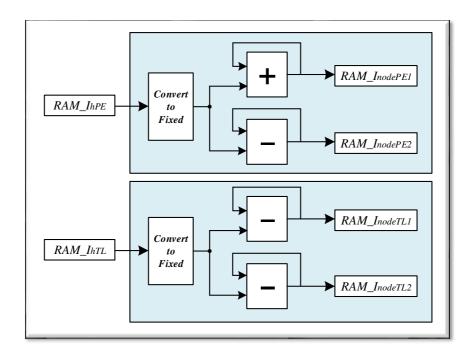

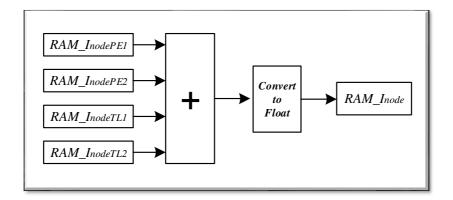

| FIGURE 3-6 HARDWARE IMPLEMENTATION OF HISTORY CURRENT FORMATION SUBMODULE       | 110 |

| FIGURE 3-7 HARDWARE IMPLEMENTATION OF CALCULATING NODAL CURRENT INJECTIONS      | 111 |

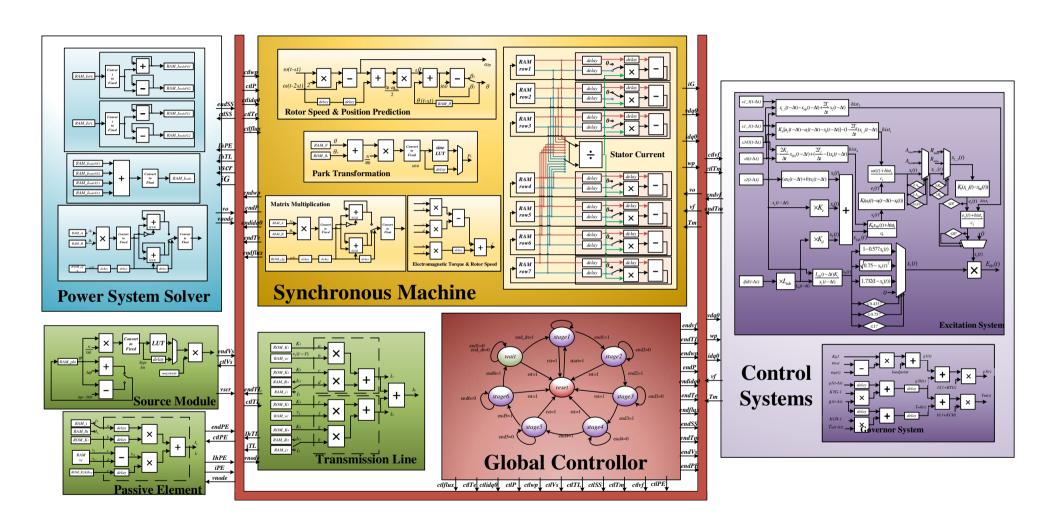

| FIGURE 3-8 DETAILED HARDWARE ARCHITECTURE OF THE FPGA-BASED EMT SIMULATOR       | 113 |

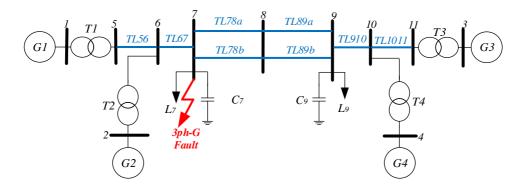

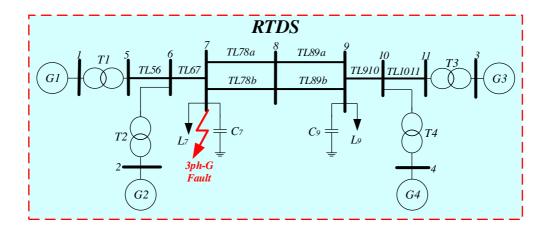

| FIGURE 3-9 SINGLE-LINE DIAGRAM OF CASE STUDY 1                                  | 114 |

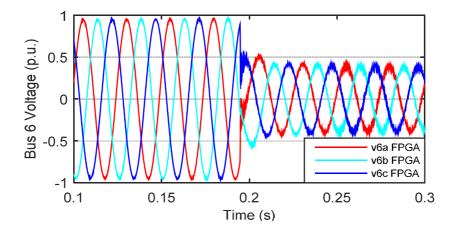

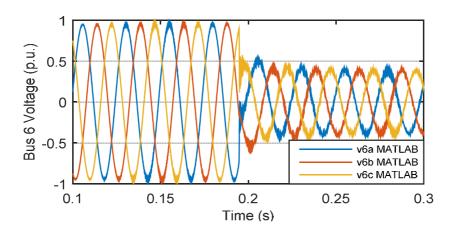

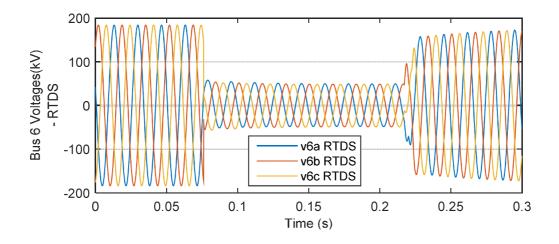

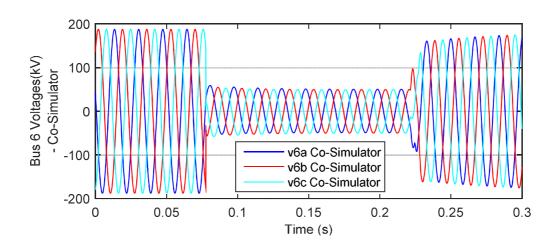

| FIGURE 3-10 THREE-PHASE VOLTAGE AT BUS 6                                   | 115 |

|----------------------------------------------------------------------------|-----|

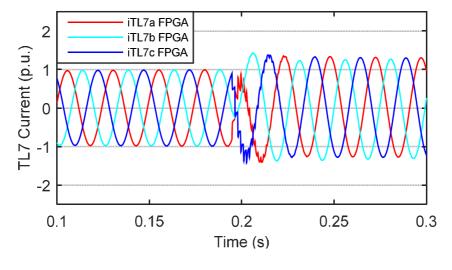

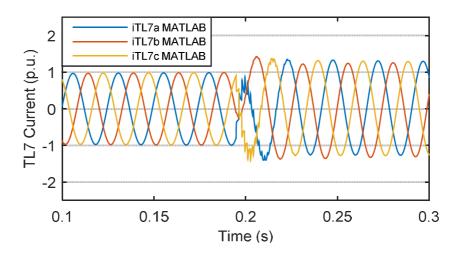

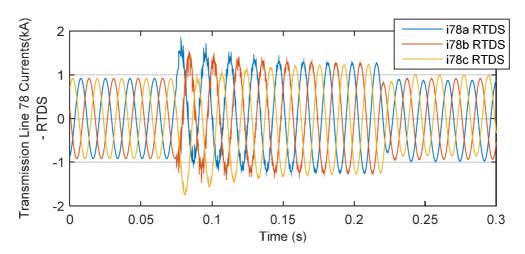

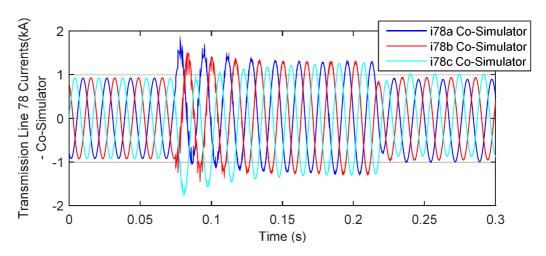

| FIGURE 3-11. THREE-PHASE LINE CURRENT BETWEEN BUS 7 AND BUS 8 (TL78A)      | 116 |

| FIGURE 3-12 CURRENT AT FAULT LOCATION                                      | 117 |

| FIGURE 3-13 SINGLE-LINE DIAGRAM OF CASE STUDY 2                            | 118 |

| FIGURE 3-14 SIMULATION RESULTS FOR CASE 2                                  | 120 |

| FIGURE 4-1 ARCHITECTURE OF THE PROPOSED FPGA-RTDS CO-SIMULATOR             | 123 |

| FIGURE 4-2 INTERFACE BETWEEN FPGA AND RTDS                                 | 126 |

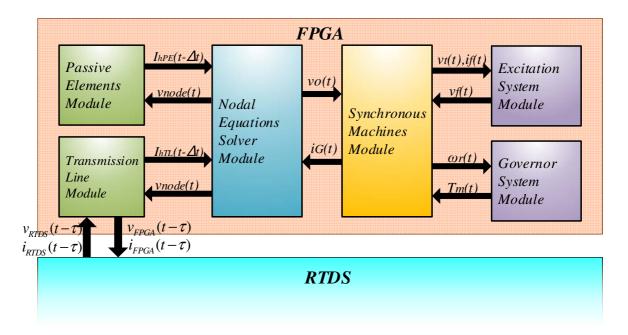

| FIGURE 4-3 HARDWARE MODULES FOR FPGA IMPLEMENTATION                        | 130 |

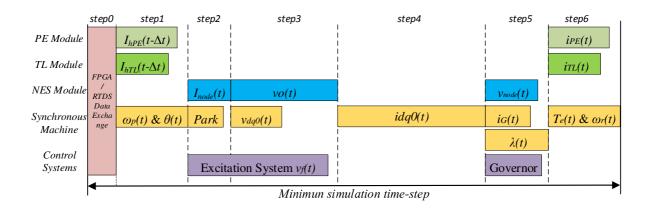

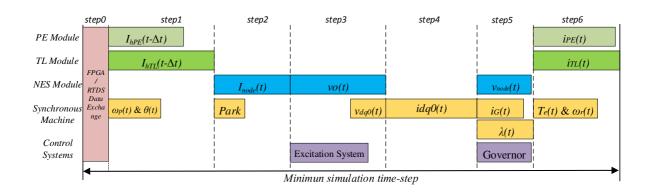

| FIGURE 4-4 COMPUTATION SCHEME OF THE CO-SIMULATOR                          | 131 |

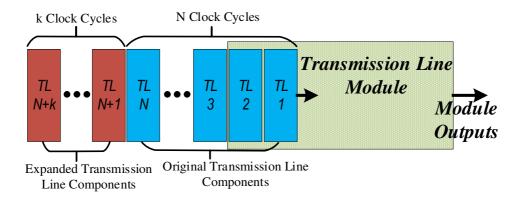

| FIGURE 4-5 NETWORK EXPANSION OF TRANSMISSION LINE COMPONENTS               | 133 |

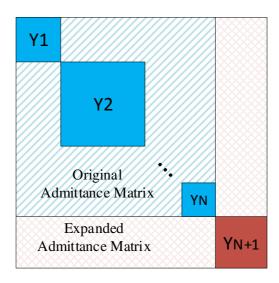

| FIGURE 4-6 NETWORK EXPANSION OF ADMITTANCE MATRIX                          | 133 |

| FIGURE 4-7 SIMULATIONS OF TWO-AREA FOUR-MACHINE SYSTEM                     | 136 |

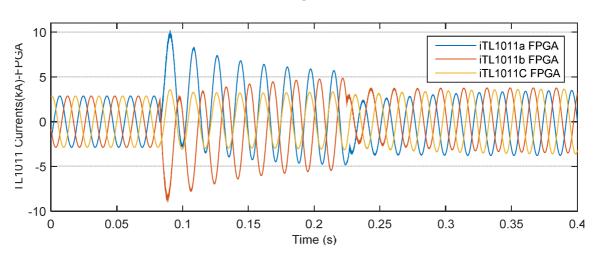

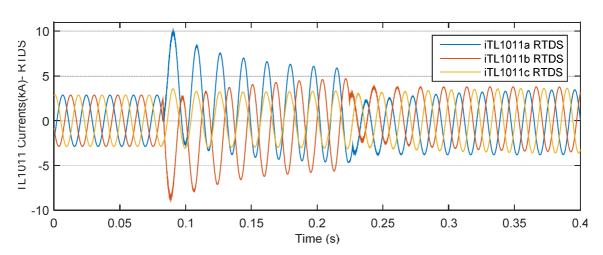

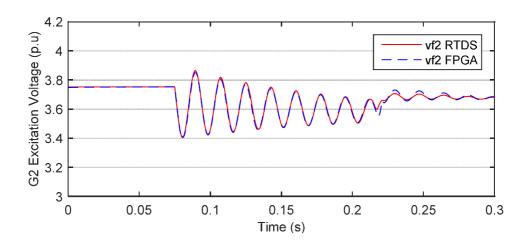

| FIGURE 4-8 SIMULATION RESULTS FOR CASE 1                                   | 139 |

| FIGURE 4-9 SIMULATIONS OF TWO-AREA FOUR-MACHINE SYSTEM FOR CASE 2          | 140 |

| FIGURE 4-10 SIMULATION RESULTS FOR CASE 2                                  | 144 |

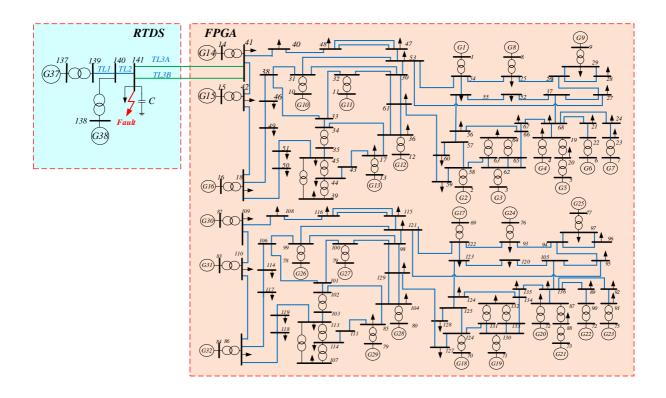

| FIGURE 4-11 SIMULATION OF A 141-BUS SYSTEM USING THE PROPOSED CO-SIMULATOR | 145 |

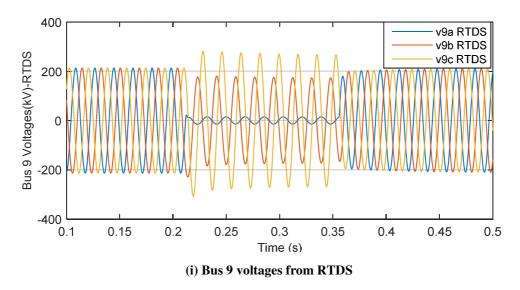

| FIGURE 4-12 CASE 3 SIMULATION RESULTS FROM RTDS                            | 146 |

| FIGURE 4-13 CASE 3 SIMULATION RESULTS FROM FPGA                            | 147 |

| FIGURE 4-14 BREAKDOWN OF MINIMUM SIMULATION TIME-STEP OF CASE 1            | 149 |

| FIGURE 5-1 DIRECT COMMUNICATION BETWEEN FPGAS                              | 155 |

| FIGURE 5-2 INDIRECT COMMUNICATION THROUGH RTDS                             | 156 |

| FIGURE 5-3 SIMULATION CAPABILITY OF THE MULTI-FPGA BASED CO-SIMULATOR      | 157 |

| FIGURE 5-4 SINGLE-LINE DIAGRAM OF SYSTEM CONFIGURATION                     | 160 |

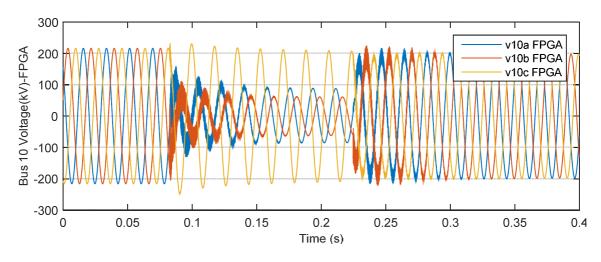

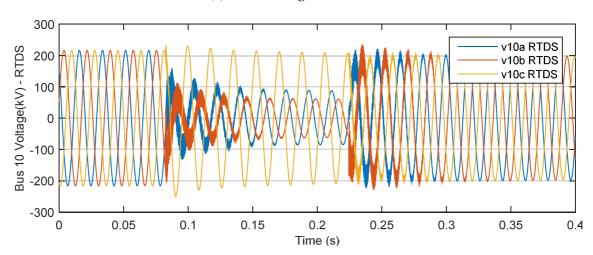

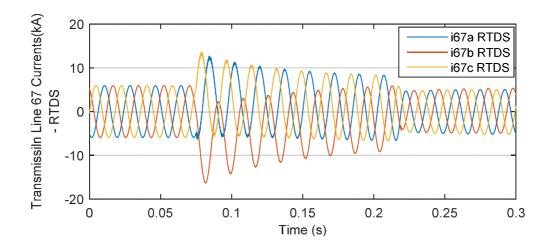

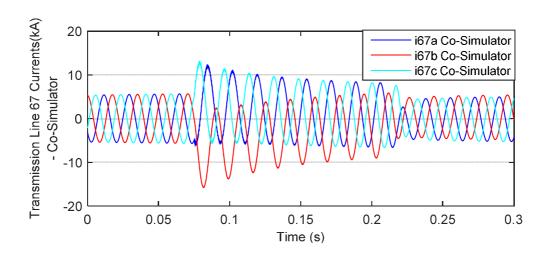

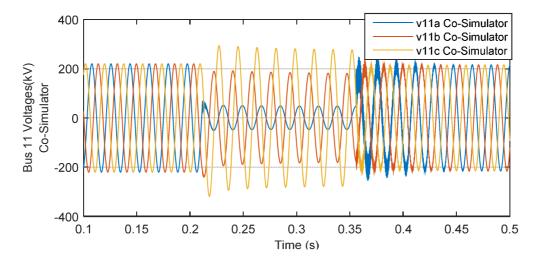

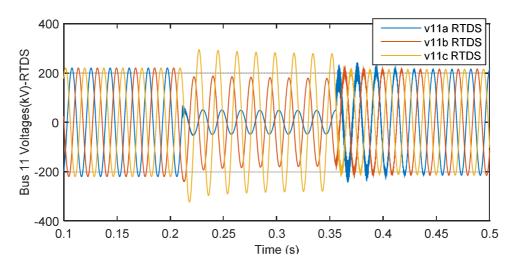

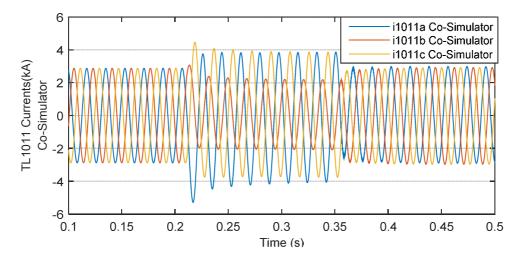

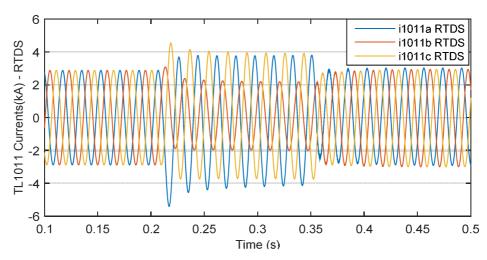

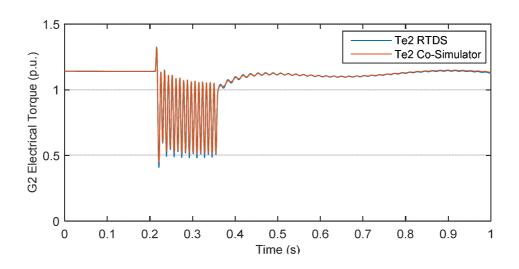

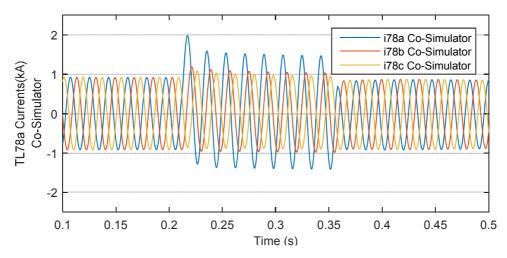

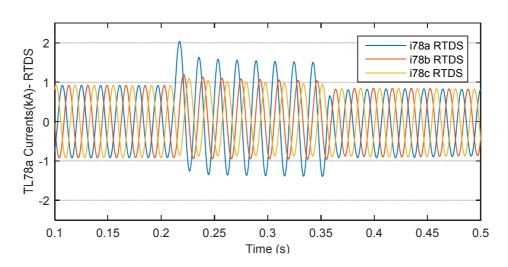

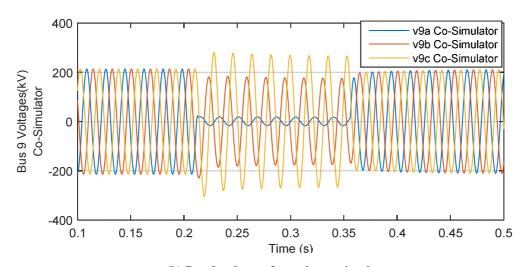

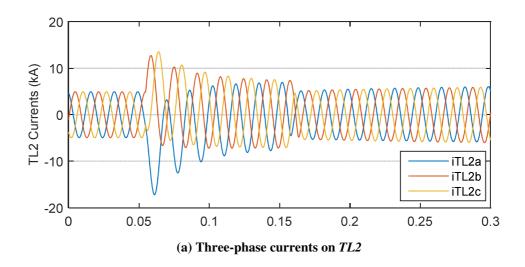

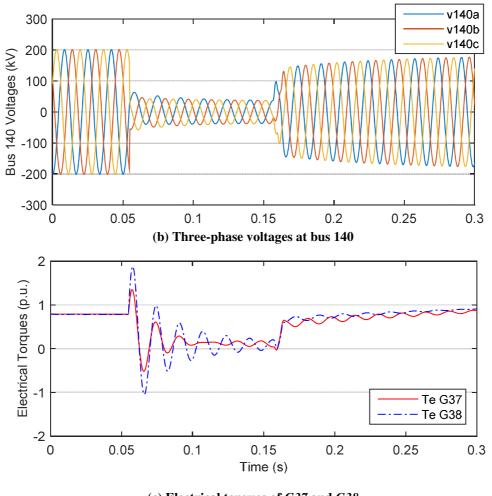

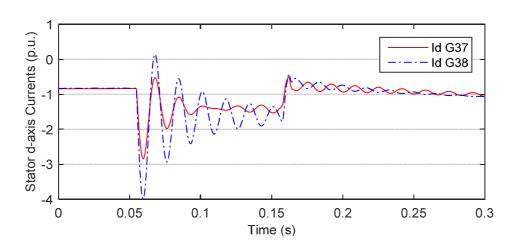

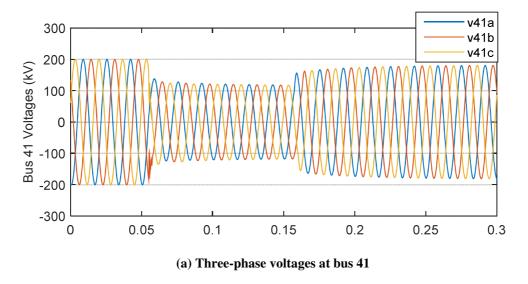

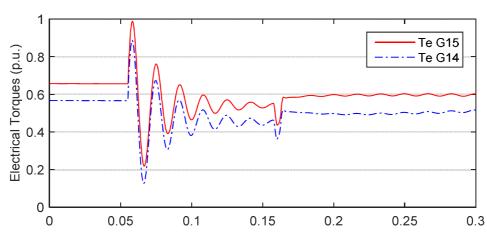

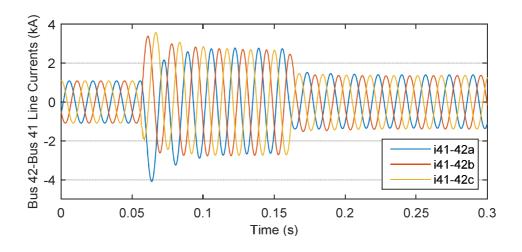

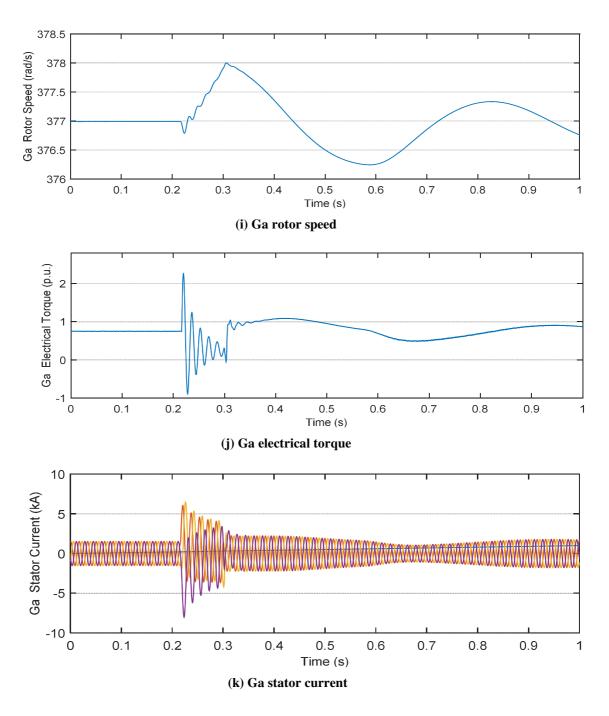

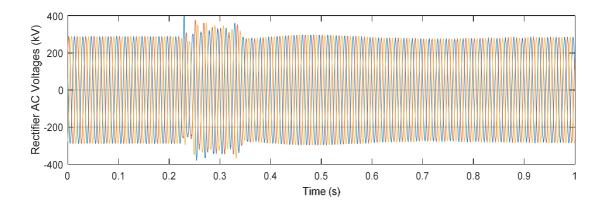

| FIGURE 5-5 SIMULATION RESULTS WITH 100MS FAULT AT RECTIFIER SIDE           | 165 |

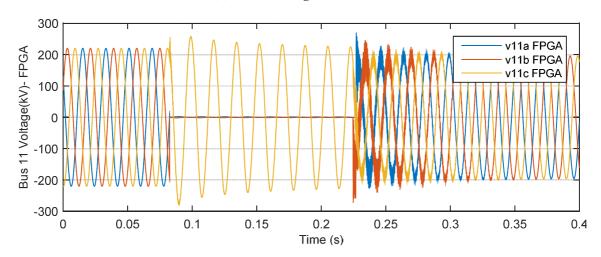

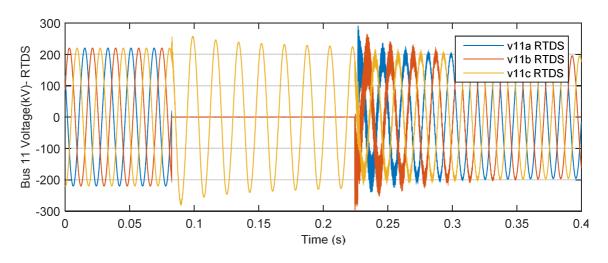

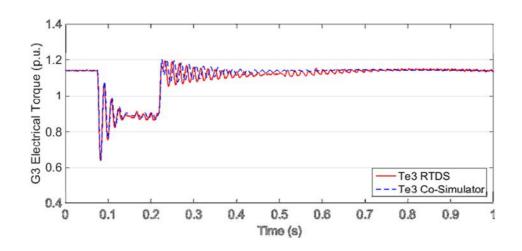

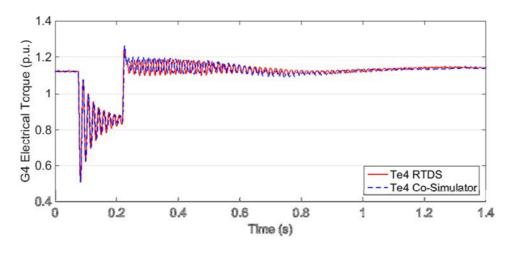

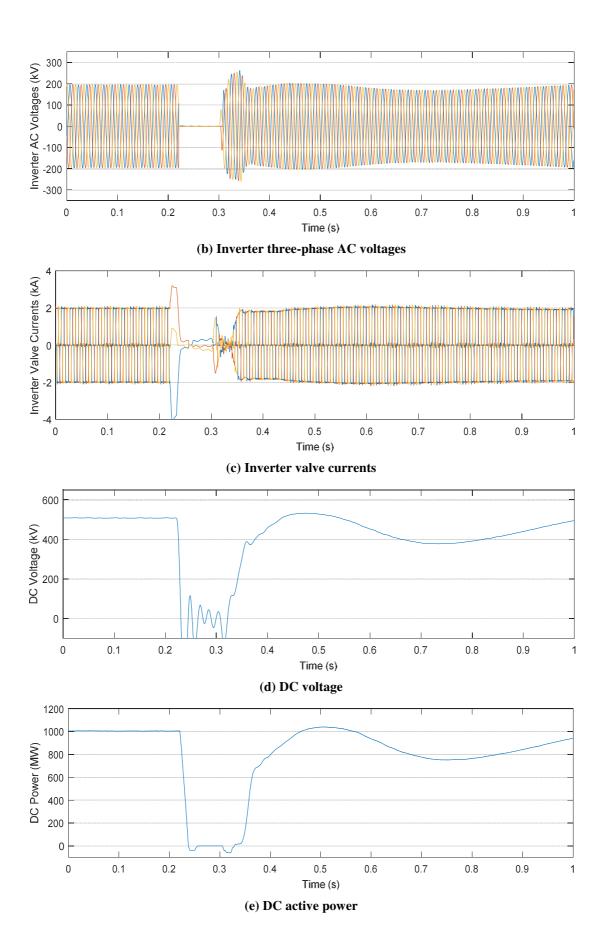

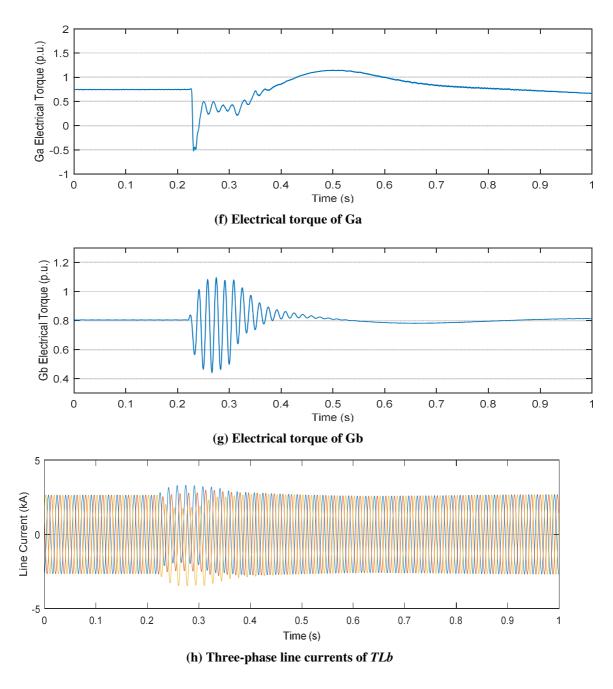

| FIGURE 5-6 SIMULATION RESULTS WITH 100MS FAULT AT INVERTER SIDE            | 168 |

| FIGURE 5-7 BREAKDOWN OF MINIMUM SIMULATION TIME-STEP                       | 170 |

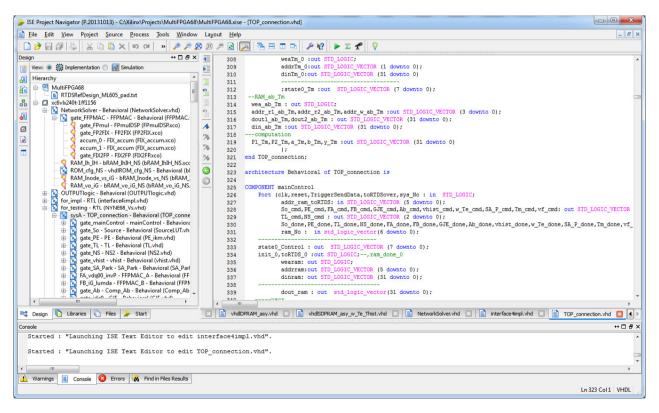

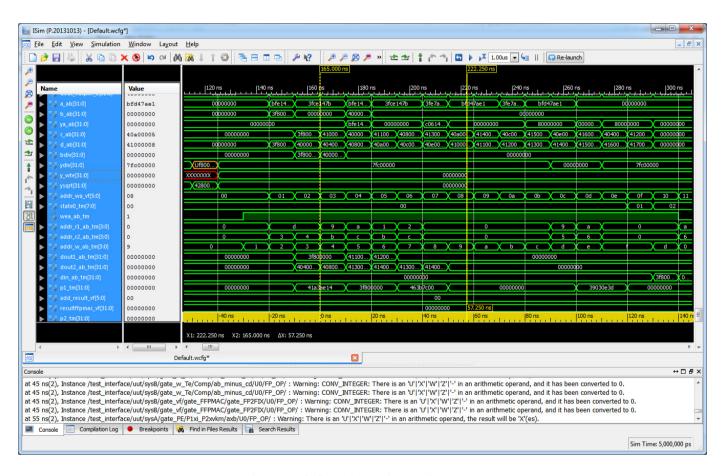

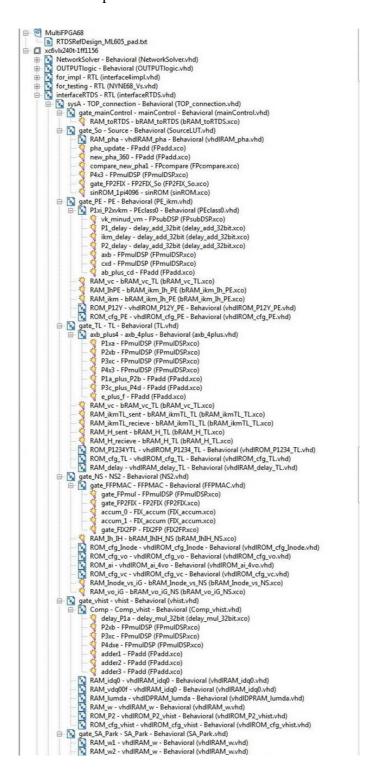

| FIGURE D. 1 ISE CODING ENVIRONMENT                                         | 199 |

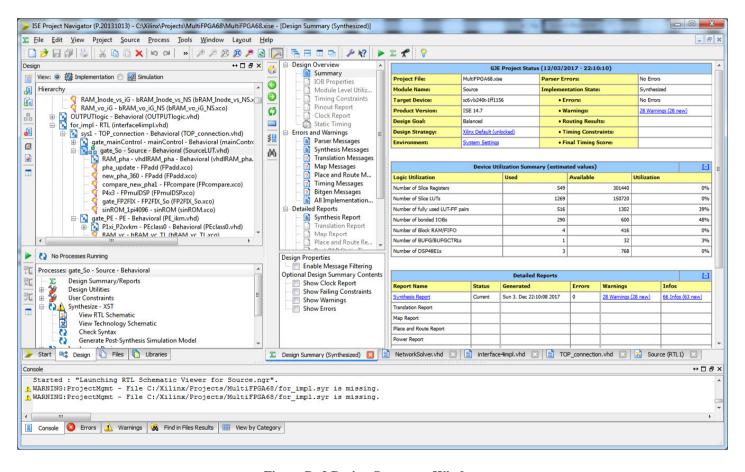

| FIGURE D. 2 DESIGN SUMMARY WINDOW.       | 200 |

|------------------------------------------|-----|

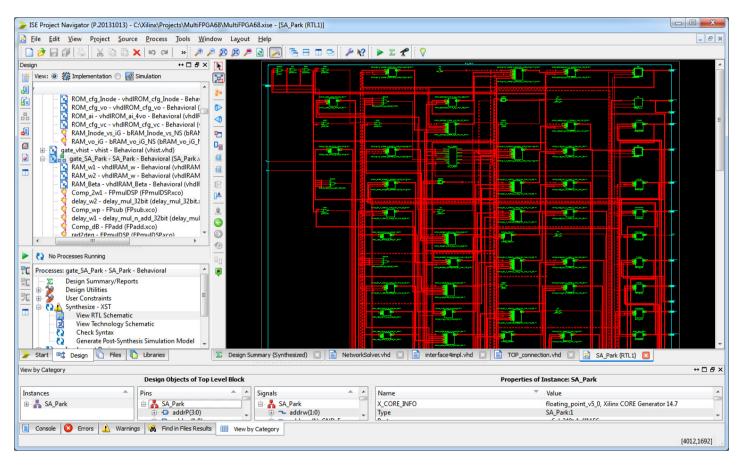

| FIGURE D. 3 RTL SCHEMATIC VIEW           | 201 |

| FIGURE D. 4 ISIM SIMULATION ENVIRONMENT. | 203 |

# LIST OF TABLES

| TABLE 1.1 EXISTING AND FUTURE INTERCONNECTOR PROJECTS [28]         | 3   |

|--------------------------------------------------------------------|-----|

| TABLE 1.2 FEATURE SUMMARY OF XILINX VIRTEX-6 XC6VLX240T FPGA [115] | 16  |

| TABLE 2.1 DEFINITIONS OF VARIABLES FOR SYNCHRONOUS MACHINE         | 28  |

| TABLE 2.2 PARAMETERS FOR GOVERNOR/TURBINE SYSTEM                   | 80  |

| TABLE 4.1 FPGA RESOURCE UTILIZATION                                | 148 |

| TABLE A.1 SYNCHRONOUS MACHINE PARAMETERS                           | 190 |

| TABLE C.1 TRANSMISSION LINE PARAMETERS                             | 194 |

| Table C.2 Load Parameters                                          | 196 |

| Tarif C 3 Generator Parameters                                     | 198 |

## LIST OF ABBREVIATIONS

**AC** Alternating Current

**ASIC** Application Specific Integrated Circuit

**CLB** Configurable Logic Blocks

**CPLD** Complex Programmable Logic Devices

**CPU** Central Processing Unit

**D/A** Digital To Analog

**DC** Direct Current

**DSP** Digital Signal Processing

**EMT** Electromagnetic Transient

**EMTP** Electromagnetic Transient Programme

**FACTS** Flexible Ac Transmission Systems

**FFT** Fast Fourier Transform

**FPGA** Field-Programmable Gate Array

**FSM** Finite State Machine

GTDI Gigabit Transceiver Digital Input Card

GTDO Gigabit Transceiver Digital Output Card

HIL Hardware-in-the-Loop

**HVDC** High Voltage Direct Current

I/O Input/Output

**ISP** In-System Programming

LCC Line-Commutated Converter

**LUT** Look-Up Tables

MMC Modular Multilevel Converter

MMCM Mixed-Mode Clock Managers

MSB Most Significant Bit

**OTP** One Time Programmable

**PLD** Programmable Logic Devices

PLL Phase Locked Loop

**PV** Photovoltaics

**PWM** Pulse Width Modulation

**RAM** Random Access Memory

**RISC** Reduced Instruction Set Computer

**ROM** Read-Only Memory

**RTDS** Real-Time Digital Simulator

**RTL** Register Transfer Level

**RTS** Real-Time Simulator

**SRAM** Static Random Access Memory

**STATCOM** Static Compensators

TCSCs Thyristor-Controlled Series Compensations

**TNA** Transient Network Analyser

**TS** Transient Stability

**UBC** University of British Columbia

**USB** Universal Serial Bus

VCO Voltage-Controlled Oscillator

# Chapter 1

## INTRODUCTION

## 1.1 Research Background

#### 1.1.1 Evolution of Modern Electrical Power Systems

Modern electrical power systems are undergoing dramatic changes in a number of ways, including:

- Increasing level of integration from renewable energy sources and Electric Vehicles

(EV) [3-7].

- Increasing level of interconnections between regional/national electrical power systems [8-16].

- Increasing applications of power electronic-based devices in existing networks [17-21].

Renewable sources such as wind, solar, hydro and EV are playing an increasingly important role in electrical power systems to provide low-carbon electricity. The speed of increase of renewable integration is further driven by government targets and national legislations. For example in the U.K., the target is to provide 15% of total energy demand from renewables by 2020, and 30% of electricity from renewables [22]. Scottish government's 2020 renewable target states that the equivalent of 100% of Scotland's electricity demand should be met by renewables [22]. Currently UK already has the largest offshore wind farms in the world with

further projects down the pipeline [23]. PV deployment in UK has reached more than 10GW, and is becoming the most popular renewable energy source among British electricity consumers, both in the domestic and commercial sectors [24]. More than 100,000 plug-in EVs have been registered in the UK up until March 2017 [25]. Figure 1-1 shows the installed capacity of different renewable sources in UK. Similar trend can also be found in other parts of the world, for example in China about 13 large hydro power centres are planned with a total generating capacity of about 215 GW [26].

# 12000 10000 8000 4000 2000 2012 2013 2014 2015 2016

**Installed Capacity of Renewable Sources (MW)**

#### Figure 1-1 Installed capacity of renewable sources in UK [27]

The number of interconnections between power systems also grows significantly in recent years. Interconnectors are the physical links which allow the transfer of electricity across borders. It can improve the diversity and security of energy supplies, facilitate competition in wider electricity market and help the transition to a low carbon future by integrating renewable sources [28]. For example, UK currently has 4GW of interconnector capacity with France, Netherlands, Northern Ireland and the Republic of Ireland [28], with 7 more interconnectors to be built in the next five years linking the UK with other European countries [28]. A list of these projects is shown in Table 1.1. Furthermore, under the initiative

of global power and energy internet, interconnectors have been built or proposed world-wide in middle-east [29], Asia [11], Europe [13], North America [30] and South America [31, 32].

Table 1.1 Existing and Future Interconnector Projects [28]

| Project   | Connecting  | Consoity | Delivery date/Estimated |

|-----------|-------------|----------|-------------------------|

| Name      | Country     | Capacity | Delivery Date           |

| IFA       | France      | 2000MW   | 1986                    |

| Moyle     | Ireland     | 500MW    | 2002                    |

| BritNed   | Netherlands | 1000MW   | 2011                    |

| EWIC      | Ireland     | 500MW    | 2012                    |

| ElecLink  | France      | 1000MW   | 2019                    |

| NEMO      | Belgium     | 1000MW   | 2019                    |

| NSN       | Norway      | 1400MW   | 2020                    |

| FAB Link  | France      | 1400MW   | 2022                    |

| IFA2      | France      | 1000MW   | 2020                    |

| Viking    | Denmark     | 1000MW   | 2022                    |

| Greenlink | Ireland     | 500MW    | 2021                    |

Due to the intermittent nature of renewables compared with traditional power plant, they bring additional risks to the operation, control and protection of power systems. To solve these problems, power electronic-based devices are installed to improve the stability and controllability of power systems. For example, in the UK two units of Thyristor-Controlled Series Compensations (TCSCs) have been installed to boost the boundary transfer capability between Scotland and England [33], and three units of Static Compensators (STATCOMs) are to be installed in the National Grid Electricity Transmission Network to improve the transient voltage stability [34].

All the changes mentioned above directly result in a significant increase in the size and complexity of power systems, which makes the power system planning, operation and optimization ever-more difficult. For example, for simulation studies with interconnectors,

detailed modelling of power systems at both ends of the interconnector is required for accurate representation of system dynamics and control/harmonic interactions. At the same time, the simulations of these interconnectors themselves are normally computationally intensive because of the large number and high-frequency switching of the power electronics involved.

#### 1.1.2 The Need for Accurate Simulation Technology

The increasing complexity of power system drives the need for more accurate simulation technologies. For example, the switching dynamics from power electronic based devices can potentially lead to more serious transient overvoltage/overcurrent problems and harmonic problems. Also it poses great challenges to the protection and control of power systems as the voltage and current behaviour of the system are affected by the operations of power electronic devices. To accurately simulate these phenomena to facilitate the design and planning of protection/control, the power system component models should be able to represent high frequency dynamics of up to MHz. This means that the required simulation time-step is in the order of microsecond according to Nyquist criteria [35]. Normally, a simulation time-step of 1  $\mu$ s – 50  $\mu$ s is required [1] for the study of the above phenomenon.

Traditionally, electromechanical transient simulation programmes (also known as transient stability (TS) programmes) have been utilized to analyse the transient stability of power systems [36]. Typical TS programmes solve thousands of differential-algebraic equations for multi-machine power systems assuming single-phase fundamental frequency behaviour [37]. There are several commercial TS programmes available in the market such as the PSS/E from PTI [38], SIMPOW from ABB [39], NETOMAC from Siemens [40] and PowerFactory [41]. A simulation time-step of around 10ms is normally adopted by TS programmes, and with this

simulation time-step, high frequency dynamics as mentioned above cannot be accurately simulated. As a result, the use of TS programme is limited when higher simulation accuracy/smaller simulation time-step are required.

Electromagnetic transient programme (EMTP) was specifically developed with sufficient accuracy for the analysis of above aspects [42]. Unlike electromechanical transient, Electromagnetic transient (EMT) considers the interaction between magnetic fields of inductance and the electric fields of capacitances in the system [43]. The study of these interactions requires accurate simulation of the network elements such as synchronous generators, transmission lines, transformers, and power converters. The models should cover a wide range of frequencies from DC up to MHz, which indicates a required simulation timestep as small as a few microseconds [1, 43]. For example, to investigate 10 KHz voltage disturbance, a time-step of smaller than 50 μs is required according to Nyquist criterion [35].

Typically the following modelling aspects are considered in the EMTP:

- Non-linearity in electrical components;

- Electro-magnetic couplings;

- Travelling wave effect of transmission lines;

- Unbalance of three-phase systems and frequency dependent of transmission line parameters.

Normally the power system components are represented as differential equations using instantaneous values in EMTP rather than phasor values. Also single-phase representation is replaced by multi-phase representation [43]. Differential equations are solved using numerical method with simulation time-steps of around 50µs. With such small simulation time-step, the size of power system that can be simulated by EMTP is rather limited. The

original commercial EMTP is developed by Dommel [42], and a number of developments have been made ever since: PSCAD-EMTDC [44] developed by Manitoba HVDC Research Centre; NETOMAC from Siemens and a number of other EMT-based simulators developed in the past two decades which will be discussed in detail in the next section.

#### 1.1.3 The Need for the Efficient Simulation of Larger Systems

The continuous increase of the number of interconnector and size of power system inevitably leads to the need for the efficient simulation of larger power systems. Although sufficient simulation accuracy can be provided by EMTP, the size of power system that can be efficiently simulated by EMTP is usually limited (e.g., IEEE 39-bus system can take up a whole rack of RTDS with detailed EMT modelling of synchronous machines and transmission lines). For example with most of the commonly used EMTP-based simulators, e.g. PSCAD, it is difficult to study the phenomenon of harmonic/control interactions of large scale hybrid AC/DC transmission network [37]. This is because smaller simulation time-step (in the order of few microseconds) is needed for the simulation of converter systems for DC transmission. As a result it takes up a significant amount of the computation resources and limits the size of AC system (to tens of buses) that can be simulated given a fixed amount of hardware resources. This type of study requires the detailed representation of synchronous machines and power electronic-based converters, and the size of network can be easily up to hundreds, if not thousands of nodes. Due to the high requirement of both accuracy and the size of the system, the use of EMTP becomes technically difficult and economically prohibitive in simulation of large power systems.

For example for the simulation of Modular Multilevel Converter (MMC) based HVDC system, a simulation time-step of less than 5µs is required for accurate results [45]. A normal

MMC converter has several thousand of power electronic switches, and the simulation of such a system using EMTP becomes very time and resource-consuming. Even if the MMC HVDC can be simulated, the connecting AC systems that can be modelled are normally limited to a maximum of tens of nodes using typical EMT programmes. Network equivalents can be adopted to reduce the computational burden, at the expense of simulation accuracy. From the point of view of system operators, it would certainly be beneficial for planning and analysis purposes if a larger part of the power network can be simulated under EMT type of simulation programmes.

#### 1.1.4 Opportunities and Challenges

From the above analysis, it can be clearly seen that the simulation of modern electrical power system has the following two seemingly conflicting objectives:

- To achieve accurate simulation of power electronic devices and nonlinear power system dynamics.

- 2. To achieve efficient simulation of larger-scale power systems;

Significant amount of efforts have been made to achieve the above two objectives. The main approach is to simplify the part of power system that is remote to the system of interest [46-51]. The way of simplification varies from each other and the resulting simulation accuracy and speed are also different. Nevertheless, more powerful simulation methodologies are desired to achieve both accuracy and simulation speed at the same time.

#### 1.2 Literature Review

Previous research works can be classified into two main categories: one is focusing on improving the simulation capability for large power systems and the other is focusing on

improving the simulation accuracy. Literatures of these two categories are discussed first and then the FPGA technology and its application to power system simulation are reviewed.

#### 1.2.1 Improvement of Simulation Capability for Large Power Systems

#### 1.2.1.1 Network Equivalent & Network Partitioning

One of the earliest attempt to achieve efficient simulation is made in [48]. In the paper, EMT models of power system components were adopted for part of the network. Passive equivalent circuits were used to simplify the rest of the network. The passive equivalent circuits were used to represent the dynamics of the original power system. The simplification to RLC components inevitably causes the loss of important power system dynamics from synchronous machines and transmission lines. Another method was to partition the original network into smaller subsystems. In reference [52], the method of network partitioning was proposed utilizing the natural delay of travelling-wave transmission lines. The simulations of subsystems which are interconnected by relatively long transmissions lines are effectively decoupled with each other. Another method of network partitioning was proposed in [53]. The proposed method divided the original system using the idea of "boundary busses". One of the benefits of this method was that it did not relay on the transmission lines. A different approach which based on the idea of multi-rate simulation was proposed in [54]. The complete system was modelled using EMT component models and solved with different time-steps according to the speed of system dynamics. The part of the system with slow dynamics was simulated using larger time-steps, while the part of the system with faster dynamics was simulated using smaller time-steps. However, the drawback for the above methods is that the size of the system that can be simulated is limited [37].

#### 1.2.1.2 Hybrid EMT/Transient Stability (TS) Simulation

In the last decade, the idea of hybrid simulation method was proposed [47, 51, 55-64] to achieve efficient simulation of relatively large power systems without significantly sacrificing the simulation accuracy. The main objective of hybrid simulation is to split the original network into two parts and the part that requires less simulation accuracy is simulated using TS programmes, while the other part is simulated using detailed EMT programmes. The EMT part usually includes HVDC links, Flexible AC Transmission (FACTS) devices or parts of the network that is sensitive to disturbances. The TS part tries to include extensive portions of the network, and detailed component models are not implemented.

The accuracy of hybrid simulation is largely determined by the method of network equivalent for both simulators. Reference [65] suggested to represent the TS part of the system by a Norton equivalent with fundamental frequency current source for the simulation of EMT part of the network. The drawback of this method is that the topological changes during simulation (e.g., faults) at TS part of the system can only be simulated by changing the impedance value of the Norton equivalent circuit [62]. More accurate approaches are to use the frequency dependent network equivalent [58, 61, 63]. The method of Vector Fitting was proposed in [66] to calculate the frequency dependent network equivalent. In reference [47], a method of multiport Norton equivalent with couplings was proposed for the simulation case with multiple interface buses. However these methods considerably increase the computational burden of EMT simulators.

Another aspect in hybrid simulation is the choice of interface variables and the conversion of data. The interface variables that have been chosen must be able to determine the power flow

into the interface buses [61]. Data converter blocks are required to connect two types of programmes. Conversion from phasors to instantaneous variables is required for EMT programme, and conversion from instantaneous variables to phasors is required for TS programme. Signal generators with the inputs of amplitude, phase and frequency information are normally used to provide interface data to EMT simulators [67]. Digital processing techniques such as curve fitting, Fast Fourier Transform (FFT) are utilized to provide interface data to TS simulators [47, 61, 67]. However the problems related to the speed of FFT method and the effectiveness in handling DC offset with curve fitting technique need to be solved [51].

From the above analysis, it can be seen that the actual implementation of hybrid simulation is difficult. It is understandable because two parts of the systems to be simulated are based on different mathematical models under different assumptions, and are simulated with different time-steps. Due to the nonlinear nature of power system, the interface between them will inevitably be difficult to realize. At the same time the potential interface errors cannot be eliminated.

Therefore the idea of utilizing modern Field Programmable Logic Arrays (FPGAs) to simulate large scale power systems with detailed EMT models becomes attractive. A review of the FPGA technology and associated applications are shown in the next sections.

#### 1.2.2 Improvement of Simulation Accuracy

#### 1.2.2.1 Real-Time Simulation

The idea of real-time simulator (RTS) was first developed in the 1950s to achieve high simulation accuracy for power system simulation. The main advantages of real-time simulation are its fast simulation speed (real time) and its ability to carry out HIL testing for

the HIL test setup is less expensive than the physical setup. In addition, the testing using real-time simulation can replace risky or expensive test that uses physical high voltage/high current equipment [1]. The earliest RTS is called Transient Network Analyser (TNA) [68-70]. The working principle of TNA is to establish the physical model of power system but with lower levels of voltage and current. Therefore the physical characteristics in the TNA are effectively the same as those in real power systems, and the simulation using TNA is inherently real-time. The size of the network that can be simulated is largely dependent on the available equipment and the size of the lab, so the simulation of a relatively large power system is economically prohibitive. Furthermore, the setting up of new simulation cases or the modification to existing simulation cases are labour-intensive and require highly skilled personnel [71]. Due to these reasons, the flexibility and expandability of TNA is rather limited.

With the fast development of microprocessor and integrated circuit, digital RTS started to emerge based on Central Processing Unit (CPU), Digital Signal Processing (DSP) or Reduced Instruction Set Computer (RISC) [71]. Fully digital RTS have higher flexibility and lower cost compared with traditional TNA, and has been used till now. Significant advances were made since 1980s. Reference [72] proposed a real-time digital simulator for the testing of protection relays. The proposed simulator was based on EMTP using RISC and DSP as fundamental hardware layer. The IBM RISC 6000 work station performed the simulation of the network, while the DSP performed the simulation of transformers. Reference [73] proposed the use of dual DSP for real-time simulation. In the proposed method, each DSP was used to simulate one terminal of a transmission line. A real-time simulation framework fully based on IBM RISC 6000 work station was proposed in [74]. It achieved a simulation

time-step of 38µs to 107µs for network with 18 to 30 nodes. University of British Columbia (UBC) developed their real-time digital simulator (OVNI) based on Pentium II workstation [75]. It can achieve the real-time simulation of HVDC system with 24 switches at a simulation time-step of 81µs. However, all the above mentioned methods either used custom-made DSPs or commercial supercomputers. The high cost of the equipment and the cost associated with the inter-computer communication limited the further applications of such methodologies.

With further development of the processor technology, the PC-cluster based real-time simulation technique was adopted to cater for larger sized power networks with reduced cost. Reference [76], on the basis of reference [75], developed a PC cluster version of OVNI. The proposed method utilized 5 PCs to form the PC cluster. The speed of simulation and simulation time-step were considerably improved compared with the original OVNI. A demonstration of simulating 234 node transmission network in real-time is shown in the paper. University of Alberta developed another PC cluster based real-time digital simulator, targeting the electrical drive systems with power electronic devices [77]. The simulation time-step of 10µs was achieved. The PC cluster based method was further driven by the advent of low-cost, high-performance readily available multi-core processors [78]. It potentially reduced the need to cluster multiple PCs to conduct complex parallel simulation, thereby reducing dependence on the inter-computer communication technology.

The latest trend in real-time simulation consists of exporting simulation models to FPGA [79-92]. However, most of the works to date are only focusing on the simulation of power electronic converters or small sized power systems. Very few applications have been found to implement the EMTP for large-scale power systems using FPGA [93-95]. One of the important advantages of using FPGA is that computational burden (simulation time-step) is

not linearly related to the size of the system to be simulated, which is due to its paralleled architecture and pipelined way of computations. As a result, potentially very large systems using EMT models can be simulated in real-time.

In parallel with the continuous research and development in real-time simulation technologies, a number of real-time digital simulators have been made commercially available:

- The Real-Time Digital Simulator (RTDS), from RTDS Technologies Inc. The

company demonstrated the first commercial RTDS in 1991 using DSPs [96]. Modern

RTDS uses PowerPC RISC processors that are implemented in cards (PB5) [2].

Several cards are used form a rack for the simulation a complete power system. With

larger networks, multiple racks can be utilized together with fast interface cards.

- 2. eMEGAsim, from OPAL-RT Technologies Inc. [97]. The hardware includes multicore CPU, FPGA, and commercial of-the-shelf motherboard. The models are constructed in MATLAB/SIMULINK, and are simulated in target PCs.

- 3. HYPERSIM from Hydro-Quebec [98, 99]. It is a supercomputer-based simulator, which is no longer commercially available. Recent development of the simulator uses PC clusters, supercomputers and 32 core Intel computers to suit multi-purpose simulations.

- dSPACE [100]. It is purely CPU based with the modelled constructed in SIMULINK.

It is mainly used for real-time control and rapid prototyping for automotive engineering and industrial control.

- 5. VTB [101-103]. It is based on DSP cluster or multi-core CPU/FPGA, and is mainly used for power system simulations.

- 6. xPC Target [104]. It is based on CPU and FPGA and is mainly used for rapid prototyping, real-time testing of applications and HIL simulation.

- rtX from ADI [105]. Simulations are carried out in CPU and main purpose is for power system simulation for avionics and maritime industries, aircraft simulation and shipboard simulation.

- 8. Typhoon RTDs [106, 107]. Simulations are carried out in FPGA with models constructed in Typhoon schematic editor. It is mainly used for the testing of power electronics controller.

- 9. NETOMAC from Siemens [40, 108]. It is a PC based digital simulator which is able to carry out transient stability, electromagnetic transient and real-time simulations.

Among all the available real-time digital simulators, only a few of them are capable of simulating large systems [2]. The main problem is that these simulators are expensive, both in terms of initial investment and maintenance fees. With the growing size and complexity of power system, significant further investments are likely to be required.

#### 1.2.3 FPGA Technology

Typical digital systems can be classified into full-custom integrated circuit and semi-custom integrated circuit [109]. Full-custom integrated circuit can be further categorized into general-purpose integrated circuit. The commonly used CPU, RISC, DSP all belong to general-purpose integrated circuit and Application Specific Integrated Circuit (ASIC) belongs to the special-purpose integrated circuit [110].

General-purpose integrated circuit can be fully compiled and controlled by software, hence achieves the decoupling between software and hardware. This feature makes the general-purpose integrated circuit very flexible but with lower computational efficiency. On the other hand, ASIC is the purposely built integrated circuit designed to meet specific requirements from customers. In this way, the circuit configuration, layout and wiring can be optimally

designed to achieve the best utilization of the circuit. The drawbacks of ASIC are that it is less flexible with high cost, and cannot be reconfigured.

Semi-custom integrated circuit includes various kinds of reconfiguration devices such as FPGA and Complex Programmable Logic Devices (CPLD). This kind of reconfigurable device lies between the general-purpose integrated circuit and special-purpose integrated circuit. The manufacturer provides basic layout of logic gates and reconfigurable logic blocks, and the customer is able to design the connections between logic gates using professional software. In this way, the integrated circuit is effectively configured by the customers according to their need. It can be seen that this type of devices combines the merits of both general-purpose integrated circuit and special-purpose integrated circuit, featuring low cost, high configurability and short development time. Comparing FPGA with CPLD, FPGA has better configurability, higher integration density in terms of logic gates and better computational ability.

Currently the FPGA in the market can be classified into three different categories: 1) Static Random Access Memory (SRAM)-based [111, 112]; 2) fuse-based [111, 112] and 3) flash-based [113]. Among them, the SRAM-based FPGA is the most widely used because of its fast computational speed and high reconfiguration ability [114]. Fuse-based FPGA only has One Time Programmable (OTP) ability. Flash-based FPGA is relatively new and does not have wide applications. In terms of the manufactures, Altera, Xilinx, Lattice and Actel are some of the largest FPGA manufactures in the world.

• Altera<sup>®</sup> is one of the most famous FPGA manufactures with fast developments after 1990s. It has now become one of the largest providers of programmable logic devices

- (PLD). FPGA from Altera<sup>®</sup> has high performance, high integration density of logic gates and relatively low cost.

- Xilinx<sup>®</sup> is the inventor of FPGA and it has been manufacturing PLDs over several decades. The FPGA was first developed in 1985 by Xilinx and several generations of FPGAs have been developed with much improved performances.

- Lattice<sup>®</sup> is the inventor of In-System Programming (ISP). It enters into the FPGA markets after 2004 and is now the world's third largest provider for FPGA.

- Actel<sup>®</sup> is an American FPGA manufacturer originally focusing on products for military defence and aerospace engineering. The early generations of FPGAs from Actel<sup>®</sup> are mostly fuse-based. Recently it starts to develop commercially available flash-based FPGA.

Table 1.2 Feature Summary of Xilinx Virtex-6 XC6VLX240T FPGA [115]

| Logic Cells                      |                                  | 241,152 |

|----------------------------------|----------------------------------|---------|

| Configurable                     | Configurable Slices Logic Blocks |         |

| (CLBs)                           | Max Distributed RAM (Kb)         | 3,650   |

| DSP48E1 Slices                   |                                  | 768     |

|                                  | 18 Kb                            | 832     |

| Block RAM<br>Blocks              | 36 Kb                            | 416     |

| Diocks                           | Max (Kb)                         | 14,976  |

| MMCMs                            |                                  | 12      |

| Interface Blocks for PCI Express |                                  | 2       |

| Ethernet MACs                    |                                  | 4       |

| Maximum Transceivers GTX         |                                  | 24      |

| Total I/O Banks                  |                                  | 18      |

| Max User I/O                     |                                  | 720     |

As the Xilinx<sup>®</sup> Virtex-6 XC6VLX240T FPGA is used for the EMTP implementation in this thesis, its basic configuration and functions are briefly illustrated in the following sections.

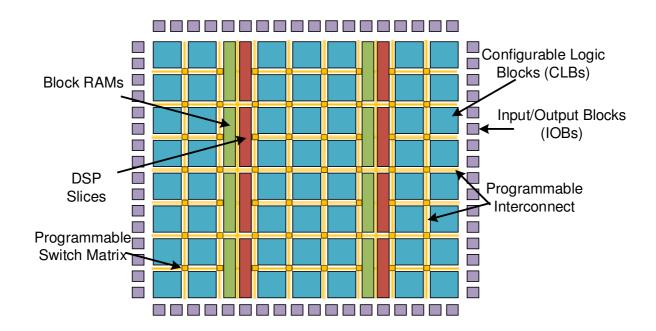

Figure 1-2 shows the general architecture of FPGA. It can be seen from the figure that the

FPGA includes a large amount of Configurable Logic Blocks (CLB) Slices, Block RAMs, DSP-DSP48E1 Slices and Input/Output blocks, which are interconnected by a number of column and row programmable interconnects to form a two dimensional architecture.

Figure 1-2 General FPGA architecture

#### Configuration Logic Block (CLB)

Configurable logic block (CLB) is the basic repeating logic resource on FPGA. CLBs contain smaller components, including flip-flops, look-up tables (LUTs), and multiplexers. The LUTs in Virtex-6 FPGAs can be configured as either one 6-input LUT (64-bit ROMs) with one output, or as two 5-input LUTs (32-bit ROMs) with separate outputs. Each LUT output can optionally be registered in a flip-flop. Four such LUTs and their eight flip-flops as well as multiplexers and arithmetic carry logic form a slice, and two slices form a CLB.

#### Block RAM (BRAM)

Block RAM (BRAM) on FPGA is a dedicated slice of random access memory that is embedded throughout an FPGA for data storage. Each block RAM has two completely

independent ports that share the stored data. Each memory access, read and write, is controlled by the clock. BRAM can be used to transfer data or store large data sets more efficiently than RAM built from LUTs.

#### DSP-DSP48E1 Slice

Digital signal processing applications require large number of binary multipliers and accumulators if realized using logic resources. Therefore dedicated DSP slices are provided to improve efficiency. The DSP48E1 slice provides extensive pipelining and extension capabilities that enhance speed and efficiency of many applications, such as wide dynamic bus shifters, memory address generators, wide bus multiplexers, and memory-mapped I/O register files. The accumulator can also be used as a synchronous up/down counter.

#### Input/Output

Input and output (I/O) resources on FPGA are physical structures that allow the user to connect FPGA to other devices. I/O blocks are usually arranged at the periphery of the FPGA architecture and also connected to the programmable interconnect. The FPGA I/O pins are configurable and can comply with different standards.

#### 1.2.4 Application of FPGA in Real-Time Simulation

FPGA has already being widely used in communication [116-122], control [123-129], and computer engineering [130-134]. Due to its inherent parallel processing ability and pipelined design, FPGA is beginning to play a more important role in real-time simulations. For example, FPGA has been used in the capture of high-precision pulses, high density digital I/O applications and Pulse Width Modulation (PWM) signal generations [135-138]. In terms of large scale power system simulation, FPGA has the features of parallel processing, pipelined

design and high clock speed. At the same time, the calculation of power system dynamics can be carried out in a paralleled and pipelined manner, which will be discussed in detail in later chapters. Therefore, FPGA is particularly suitable for the simulation of large scale power systems. With the fast increasing logic density, capacity and speed as well as the reducing power consumption and price, the FPGA will play an even bigger role in real-time simulation of electrical power systems.

Because of these advantages, some effort has been made in utilizing FPGA to achieve realtime simulations of power systems. For example in RTDS and eMEGAsim, the FPGA has been used to simulate part of the power systems with small time-step [89, 139]. Currently the only model available in FPGA is the MMC HVDC converters. In these applications, the FPGA is used as supplementary simulation hardware to the main DSP/CPU/RISC based simulators. Some other works have focused on the use of FPGA as the main simulation hardware [79, 94, 95, 140-146]. Reference [94] implemented the EMT models of frequency dependent transmission lines and passive components into FPGA to achieve real-time simulations. The designed simulator is based on 46-bit floating-point number, and can achieve a simulation time-step of 12µs when simulating a system with 15 transmission lines, 4 synchronous generators and 8 loads. An oscilloscope was used to measure the system response. Reference [140] proposed an iterative non-linear EMT solver to implement the Newton-Raphson method in solving non-linear equations. Simulation case studies of surge arresters and non-linear reactors were carried out to demonstrate the performance. Reference [141, 142] implemented the EMT models of universal machines, universal lines, and transformers with hysteresis characteristics into the FPGA. Reference [144] proposed a generalized, parallel implementation methodology for real-time simulation of AC machine transients. A simulation time-step of a few hundred nanoseconds was achieved. Based on the

method proposed in [94], reference [95, 143] further develops the FPGA based simulator for the simulation of large power systems. A 420 bus system has been simulated with a simulation time-step of 45µs. The simulation of high-frequency power electronic devices in FPGA is discussed in [79]. With limited external AC systems, a simulation time-step of 60ns can be achieved. Reference [145, 146] introduces the switching functions of power electronic switches into FGPA to simulate power electronic based machine-driving systems. Simulation time-step of 12.5ns was achieved.

From the above analysis, it can be seen that the computational ability of FPGA is highly suitable for the application of real-time simulation of power systems. In particular very small time-steps can be achieved for fast-switching power electronic devices, and small time-steps can be achieved for very large AC power systems. The downside of FPGA is that currently there is no Graphical User Interface (GUI) for FPGA-based simulator, hence the visualisation of results and the manipulations of the simulated system (change of topology, system/controller parameters) are not convenient compared with commercial real-time simulators such as RSCAD or SIMULINK. Therefore it would be very advantageous to integrate FPGA with other simulators to form an integrated simulation platform. This platform will inherit the merits of better visualization and flexibility from commercial real-time simulators and the fast computational speed and parallelism from FPGAs. This thesis, by integrating the FPGA with RTDS, tries to achieve both fast simulation speed and high simulation accuracy for the simulation of large power systems.

# 1.3 Project Objective, Contributions and Thesis Outline

# 1.3.1 Project Objectives

The main objectives of the project are to:

- Develop detailed EMT models of power system components suitable for implementation

in FPGA. Models for synchronous machines, transmission lines, passive components,

voltage/current sources and circuit breakers should be included.

- 2. Develop detailed EMT models of non-linear control systems for synchronous machines.

Models for excitation systems and governor/turbine systems should be included.

- Implement the developed models into hardware modules in FPGA. Pipelined computation schemes and paralleled architecture between hardware modules should be carefully designed.

- 4. Develop a generic FPGA-based EMT simulator for power system simulation.

- 5. Integrate FPGA with RTDS to develop a real-time FPGA-RTDS co-simulator.

- 6. Expand the capability of the co-simulator by introducing multi-FPGA architecture for the simulation of large scale power systems.

### 1.3.2 Contributions of the Thesis

The main contributions of the work in this thesis are summarized as follows:

- The co-simulation methodology integrating FPGA and RTDS for real-time large scale power system simulations.

- 2. The massively paralleled and deeply pipelined FPGA algorithms for the EMT modelling of power system components and control systems.

- 3. The scalable multi-FPGA structure and algorithm in simulating very large scale power systems.

### 1.3.3 Thesis Outline

The outline of the thesis is as follows:

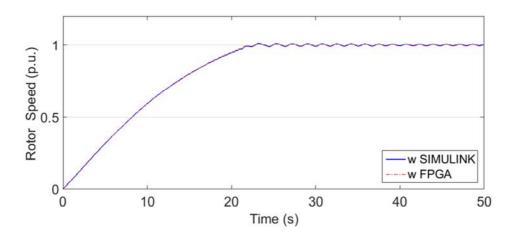

Chapter 2 In this chapter, a library of power system components using EMT models is developed in FPGA, including most of the common power system elements (synchronous machines, transmission lines, passive elements, voltage/current sources and circuit breakers) and their control systems (excitation systems and governor systems). The EMT modelling and hardware implementation of each module are described. Comparisons between FPGA and SIMULINK are made to verify the accuracy of the developed models.

**Chapter 3** This chapter describes the hardware implementation of FPGA based real-time simulator from a system point of view. Deeply pipelined and massively paralleled computation scheme of FPGA are designed to minimize the requirement on hardware resources. A four-machine two-area power system is simulated using FPGA and comparisons are made with RTDS to verify the accuracy of the simulator and the developed algorithms.

Chapter 4 By integrating FPGA and RTDS together, the FPGA-RTDS co-simulator is developed. The mathematical foundations and hardware implementation of the interface between FPGA and RTDS are explained in detail. Case study of the four-machine two-area power system with one area simulated in FPGA and the other area simulated in RTDS is carried out and comparisons are made with the complete system simulated in RTDS. In addition, simulation results of a 141-bus system are presented to demonstrate the capability of the co-simulator. The expandability of the co-simulator and the relationships between the hardware resource, simulation time-step and the size of system is discussed in detail.

**Chapter 5** In this chapter, multi-FPGA structure is proposed and the multi-FPGA-RTDS cosimulator is developed for the simulation of large scale power systems. Methods and guidelines of network partition are discussed for the allocation of computational load among FPGAs. Two types of architectures are proposed for the co-simulator. The advantages and

disadvantages of both architectures and corresponding interface designs are discussed. Simulation case study utilizing 10 FPGAs to simulate a large scale power system with more than 4000 nodes is presented to demonstrate the capability of the proposed co-simulator.

**Chapter 6** This chapter draws the conclusion of the thesis and discusses possible future works.

### 1.3.4 Logical Relationships between Chapters

The relationships between the chapters are described as follows:

**Chapter 2** develops a library of power system components and control systems in FPGA, which lays the foundation for later chapters.

**Chapter 3**, using the models developed in **Chapter 2**, implements the FPGA-based EMT simulator.

**Chapter 4**, based on the FPGA-based EMT simulator developed in **Chapter 3**, designs the interface and coordination between FPGA and RTDS and develops the FPGA-RTDS cosimulator.

**Chapter 5** further expands the simulation capability of the co-simulator developed in **Chapter 4** by introducing the multi-FPGA structure to achieve the simulation of large-scale power systems.

# **Chapter 2**

# MODELLING AND HARDWARE IMPLEMENTATION OF POWER SYSTEM ELEMENTS

### 2.1 Introduction

This chapter explains the modelling of power system elements and their hardware implementations in FPGA. Section 2.2 describes the modelling and hardware implementation of the most commonly used power system components including synchronous machines, transmission lines, passive elements, voltage/current sources and circuit breakers. Section 2.3 describes the modelling and hardware implementation of control systems for synchronous machines. Section 2.4 verifies the developed models by comparing simulation results from FPGA with those from SIMULINK. Section 2.5 summarizes this chapter.

# 2.2 Power System Elements

## 2.2.1 Synchronous Machines

The synchronous machine is an indispensable part of the power system. It involves dynamics from both mechanical and electrical parts. The nonlinear behaviour of synchronous machine is closely related to the stability and dynamics of electrical power systems.

### 2.2.1.1 Overview of Solution for Synchronous Machine

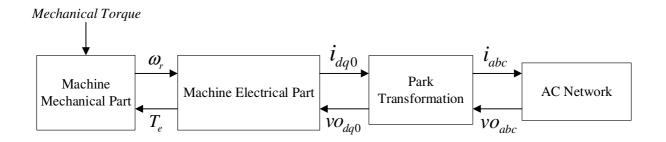

Figure 2-1 Block diagram representation of synchronous machine

Figure 2-1 shows the block diagram representation of synchronous machine. For the solution of synchronous machine, the following computational blocks are identified:

- 1. Electrical part.

- 2. Mechanical part.

- 3. External AC network

The mechanical part takes the inputs of mechanical torque  $T_m$  and electromagnetic torque  $T_e$  and calculates the rotor speed  $\omega_r$ . The machine electrical part has the inputs of rotor speed  $\omega_r$  and equivalent voltage source of external AC network  $vo_{dq0}$ , and calculates the terminal stator current in dq0 reference frame  $i_{dq0}$ . The external AC network provides the equivalent Thevenin voltage source  $vo_{abc}$  for the solution of machine electrical part. Park transformation is utilized to transform the variables from abc to dq0 reference frames.

The model of each part suitable for EMT implementation is described in following sections followed by the details solution steps of synchronous machine.

### 2.2.1.2 Model Formulation

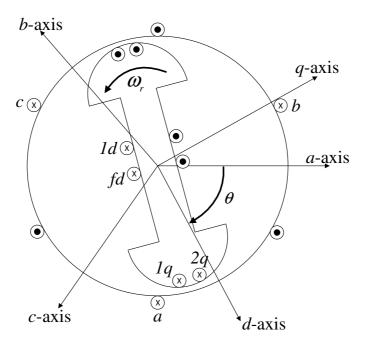

Figure 2-2 Synchronous machine schematic

Figure 2-2 shows a simplified schematic of the synchronous machine with the coil orientation, current polarities and rotor position reference. One damper winding on d-axis and two damper windings on q-axis are considered in this thesis. The direct axis (d-axis) lags the quadrature axis (q-axis) by 90 degrees.  $\theta$  is the angle different between d-axis and the phase a axis. The direction of current on rotor winding is defined as positive when flowing into the machine; the direction of current on stator windings is defined as positive when flowing out of the machine.

Under the above definitions, the Park transformation which transforms the three-phase variables in abc reference frame into dq0 reference frame can be expressed as [147]:

$$P = \frac{2}{3} \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ -\sin(\theta) & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(2.1)

The inverse of Park transformation is given by

$$P^{-1} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) & 1\\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) & 1\\ \cos(\theta + \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) & 1 \end{bmatrix}$$

(2.2)

### **Electrical Part of Synchronous Machine**

The complete dynamic behaviour of synchronous generator in dq0 reference frame can be written as [147]:

$$\begin{bmatrix} v_{d} \\ v_{q} \\ v_{0} \\ v_{f} \\ 0 \\ 0 \end{bmatrix} = - \begin{bmatrix} R_{a} & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & R_{a} & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & R_{a} & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & -R_{fd} & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & -R_{1d} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & -R_{1q} & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & -R_{2q} & 0 \end{bmatrix} \begin{bmatrix} i_{d} \\ i_{q} \\ i_{0} \\ i_{fd} \\ i_{1q} \\ i_{2q} \end{bmatrix}$$

$$+ \frac{1}{\omega_{base}} \frac{d}{dt} \begin{bmatrix} \lambda_{d} & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & \lambda_{q} & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & \lambda_{0} & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & \lambda_{fd} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & \lambda_{1q} & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & \lambda_{2q} \end{bmatrix} + \begin{bmatrix} -\omega_{r} \lambda_{q} \\ \omega_{r} \lambda_{d} \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

$$(2.3)$$

and

$$\begin{bmatrix} \lambda_{d} \\ \lambda_{q} \\ \lambda_{0} \\ \lambda_{fd} \\ \lambda_{1d} \\ \lambda_{1q} \\ \lambda_{2q} \end{bmatrix} = \begin{bmatrix} -(L_{ad} + L_{l}) & 0 & 0 & L_{ad} & L_{ad} & 0 & 0 \\ 0 & -(L_{aq} + L_{l}) & 0 & 0 & 0 & L_{aq} & L_{aq} \\ 0 & 0 & -L_{0} & 0 & 0 & 0 & 0 \\ -L_{ad} & 0 & 0 & L_{ffd} & L_{f1d} & 0 & 0 \\ -L_{ad} & 0 & 0 & L_{f1d} & L_{11d} & 0 & 0 \\ 0 & -L_{aq} & 0 & 0 & 0 & L_{11q} & L_{aq} \\ 0 & -L_{aq} & 0 & 0 & 0 & L_{aq} & L_{22q} \end{bmatrix} \begin{bmatrix} i_{d} \\ i_{q} \\ i_{0} \\ i_{1d} \\ i_{1q} \\ i_{2q} \end{bmatrix}$$

$$(2.4)$$

where the definitions of variables are listed in Table 2.1. In (2.3) and (2.4), all variables are in per unit except time, which is in second.

**Table 2.1 Definitions of Variables for Synchronous Machine**

| Name           | Definition                 | Nam<br>e       | Definition                        |

|----------------|----------------------------|----------------|-----------------------------------|

| $V_d$          | d-axis stator voltage      | $\lambda_{1d}$ | 1d damper winding flux linkage    |

| $v_q$          | q-axis stator voltage      | $\lambda_{1q}$ | 1d damper winding flux linkage    |

| $v_0$          | 0-axis stator voltage      | $\lambda_{2q}$ | 2q damper winding flux linkage    |

| $v_f$          | Excitation voltage         | $L_{ad}$       | d-axis mutual inductance          |

| $i_d$          | d-axis stator current      | $L_{aq}$       | q-axis mutual inductance          |

| $i_q$          | q-axis stator current      | $L_l$          | Leakage inductance                |

| $i_0$          | 0-axis stator current      | $L_{ffd}$      | Field winding self-inductance     |

| $i_{fd}$       | Field circuit current      | $L_{f1d}$      | Field winding leakage inductance  |

| $i_{1d}$       | 1d damper circuit current  | $L_{11d}$      | 1d damper winding self-inductance |

| $i_{1q}$       | 1q damper circuit current  | $L_{11q}$      | 1q damper winding self-inductance |

| $i_{2q}$       | 2q damper circuit current  | $L_{22q}$      | 2q damper winding self-inductance |

| $\lambda_d$    | d-axis flux linkage        | $L_0$          | 0-axis self-inductance            |

| $\lambda_q$    | q-axis flux linkage        |                |                                   |

| $\lambda_{O}$  | 0-axis flux linkage        |                |                                   |

| $\lambda_{fd}$ | Field winding flux linkage |                |                                   |

The expressions of (2.3) and (2.4) can be simplified as:

$$v_{dq0} = -Ri_{dq0} + \frac{1}{\omega_{base}} \frac{d\lambda_{dq0}}{dt} + u$$

(2.5)

$$\lambda_{da0} = Li_{da0} \tag{2.6}$$

Equations (2.5) and (2.6) describe the dynamics of electrical part of synchronous machine.

### Discretization Using Trapezoidal Rule of Integration

In order to obtain the discrete-time model for implementation on FPGA, trapezoidal rule of integration is applied to (2.5) from t- $\Delta t$  to t:

$$\begin{split} & \frac{[v_{dq0}(t) + v_{dq0}(t - \Delta t)]\Delta t}{2} = -R \frac{[i_{dq0}(t) + i_{dq0}(t - \Delta t)]\Delta t}{2} \\ & + \frac{1}{\omega_{base}} [\lambda_{dq0}(t) - \lambda_{dq0}(t - \Delta t)] + \frac{[u(t) + u(t - \Delta t)]\Delta t}{2} \end{split} \tag{2.7}$$

Rearrange (2.7)

$$v_{dq0}(t) = -Ri_{dq0}(t) + \frac{2}{\omega_{base}\Delta t} \lambda_{dq0}(t) + u(t) + v_{hist}$$

(2.8)

where

$$v_{hist} = -v_{dq0}(t - \Delta t) - Ri_{dq0}(t - \Delta t) - \frac{2}{\omega_{base}\Delta t} \lambda_{dq0}(t - \Delta t) + u(t - \Delta t)$$

(2.9)

From (2.8) it can be seen that a linear relationship between the stator voltage and current are obtained for each time-step if the rotor speed is known. The history term of  $v_{hist}$  is calculated using values from previous time-step.

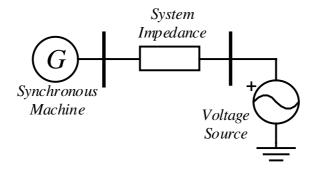

### Representation of External AC System

External AC system is solved without the machine to get the Thevenin equivalent impedance  $R_{th}$  and Thevenin voltage source  $vo_{abc}$  (details will be shown in Chapter 3). Then the AC system can be represented by a Thevenin equivalent circuit:

$$v_{abc} = vo_{abc} + R_{b}i_{abc} \tag{2.10}$$

Transform (2.10) into dq0 reference frame by multiplying P (Park transformation matrix) to both sides,

$$\begin{bmatrix} v_d \\ v_q \\ v_0 \end{bmatrix} = \begin{bmatrix} vo_d \\ vo_q \\ vo_0 \end{bmatrix} + R_{th\_dq0} \begin{bmatrix} i_d \\ i_q \\ i_0 \end{bmatrix}$$

(2.11)

where

$$\begin{bmatrix} vo_d \\ vo_q \\ vo_0 \end{bmatrix} = P \begin{bmatrix} vo_a \\ vo_b \\ vo_c \end{bmatrix}$$

(2.12)

And

$$R_{th_{-}dq0} = PR_{th}P^{-1} (2.13)$$

To solve the stator currents in  $dq\theta$  reference frame, (2.11) is substituted into (2.8):

$$\begin{bmatrix} vo_{d} \\ vo_{q} \\ vo_{0} \\ v_{f} \\ 0 \\ 0 \\ 0 \end{bmatrix} + R_{sys}i_{dq0} = -Ri_{dq0} + \frac{2}{\omega_{base}\Delta t} \lambda_{dq0} + u + v_{hist}$$

(2.14)

where

$$R_{sys} = \begin{bmatrix} R_{th\_dq0(3\times3)} & O_{3\times4} \\ O_{4\times3} & O_{4\times4} \end{bmatrix}$$

(2.15)

Substitute (2.6) into (2.14),

$$(R_{sys} + R - \frac{2}{\omega_{base}\Delta t} L - WL)i_{dq0} = v_{hist} - \begin{bmatrix} vo_d \\ vo_q \\ vo_0 \\ v_f \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

(2.16)

where

(2.16) is used to calculate stator current using the known history term of  $v_{hist}$  and the calculated Thevenin equivalent of external AC system.

### Mechanical Part of Synchronous Machine

According to Newton's second law, the mechanical part of the machine can be described by the following equations [147]:

$$\overline{T}_{m} = 2H \frac{d\overline{\omega}_{r}}{dt} + \overline{D}\overline{\omega}_{r} + \overline{T}_{e}$$

(2.18)

$$T_e = \lambda_d i_q - \lambda_q i_d \tag{2.19}$$

where H is the per unit inertia constant and D is the damping coefficient. In (2.18) and (2.19), all variables are in per unit except time. The unit of time in (2.18) is in second.

### Discretisation of Mechanical Equations

According to the trapezoidal rule of integration, (2.18) can be discretised as

$$\frac{[T_m(t) + T_m(t - \Delta t)]\Delta t}{2} = 2H[\omega(t) - \omega(t - \Delta t)]$$

$$+D\frac{[\omega(t) + \omega(t - \Delta t)]\Delta t}{2} + \frac{[T_e(t) + T_e(t - \Delta t)]\Delta t}{2}$$

(2.20)

It can be simplified to

$$T_m(t) = (\frac{4H}{\Delta t} + D)\omega(t) + T_e(t) + T_{hist}$$

(2.21)

where

$$T_{hist} = -T_m(t - \Delta t) + (D - \frac{4H}{\Delta t})\omega(t - \Delta t) + T_e(t - \Delta t)$$

(2.22)

(2.21) is used to calculate the rotor speed with the inputs of mechanical and electromagnetic torque and history term from previous time-step.

### Estimation of Rotor Speed & Rotor Angle

In order to calculate the machine terminal current, the machine electrical part requires the rotor speed and Thevenin equivalent voltage source of the network. However, the machine rotor speed is unknown at the beginning of the time-step, and estimation of rotor speed is needed for the calculation. Consider the large inertia of rotor and small simulation time-step of, simple linear estimation can be adopted:

$$\omega_{p}(t) = 2\omega(t - \Delta t) - \omega(t - 2\Delta t) \tag{2.23}$$

In (2.23), all variables are expressed in per unit. Then the rotor position can be estimated using trapezoidal rule of integration,

$$\Delta \theta = \theta(t) - \theta(t - \Delta t) = \frac{\Delta t}{2} [\omega(t - \Delta t) + \omega_p(t)] \omega_{base}$$

(2.24)

Notice that in (2.24), the rotor speed is in per unit, and the unit for time is second. The base value of rotor speed is multiplied to get the rotor position in radians.

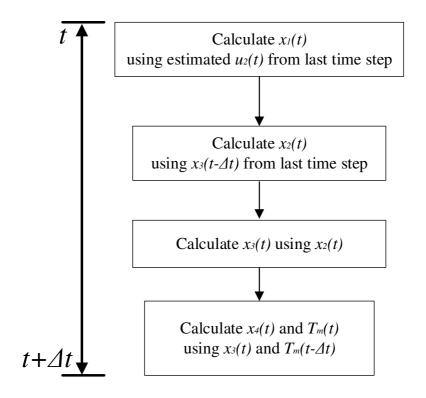

### Solution Steps for Synchronous Machine

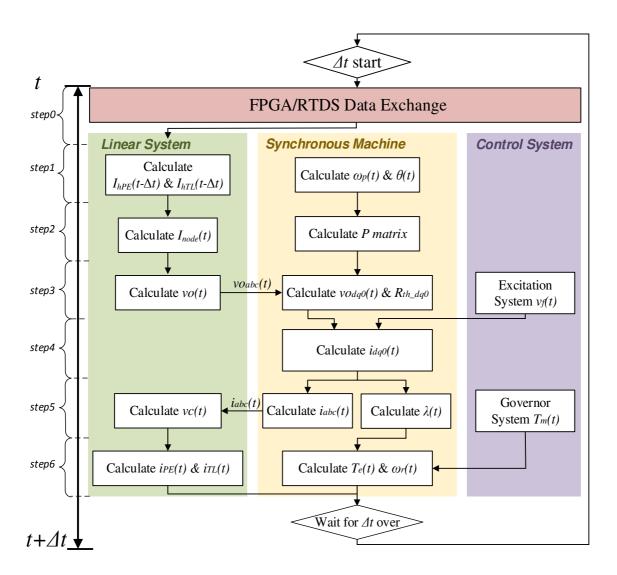

With the derived mathematical models for electrical and mechanical part of the machine, the solution steps can be summarized. Figure 2-3 shows the flow chart describing the solution steps for one time-step. Firstly, the Thevenin equivalent impedance and voltage source of the external AC network is calculated (details are explained in Chapter 3). The rotor speed and rotor position are also estimated. Secondly the Park transformation matrix is calculated using

the estimated rotor position. Thirdly the stator terminal currents are calculated, followed by the calculation of electromagnetic torque. Then the rotor mechanical speed is calculated using the calculated electromagnetic torque. Finally, the current injections from synchronous machine are exported to the external AC system for solution of the whole system.

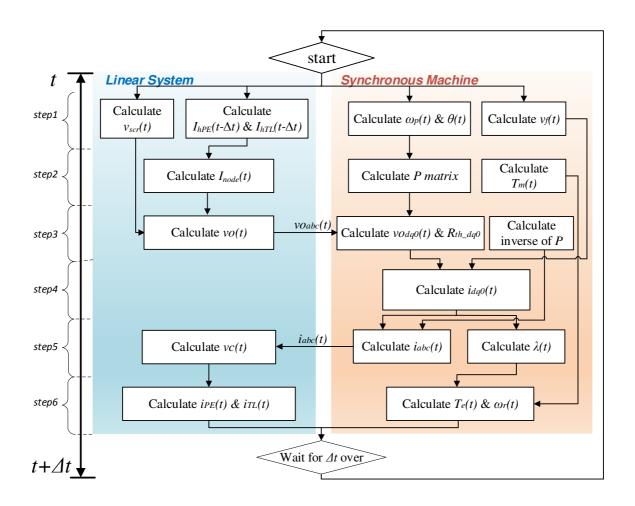

Figure 2-3 Solution steps for synchronous machine

### 2.2.1.3 Hardware Implementation

The hardware implementation of synchronous machine consists of five modules: rotor speed and position prediction module, Park and inverse Park transformation module, stator current module, flux linkage calculation module and electromagnetic torque & rotor speed module.

In this section, they will be described in detail according to the order of solution steps.

### 2.2.1.3.1 Rotor Speed and Position Prediction Module

Firstly, the rotor speed and rotor position are estimated by the rotor speed and position prediction module. Predicted machine rotor speed for the current time-step is made using rotor speed from last two time-steps as shown in equation (2.23). Then rotor angle is calculated using the predicted rotor speed as equation (2.24).

Figure 2-4 Rotor speed and position prediction module

As shown in Figure 2-4, the rotor speed and position prediction module consists of two floating point multipliers, two floating point adder and two floating point subtractors.

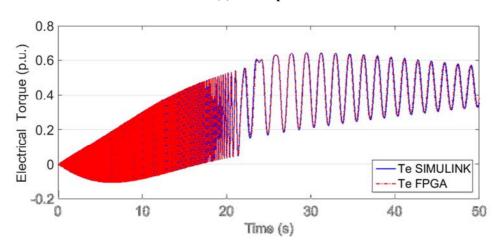

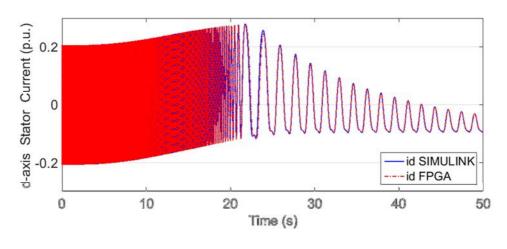

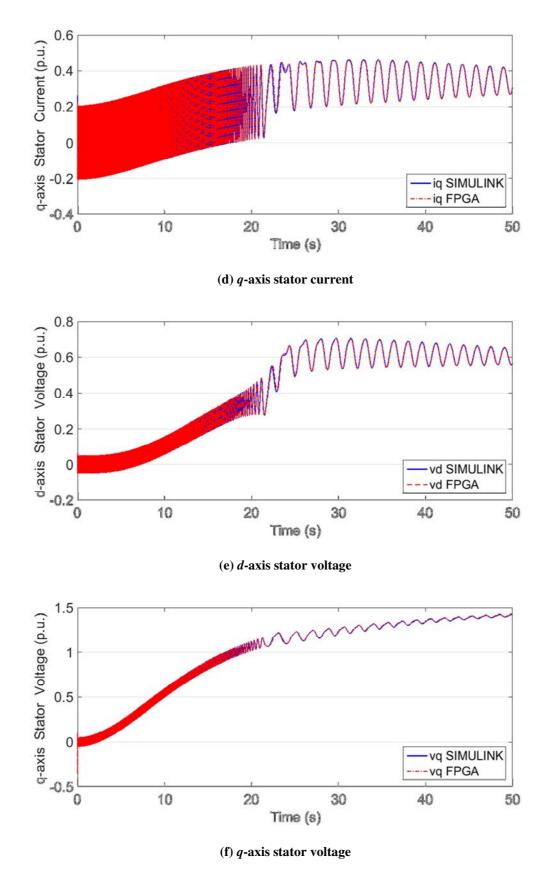

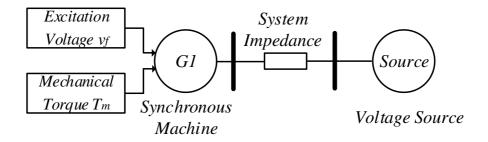

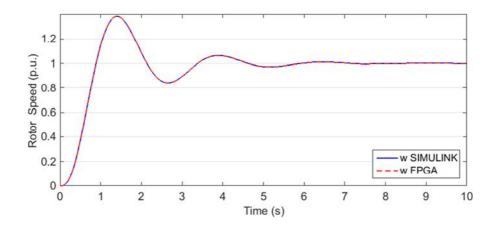

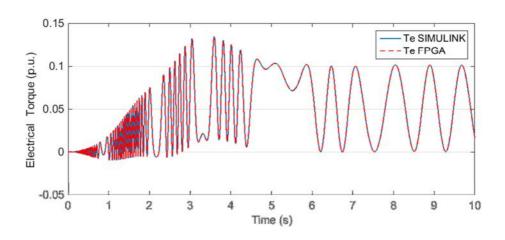

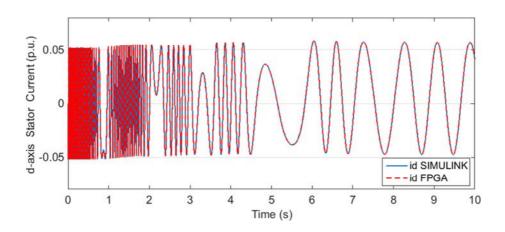

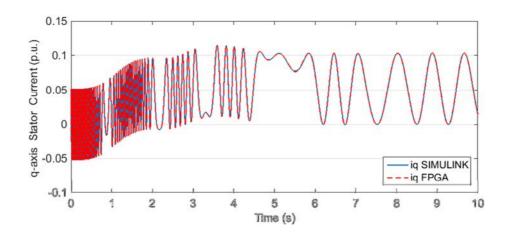

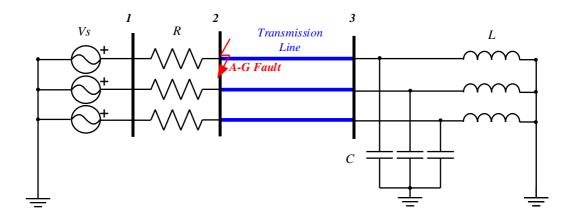

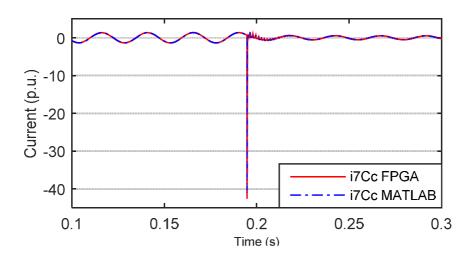

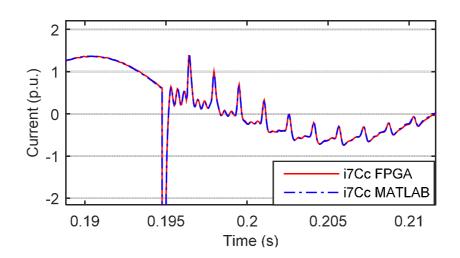

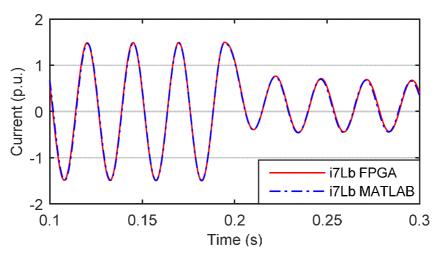

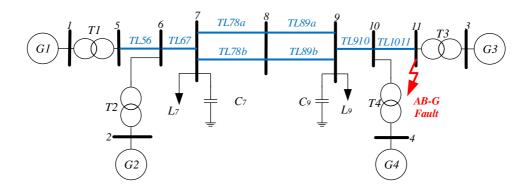

The algorithm in each time-step of this module is shown below: