### A Power-Scalable Variable-Length Analogue DFT Processor for Multi-Standard Wireless Transceivers

By

Ghazal Tanhaei

A Thesis submitted to The University of Birmingham for the degree of

#### DOCTOR OF PHILOSOPHY

School of Electronic, Electrical and System Engineering College of Engineering and Physical Sciences The University of Birmingham September 2016

### UNIVERSITY<sup>OF</sup> BIRMINGHAM

#### **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

Dedicated to my parents, Nasrin and Khosrow

for their endless love, encouragements and sacrifices

### ABSTRACT

Since the invention of the mobile phone, a new generation of mobile communication standard has emerged every 10 years. Upgrading the technology of mobile networks in all areas takes few years. Hence, mobile phones should support the previous communication standards as well as the latest standards. Realizing a multi-standard mobile phone by multiple transceivers in parallel is neither a size-efficient nor a cost-efficient solution. Hence, modern mobile phones demand reconfigurable transceivers. It is also essential for mobile phones to consume power efficiently. Hence, the multi-standard transceiver should scale its power consumption to the standard specifications. Many recent communication standards are based on the Orthogonal Frequency-Division Multiplexing (OFDM). In the OFDM based transceivers, digital computation of the Discrete Fourier Transform (DFT) is a power hungry process. Reduction in the hardware cost and power consumption is possible by implementing the DFT processor with analogue circuits. Accordingly, the goal of this work is to design a power-scalable variable-length analogue DFT processor for multi-standard OFDM transceivers.

Since the Fast Fourier Transform (FFT) algorithm reduces the computational burden of the DFT, it has been used to reduce the hardware cost and power consumption of the digital DFT processors for years. However, the FFT algorithm was originally designed for discrete-time signal processing. This thesis presents the real-time recursive DFT architecture, which was designed based on the characteristics of the analogue signal processing domain. The optimal architecture for the analogue DFT is achieved by keeping the signal continuous as long as possible.

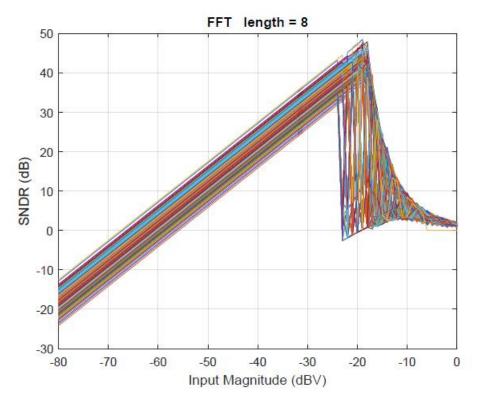

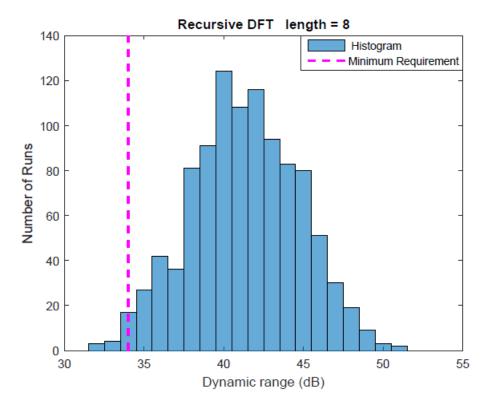

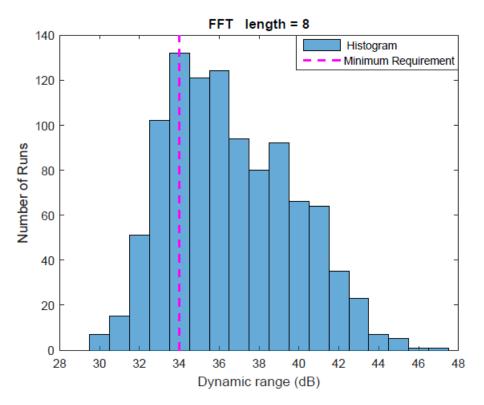

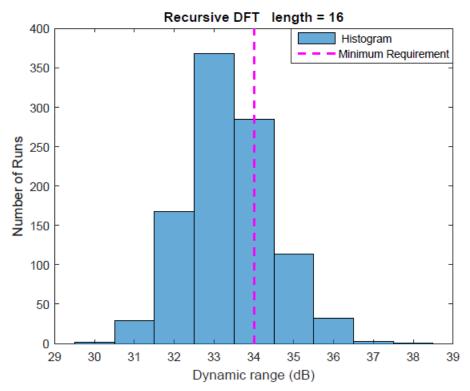

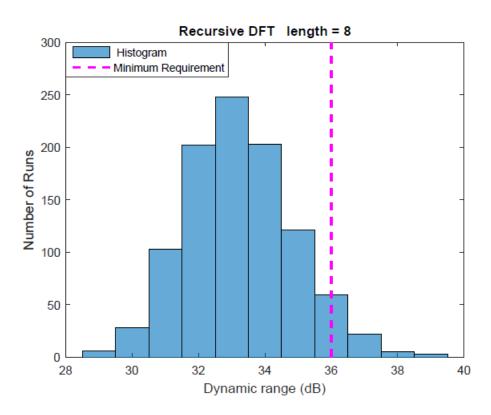

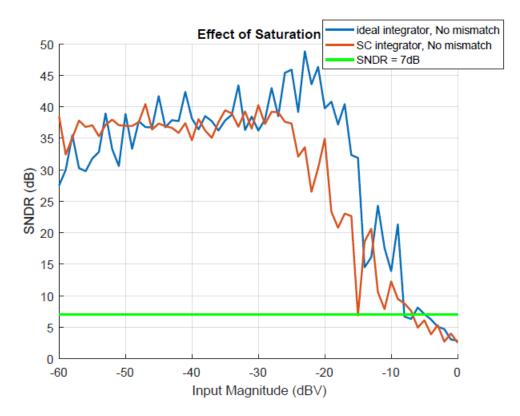

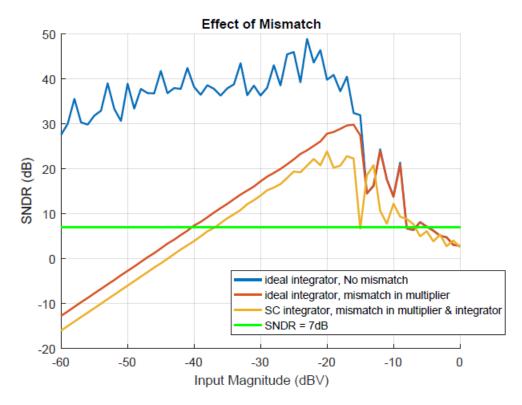

In order to analyse the performance of the proposed architecture, system-level simulations on the real-time recursive DFT processor and the radix-2 FFT processor of length 8 were performed. Results of the system performance analysis indicate that the average dynamic range of the proposed processor is 4.7 dB higher than the FFT processor. In the Monte Carlo analysis, the DFT processors that succeed in meeting the minimum dynamic range requirement (34dB) contribute to the yield. Accordingly, the proposed architecture has a yield of 99.3% while the yield of the FFT processor is 82.8%.

The real-time recursive DFT architecture was realized by the four-quadrant transconductance multipliers and the parasitic-insensitive switched-capacitor integrators. The real-time recursive DFT processor was designed in 180 nm CMOS technology. Sensitivity of the real-time recursive DFT processor to device mismatch was analysed using the Pelgrom's model. Results of device mismatch analysis indicate that the 8-point recursive DFT processor has a yield of 97.5% for the BPSK modulated signal. For the QPSK modulated signal, however, yield of the 8-point recursive DFT processor is 8.9%. Moreover, doubling the transform length reduces the average dynamic range by 3dB. Accordingly, the 16-point recursive DFT processor has a yield of 43.4% for the BPSK modulated signal. Power consumption of the recursive DFT processor is about 1/6 of the power consumption of a previous analogue FFT processor.

This thesis provided a proof-of-concept for the power-scalable variable-length analogue DFT processor. Previously, changing the transform length and scaling the power could only be performed by digital FFT processors. By using the real-time recursive DFT processor, the analogue decimation filter is eliminated. Thus, further reduction in the hardware cost and power consumption of the multi-standard transceiver is achieved.

### ACKNOWLEDGEMENTS

First and foremost, I would like to thank my parents and my sister for their encouragements and financial support. My parents have been financially supporting me during the recession only because of their high value for education. None of this would have been possible without their love and support.

I would like to express my sincere gratitude to my advisors, Dr Steven Quigley and Professor Peter Gardner, for their guidance and patience throughout my PhD study. Although they have provided me a peaceful atmosphere at the University, they gave me the freedom to work from home.

Besides my advisors, I would like to thank Dr Kamyar Keikhosravy, postdoctoral fellow at the University of British Columbia, for sharing his expertise despite the distance. His modest personality makes him approachable. I am glad that this research has led to a great friendship.

I would also like to thank Professor Costas Constantinou and Professor Khaled Hayatleh for their insightful comments and constructive criticisms.

I am also indebted to all my teachers from elementary school to graduate school, especially my electronics professor at the Amirkabir University of Technology, Dr Saeed Khatami (Rest In Peace). In the early years of higher education, his encouragements inspired me with confidence.

I wish also to express my gratitude to the University of Birmingham for awarding me the TI Group scholarship, which partially supported my research.

### **CONTENTS**

| СНАРТЕ | ER 1   | INTRODUCTION                                     | 1 |

|--------|--------|--------------------------------------------------|---|

| 1.1    | Evolu  | ITION OF COMMUNICATION SYSTEMS                   | 1 |

| 1.2    | State  | MENT OF THE PROBLEM                              | 6 |

| 1.3    | DISSEF | RTATION OBJECTIVES                               | 8 |

| 1.4    | Signif | ICANCE OF THE RESEARCH                           | 8 |

| 1.5    | THESIS | OUTLINE                                          | 9 |

| СНАРТЕ | ER 2   | BACKGROUND STUDY AND LITERATURE REVIEW1          | 1 |

| 2.1    | Funda  | AMENTALS OF OFDM                                 | 1 |

| 2.2    | WIFI A | and WIMAX Physical Layer Overview                | 0 |

| 2.3    | State  | -of-the-Art FFT Processors                       | 2 |

| 2.4    | Сомр   | ARISON OF ANALOGUE AND DIGITAL SIGNAL PROCESSING | 2 |

| 2.5    | ANALC  | DGUE FOURIER TRANSFORM ARCHITECTURES             | 4 |

| 2.     | 5.1    | The Direct Form Finite Impulse Response          | 4 |

| 2.     | 5.2    | The Fast Fourier Transform                       | 6 |

| 2.6    | Summ   | 1ARY                                             | 8 |

| СНАРТЕ | ER 3   | REAL-TIME RECURSIVE DFT ARCHITECTURE2            | 9 |

| 3.1    | Real-  | TIME RECURSIVE DFT FOR DIGITAL SIGNAL            | 9 |

| 3.2    | Real-  | TIME RECURSIVE DFT FOR ANALOGUE SIGNAL           | 2 |

| 3.3    | Advar  | NTAGES OF THE PROPOSED ARCHITECTURE              | 5 |

| 3.4    | Summ   | 1ARY                                             | 7 |

| СНАРТЕ | ER 4   | SYSTEM PERFORMANCE ANALYSIS                      | 8 |

| 4.1    | Perfo  | IRMANCE METRICS FOR DFT PROCESSOR                | 8 |

| 4.2               | PERFO                                                                                 | DRMANCE REQUIREMENTS                                                                                                                                                                                                                                                                    | 40                                                        |

|-------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 4.3               | Вена                                                                                  | VIOURAL MODELLING                                                                                                                                                                                                                                                                       | 43                                                        |

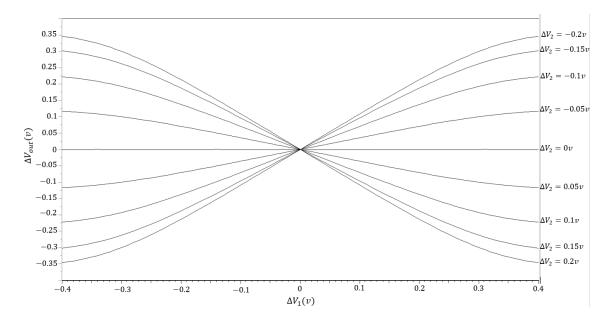

|                   | 4.3.1                                                                                 | Behavioural Model of the Multiplier                                                                                                                                                                                                                                                     | 44                                                        |

|                   | 4.3.2                                                                                 | Behavioural Model of the Integrator                                                                                                                                                                                                                                                     | 46                                                        |

|                   | 4.3.3                                                                                 | Behavioural Modelling of the FFT Processor                                                                                                                                                                                                                                              | 48                                                        |

|                   | 4.3.4                                                                                 | Behavioural Modelling of the Recursive DFT Processor                                                                                                                                                                                                                                    | 54                                                        |

| 4.4               | Detei                                                                                 | RMINING THE DESIGN SPECIFICATIONS                                                                                                                                                                                                                                                       | 57                                                        |

|                   | 4.4.1                                                                                 | Power Budget                                                                                                                                                                                                                                                                            | 57                                                        |

|                   | 4.4.2                                                                                 | Design Specifications of the Multiplier                                                                                                                                                                                                                                                 | 58                                                        |

|                   | 4.4.3                                                                                 | Design Specifications of the Integrator                                                                                                                                                                                                                                                 | 63                                                        |

| 4.5               | YIELD                                                                                 | Prediction                                                                                                                                                                                                                                                                              | 66                                                        |

| 4.6               | PERFO                                                                                 | DRMANCE ANALYSIS RESULTS                                                                                                                                                                                                                                                                | 70                                                        |

| 4.7               | Sum                                                                                   | /ARY                                                                                                                                                                                                                                                                                    | 73                                                        |

|                   |                                                                                       |                                                                                                                                                                                                                                                                                         |                                                           |

| СНАР              | TER 5                                                                                 | CIRCUIT DESIGN                                                                                                                                                                                                                                                                          | 74                                                        |

| <b>CHAP</b>       | -                                                                                     | CIRCUIT DESIGN                                                                                                                                                                                                                                                                          |                                                           |

| _                 | Previ                                                                                 |                                                                                                                                                                                                                                                                                         | 74                                                        |

| 5.1<br>5.2        | Previ                                                                                 | OUS WORK ON THE ANALOGUE FFT PROCESSOR                                                                                                                                                                                                                                                  | 74<br>80                                                  |

| 5.1<br>5.2        | Previ                                                                                 | OUS WORK ON THE ANALOGUE FFT PROCESSOR                                                                                                                                                                                                                                                  | 74<br>80<br>81                                            |

| 5.1               | Previ<br>Anal<br>5.2.1                                                                | ous Work on the Analogue FFT Processor<br>ogue Multiplier<br>Principle of Operation                                                                                                                                                                                                     | 74<br>80<br>81<br>82                                      |

| 5.1               | PREVI<br>ANAL<br>5.2.1<br>5.2.2<br>5.2.3                                              | OUS WORK ON THE ANALOGUE FFT PROCESSOR<br>OGUE MULTIPLIER<br>Principle of Operation<br>Analysis of the CMOS Gilbert Cell                                                                                                                                                                | 74<br>80<br>81<br>82<br>90                                |

| 5.1<br>5.2<br>5.3 | PREVI<br>ANAL<br>5.2.1<br>5.2.2<br>5.2.3                                              | OUS WORK ON THE ANALOGUE FFT PROCESSOR<br>OGUE MULTIPLIER<br>Principle of Operation<br>Analysis of the CMOS Gilbert Cell<br>Circuit Realization                                                                                                                                         | 74<br>80<br>81<br>82<br>90<br>97                          |

| 5.1<br>5.2<br>5.3 | PREVI<br>ANAL<br>5.2.1<br>5.2.2<br>5.2.3<br>DISCR                                     | OUS WORK ON THE ANALOGUE FFT PROCESSOR<br>OGUE MULTIPLIER<br>Principle of Operation<br>Analysis of the CMOS Gilbert Cell<br>Circuit Realization<br>ETE-TIME INTEGRATOR                                                                                                                  | 74<br>80<br>81<br>90<br>97<br>98                          |

| 5.1<br>5.2<br>5.3 | PREVI<br>ANAL<br>5.2.1<br>5.2.2<br>5.2.3<br>DISCR<br>5.3.1                            | OUS WORK ON THE ANALOGUE FFT PROCESSOR<br>OGUE MULTIPLIER<br>Principle of Operation<br>Analysis of the CMOS Gilbert Cell<br>Circuit Realization<br>ETE-TIME INTEGRATOR<br>Analysis of the Parasitic-Insensitive Integrator                                                              | 74<br>80<br>81<br>90<br>97<br>98<br>. 101                 |

| 5.1<br>5.2<br>5.3 | PREVI<br>ANAL<br>5.2.1<br>5.2.2<br>5.2.3<br>DISCR<br>5.3.1<br>5.3.2<br>5.3.3          | OUS WORK ON THE ANALOGUE FFT PROCESSOR<br>OGUE MULTIPLIER<br>Principle of Operation<br>Analysis of the CMOS Gilbert Cell<br>Circuit Realization<br>ETE-TIME INTEGRATOR<br>Analysis of the Parasitic-Insensitive Integrator<br>Speed and Precision Considerations                        | 74<br>80<br>81<br>90<br>97<br>98<br>. 101<br>. 107        |

| 5.1<br>5.2<br>5.3 | PREVI<br>ANAL<br>5.2.1<br>5.2.2<br>5.2.3<br>DISCF<br>5.3.1<br>5.3.2<br>5.3.3<br>REAL- | OUS WORK ON THE ANALOGUE FFT PROCESSOR<br>OGUE MULTIPLIER<br>Principle of Operation<br>Analysis of the CMOS Gilbert Cell<br>Circuit Realization<br>ETE-TIME INTEGRATOR<br>Analysis of the Parasitic-Insensitive Integrator<br>Speed and Precision Considerations<br>Circuit Realization | 74<br>80<br>81<br>90<br>97<br>98<br>. 101<br>. 107<br>110 |

| СНАРТІ | ER 6    | DEVICE MISMATCH ANALYSIS AND RESULTS        | 116 |

|--------|---------|---------------------------------------------|-----|

| 6.1    | MOS     | Transistor Matching Models                  | 116 |

| 6.2    | MOS     | Transistor Optimum Matching                 | 118 |

| 6.3    | ΙΜΡΑΟ   | CT OF MISMATCH ON THE PERFORMANCE TRADEOFFS | 120 |

| 6.4    | ΙΜΡΑΟ   | ct of Technology Scaling on the Mismatch    | 122 |

| 6.5    | Mism    | IATCH ANALYSIS RESULTS                      | 123 |

| 6.6    | Root    | Cause Analysis                              | 128 |

| 6.7    | Μιτισ   | SATION OF THE EFFECT OF DEVICE MISMATCH     | 131 |

| 6.8    | SUMN    | ЛАRY                                        | 133 |

| СНАРТІ | ER 7    | CONCLUSION AND FUTURE WORK                  | 134 |

| 7.1    | Cont    | RIBUTIONS TO KNOWLEDGE                      | 134 |

| 7.     | 1.1     | Methodology                                 | 134 |

| 7.     | 1.2     | Limitations and Considerations              | 135 |

| 7.2    | FUTU    | RE WORK                                     | 137 |

| 7.     | .2.1    | Design Enhancements                         | 137 |

| 7.     | 2.2     | Further Analysis                            | 138 |

| LIST ( | OF REFE | RENCES                                      | 139 |

| Арре   | NDIX A  |                                             | 155 |

| Арре   | NDIX B  |                                             | 161 |

### **TABLE OF TABLES**

| TABLE 1-1: EVOLUTION OF COMMUNICATION SYSTEMS                                                       | 5   |

|-----------------------------------------------------------------------------------------------------|-----|

| TABLE 2-1: IEEE 802.11A/G PHY SPECIFICATIONS                                                        | 20  |

| TABLE 2-2: IEEE 802.16E PHY SPECIFICATIONS                                                          | 21  |

| TABLE 3-1: COMPUTATIONAL EFFICIENCY AND RESOURCE COSTS OF DIFFERENT DFT ARCHITECTURES               | 35  |

| TABLE 4-1: RECEIVER PERFORMANCE REQUIREMENTS FOR BER = 10 <sup>-6</sup>                             | 41  |

| TABLE 4-2: SUMMARY OF THE OPTIMAL VALUE FOR THE BEHAVIOURAL MODEL PARAMETERS                        | 70  |

| TABLE 4-3: SUMMARY OF THE MONTE CARLO ANALYSIS FOR THE RECURSIVE DFT AND THE RADIX-2 FFT PROCESSORS | 71  |

| TABLE 5-1: INITIAL ASPECT RATIOS OF THE COMPLEX MULTIPLIER                                          | 96  |

| TABLE 5-2: FINAL ASPECT RATIOS OF THE COMPLEX MULTIPLIER                                            | 96  |

| TABLE 5-3: INITIAL ASPECT RATIOS OF THE OP-AMP                                                      | 109 |

| TABLE 5-4: FINAL ASPECT RATIOS OF THE PARASITIC-INSENSITIVE INTEGRATOR                              | 109 |

| TABLE 6-1: SUMMARY OF THE MONTE CARLO ANALYSIS FOR THE RECURSIVE DFT PROCESSORS OF LENGTH 8         | 125 |

| TABLE 6-2: SUMMARY OF THE YIELD PREDICTION FOR THE RECURSIVE DFT PROCESSORS OF LENGTH 8 AND 16      | 127 |

| TABLE 6-3: PERFORMANCE COMPARISON OF THE ANALOGUE FOURIER TRANSFORM PROCESSORS                      | 127 |

### **TABLE OF FIGURES**

| FIGURE 1-1: MARTIN COOPER HOLDS THE DYNATAC 8000X PHONE AND HIS CURRENT MOBILE PHONE DURING THE PRINCE OF         |

|-------------------------------------------------------------------------------------------------------------------|

| ASTURIAS AWARDS CEREMONY IN 2009 [32]                                                                             |

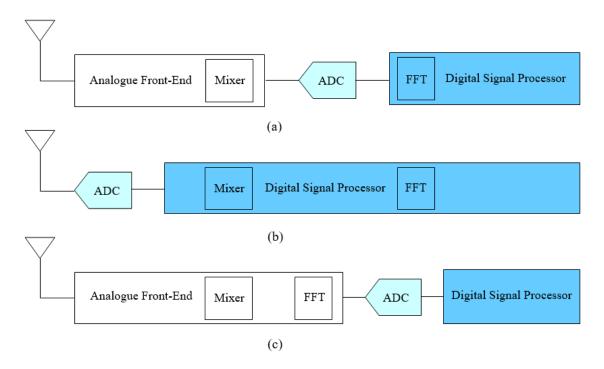

| FIGURE 1-2: ANALOGUE AND DIGITAL SIGNAL PROCESSING SECTIONS IN (A) THE CLASSICAL OFDM RECEIVER (B) THE SOFTWARE   |

| DEFINED RADIO RECEIVER (C) THE OFDM RECEIVER WITH AN ANALOGUE FFT                                                 |

| FIGURE 2-1: THE SPECTRUM OF THE FDM SIGNAL CONSISTING OF NONOVERLAPPING SUBCHANNELS [43]                          |

| FIGURE 2-2: THE SPECTRUM OF AN OFDM SIGNAL CONSISTING OF THREE OVERLAPPING SUBCARRIERS [42]                       |

| FIGURE 2-3: SUMMATION OF THE OFDM SUBCARRIERS IN THE TIME DOMAIN [1]                                              |

| FIGURE 2-4: EFFECT OF THE ISI ON THE OFDM SYMBOL IN (A) THE ABSENCE OF THE GUARD INTERVAL (B) THE PRESENCE OF THE |

| GUARD INTERVAL [1]                                                                                                |

| FIGURE 2-5: THE OFDM SYMBOL IN THE FREQUENCY DOMAIN [45]                                                          |

| FIGURE 2-6: ALLOCATION OF SUBCARRIERS TO USERS IN THE OFDM AND OFDMA TECHNOLOGIES [1]                             |

| FIGURE 2-7: WINDOWED OFDM SYMBOL IN THE TIME DOMAIN [1]                                                           |

| FIGURE 2-8: SPECTRUM OF THE OFDM SIGNAL BEFORE AND AFTER WINDOWING [45]17                                         |

| FIGURE 2-9: SYMBOL MAPPING BASED ON THE QPSK MODULATION [1]                                                       |

| FIGURE 2-10: BLOCK DIAGRAMS OF THE CLASSICAL OFDM TRANSMITTER AND RECEIVER [1]                                    |

| FIGURE 2-11: DIRECT FORM REALIZATION OF AN FIR SYSTEM [44]                                                        |

| FIGURE 2-12: SIGNAL FLOW GRAPH OF A RADIX-2 DIT FFT OF LENGTH 8 [44]                                              |

| FIGURE 2-13: SIGNAL FLOW GRAPH OF THE 2-POINT DFT [44]                                                            |

| FIGURE 3-1: SIGNAL FLOW GRAPH OF THE GOERTZEL DFT [44]                                                            |

| FIGURE 3-2: SIGNAL FLOW GRAPH OF THE GOERTZEL DFT WITH REAL MULTIPLIERS                                           |

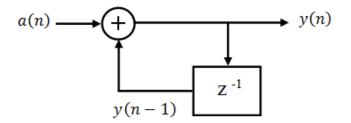

| FIGURE 3-3: BLOCK DIAGRAM OF A RECURSIVE DIFFERENCE EQUATION REPRESENTING THE DISCRETE-TIME INTEGRATOR            |

| FIGURE 3-4: ARCHITECTURE OF THE PROPOSED REAL-TIME RECURSIVE DFT                                                  |

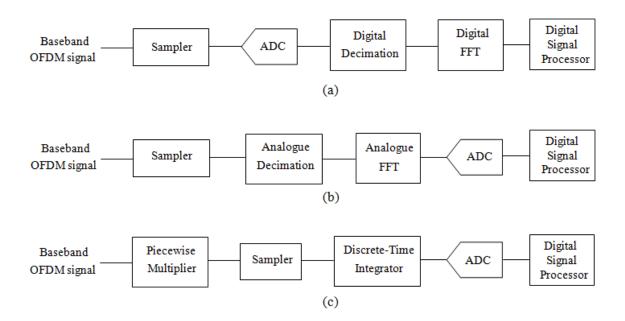

| Figure 3-5: Baseband Signal processing section in (a) the classical OFDM receiver (b) the OFDM $\sim$           |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| RECEIVER WITH AN ANALOGUE FFT OR FIR DFT OR GOERTZEL DFT (C) THE OFDM RECEIVER WITH T                           | HE |

| PROPOSED DFT                                                                                                    | 37 |

| FIGURE 4-1: TYPICAL SNDR VERSUS INPUT MAGNITUDE CURVE [41]                                                      | 40 |

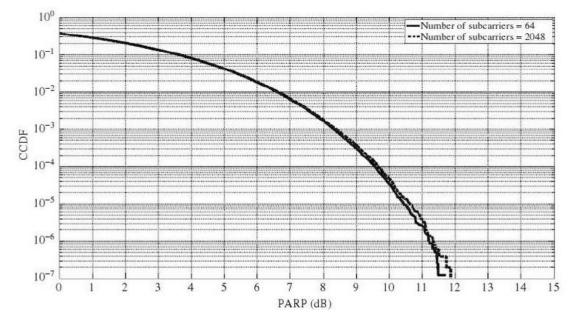

| FIGURE 4-2: PAPR CCDFs OF TWO OFDM SIGNALS WITH WIFI AND WIMAX STANDARDS [1]                                    | 42 |

| FIGURE 4-3: THE BLOCK DIAGRAM OF THE BASEBAND SIGNAL PROCESSING PART OF (A) THE CLASSICAL OFDM RECEIVER (B) THE |    |

| PROPOSED OFDM RECEIVER                                                                                          | 43 |

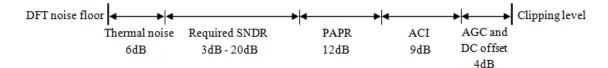

| FIGURE 4-4: ANALOGUE DFT DYNAMIC RANGE DERIVATION                                                               | 43 |

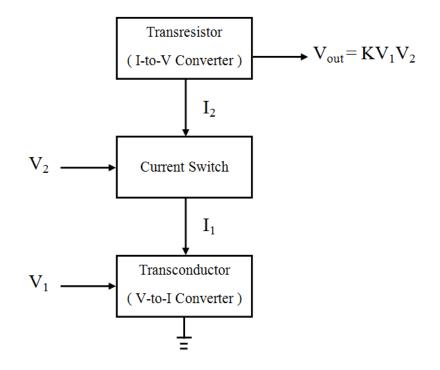

| FIGURE 4-5: BLOCK DIAGRAM OF THE ANALOGUE MULTIPLIER                                                            | 44 |

| FIGURE 4-6: CURVES OF THE MULTIPLIER BEHAVIOURAL MODEL                                                          | 45 |

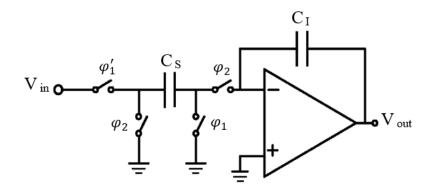

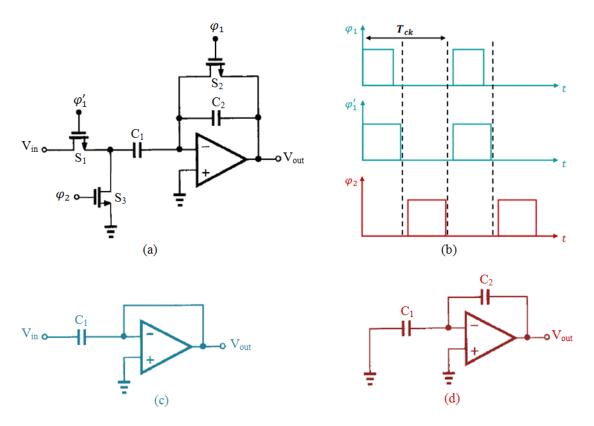

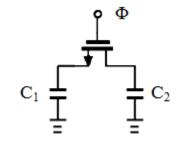

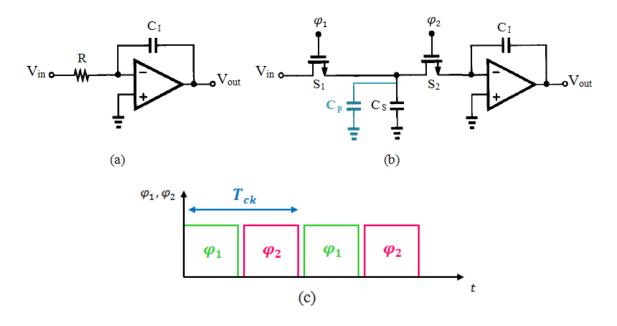

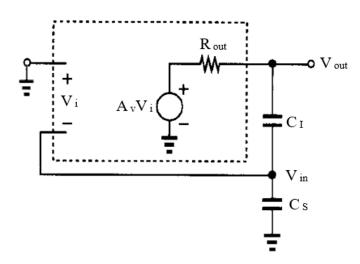

| FIGURE 4-7: SWITCHED-CAPACITOR INTEGRATOR [78]                                                                  | 47 |

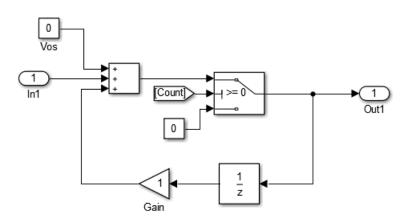

| FIGURE 4-8: BEHAVIOURAL MODEL OF THE SWITCHED-CAPACITOR INTEGRATOR IN SIMULINK                                  | 47 |

| FIGURE 4-9: SIGNAL FLOW GRAPH OF A RADIX-2 DIT FFT OF LENGTH 8 [41]                                             | 48 |

| Figure 4-10: 2-point DFT with $W81$ or $W83$ twiddle factor                                                     | 50 |

| Figure 4-11: 2-point DFT with $W80$ twiddle factor                                                              | 52 |

| FIGURE 4-12: 2-POINT DFT WITH $W82$ twiddle factor                                                              | 53 |

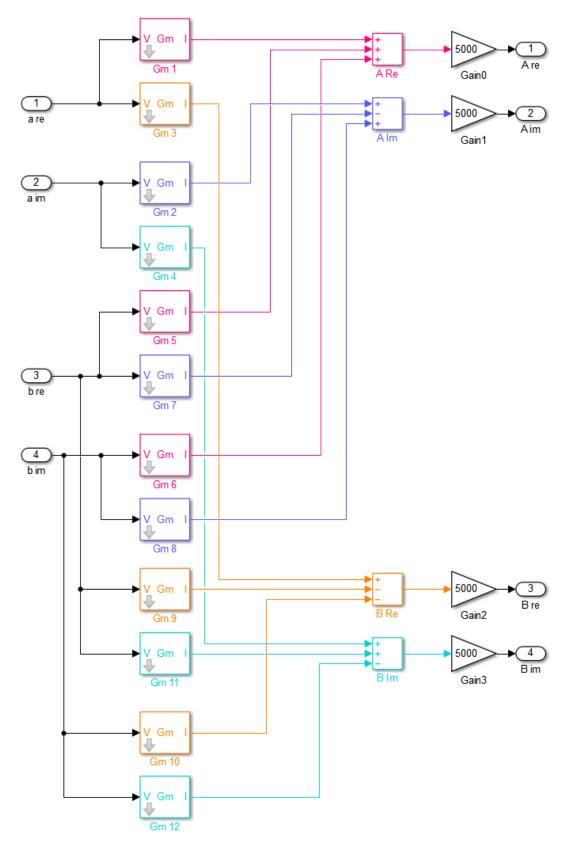

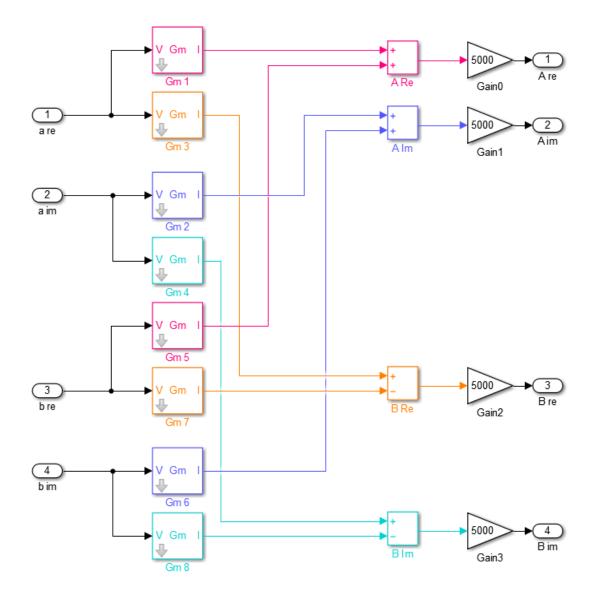

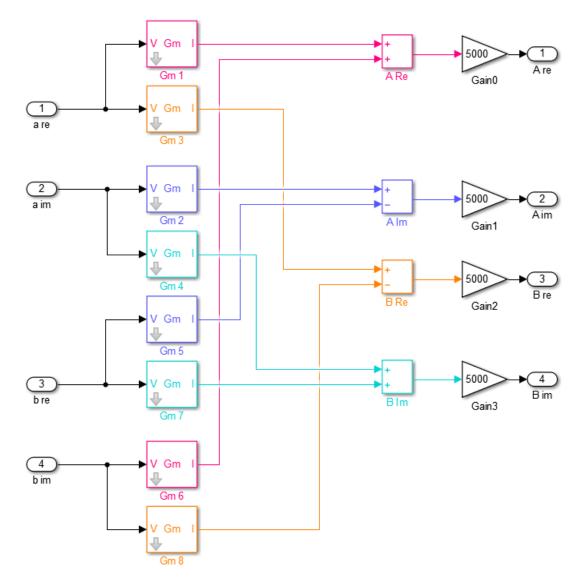

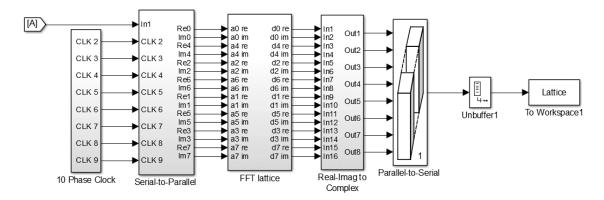

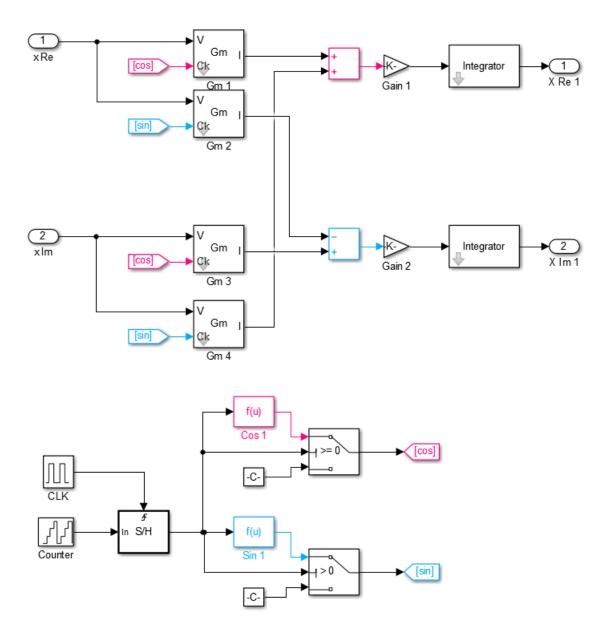

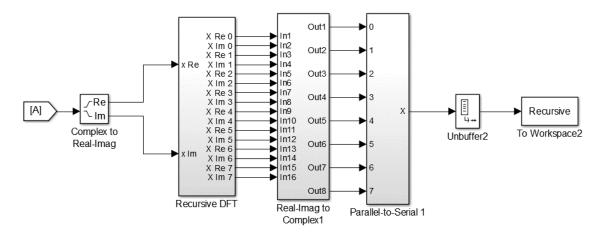

| FIGURE 4-13: BEHAVIOURAL MODEL OF THE ANALOGUE FFT PROCESSOR IN SIMULINK                                        | 54 |

| FIGURE 4-14: 1-POINT DFT WITH PIECEWISE CONTINUOUS COEFFICIENTS                                                 | 55 |

| FIGURE 4-15: BEHAVIOURAL MODEL OF THE REAL-TIME RECURSIVE DFT PROCESSOR IN SIMULINK                             | 56 |

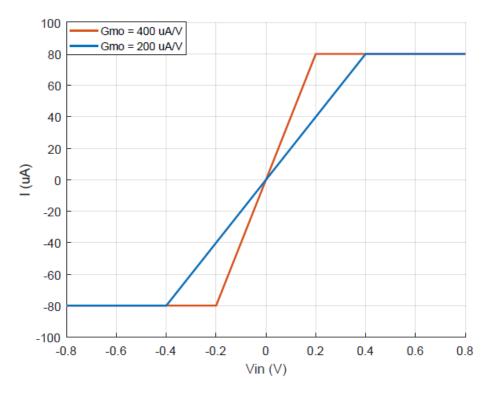

| FIGURE 4-16: THE INPUT-OUTPUT CHARACTERISTICS OF IDEAL MULTIPLIERS                                              | 59 |

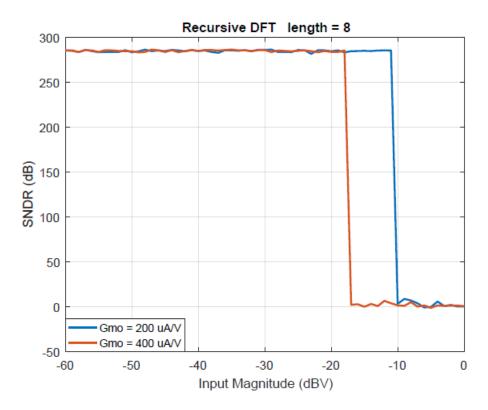

| FIGURE 4-17: SNDR CURVES FOR DIFFERENT VALUES OF <i>Gmo</i>                                                     | 59 |

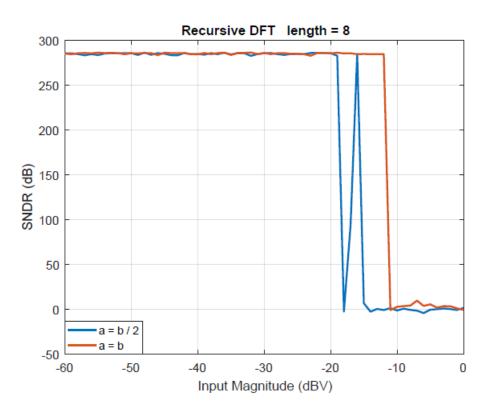

| FIGURE 4-18: SNDR CURVES FOR DIFFERENT LINEAR RANGES                                                            | 60 |

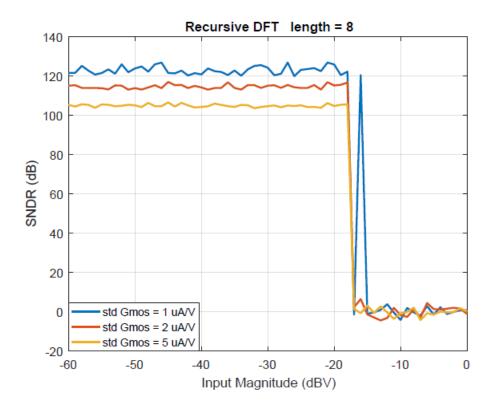

| FIGURE 4-19: SNDR CURVES FOR VARIOUS TRANSCONDUCTANCE ERRORS                                                    | 61 |

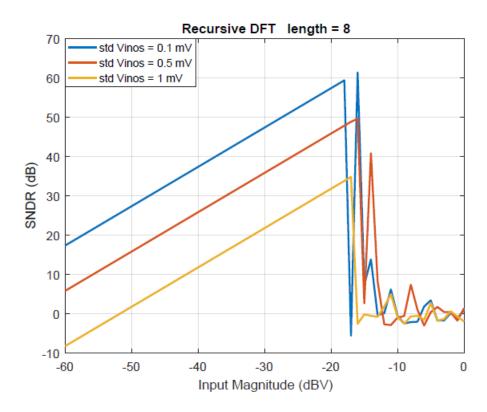

| FIGURE 4-20: SNDR CURVES FOR VARIOUS DC OFFSET MISMATCHES                                                       | 62 |

| FIGURE 4-21: SNDR CURVES FOR VARIOUS OP-AMP GAINS                                                               | 65 |

| FIGURE 4-22: SNDR CURVES FOR VARIOUS DC OFFSET MISMATCHES                                                       | 66 |

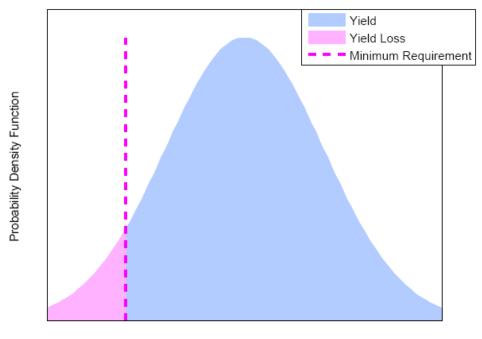

| FIGURE 4-23: YIELD PREDICTION BASED ON THE MONTE CARLO ANALYSIS [82]                                      | 67               |

|-----------------------------------------------------------------------------------------------------------|------------------|

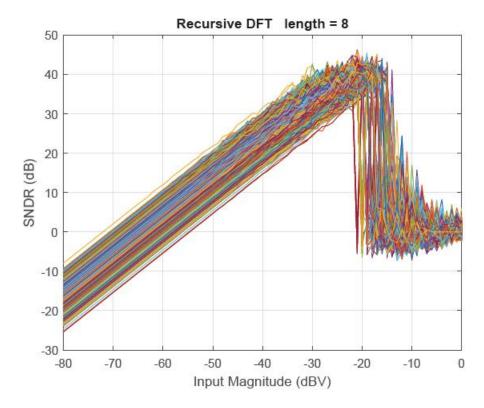

| FIGURE 4-24: MONTE CARLO ANALYSIS RESULTS OF THE REAL-TIME RECURSIVE DFT PROCESSOR                        | 71               |

| FIGURE 4-25: MONTE CARLO ANALYSIS RESULTS OF THE RADIX-2 FFT PROCESSOR                                    | 72               |

| FIGURE 4-26: THE DYNAMIC RANGE HISTOGRAM OF THE REAL-TIME RECURSIVE DFT PROCESSOR                         | 72               |

| FIGURE 4-27: THE DYNAMIC RANGE HISTOGRAM OF THE RADIX-2 FFT PROCESSOR                                     | 73               |

| FIGURE 5-1: (A) SWITCHED-CAPACITOR AMPLIFIER (B) TIMING DIAGRAM OF CIRCUIT (A)                            | 75               |

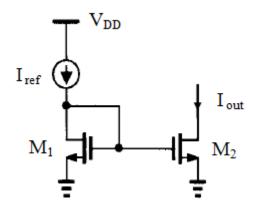

| FIGURE 5-2: THE BASIC CURRENT MIRROR [80]                                                                 | 76               |

| FIGURE 5-3: THE PASSIVE SWITCHED-CAPACITOR MULTIPLIER                                                     | 76               |

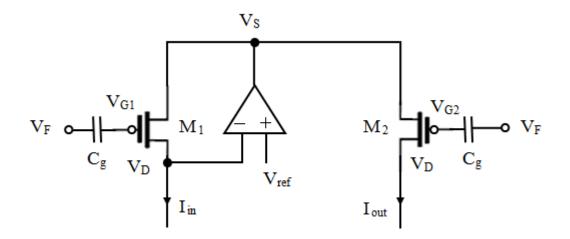

| FIGURE 5-4: THE SWITCHED-TRANSCONDUCTOR MULTIPLIER                                                        | 77               |

| FIGURE 5-5: THE FLOATING-GATE MULTIPLIER                                                                  | 78               |

| FIGURE 5-6: TWO-QUADRANT ANALOGUE MULTIPLIER [96]                                                         | 81               |

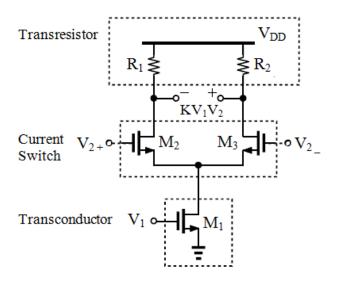

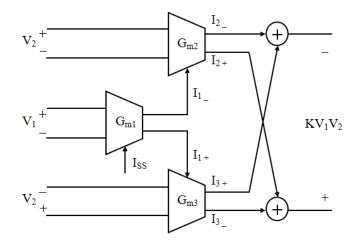

| FIGURE 5-7: BLOCK DIAGRAM OF THE GILBERT CELL                                                             | 82               |

| FIGURE 5-8: G <sub>M</sub> TRANSCONDUCTOR [80]                                                            |                  |

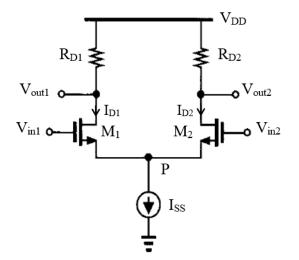

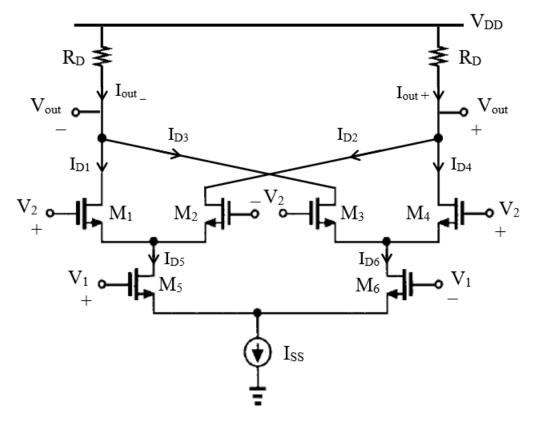

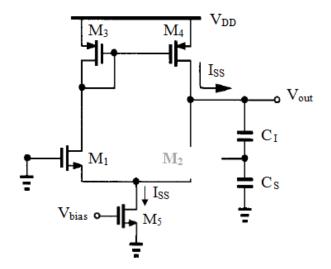

| FIGURE 5-9: GILBERT CELL                                                                                  | 86               |

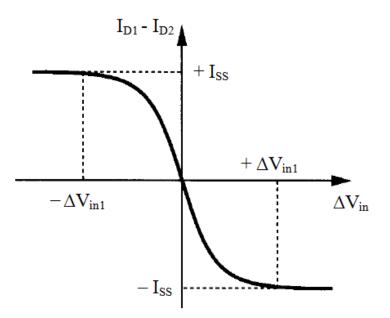

| FIGURE 5-10: INPUT-OUTPUT CHARACTERISTIC OF A DIFFERENTIAL PAIR [80]                                      | 89               |

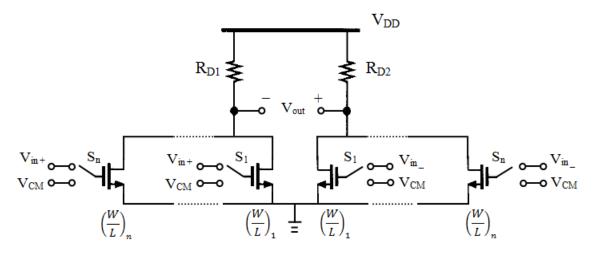

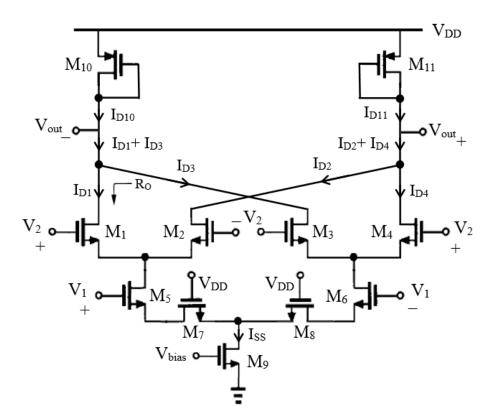

| FIGURE 5-11: DEGENERATED GILBERT CELL WITH DIODE-CONNECTED LOAD                                           | 91               |

| FIGURE 5-12: DEGENERATED GILBERT CELL WITH CMFB NETWORK                                                   | 93               |

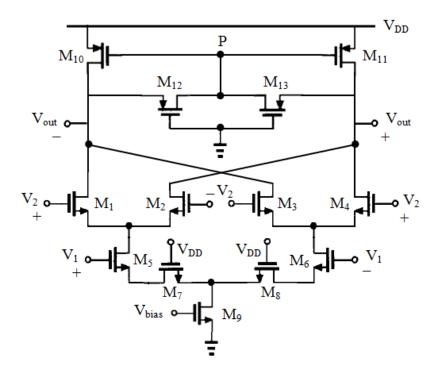

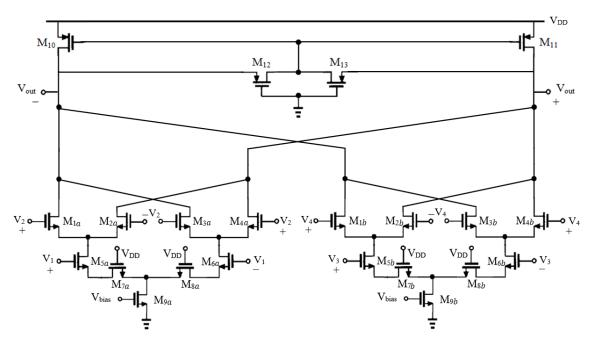

| FIGURE 5-13: TOPOLOGY OF THE COMPLEX MULTIPLIER                                                           | 94               |

| FIGURE 5-14: TRANSFER CHARACTERISTIC OF THE GILBERT CELL MULTIPLIER SIMULATED IN SPICE                    | 97               |

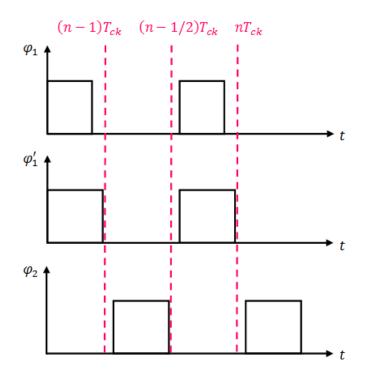

| FIGURE 5-15: (A) CONTINUOUS-TIME INTEGRATOR (B) DISCRETE-TIME INTEGRATOR (C) TIMING DIAGRAM OF CIRC       | сиіт (в) [80] 98 |

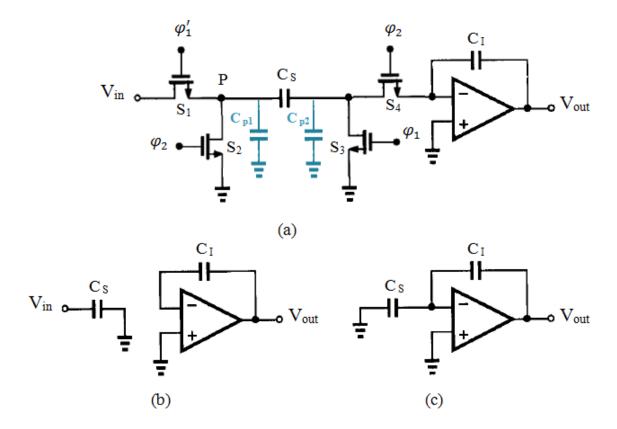

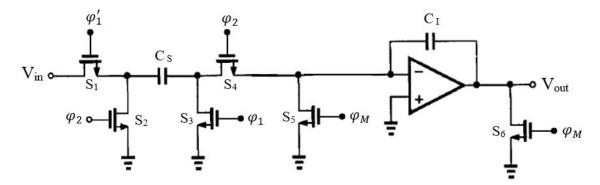

| FIGURE 5-16: (A) PARASITIC-INSENSITIVE INTEGRATOR (B) CIRCUIT OF (A) IN SAMPLING MODE, (C) CIRCUIT OF (A) | ) IN INTEGRATION |

| MODE [80]                                                                                                 | 99               |

| FIGURE 5-17: TIMING DIAGRAM OF THE PARASITIC-INSENSITIVE INTEGRATOR                                       | 100              |

| FIGURE 5-18: EQUIVALENT CIRCUIT OF THE PARASITIC-INSENSITIVE INTEGRATOR IN INTEGRATION MODE               | 103              |

| FIGURE 5-19: DIFFERENTIAL AMPLIFIER WITH SINGLE-ENDED OUTPUT [80]                                         | 105              |

| FIGURE 5-20: SLEWING IN THE OP-AMP [80]                                                                   | 105              |

| FIGURE 5-21: PARASITIC-INSENSITIVE INTEGRATOR WITH RESET SWITCHES                                 | 108 |

|---------------------------------------------------------------------------------------------------|-----|

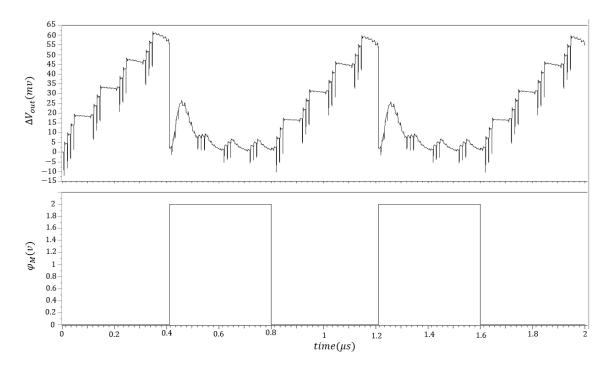

| FIGURE 5-22: OUTPUT OF A DIFFERENTIAL PARASITIC-INSENSITIVE INTEGRATOR SIMULATED IN SPICE         | 110 |

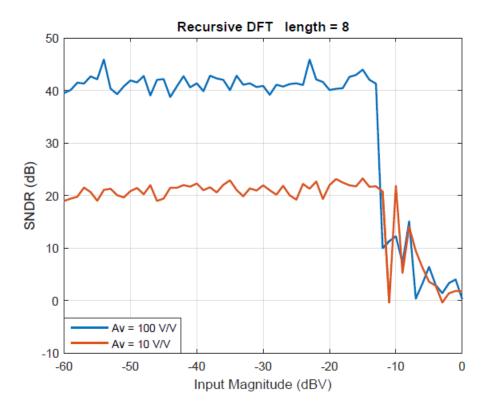

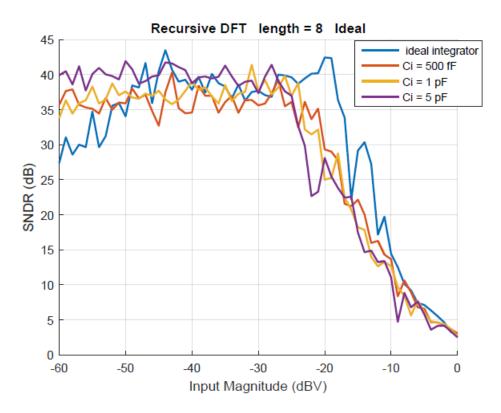

| FIGURE 5-23: THE SNDR CURVES OF REAL-TIME RECURSIVE DFT PROCESSORS WITH IDEAL DEVICES             | 111 |

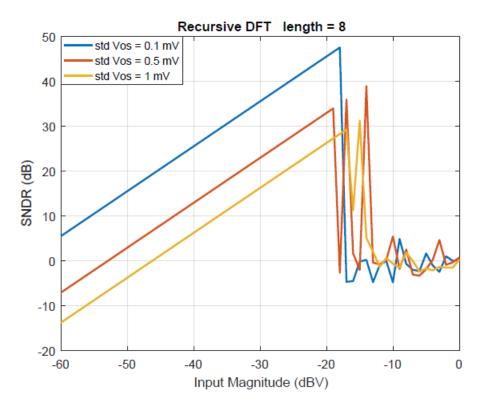

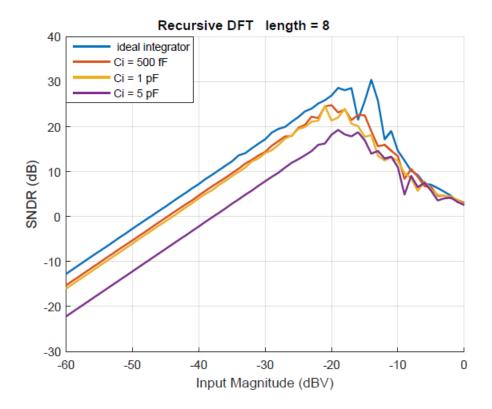

| FIGURE 5-24: SNDR CURVES OF REAL-TIME RECURSIVE DFT PROCESSORS IN THE PRESENCE OF DEVICE MISMATCH | 112 |

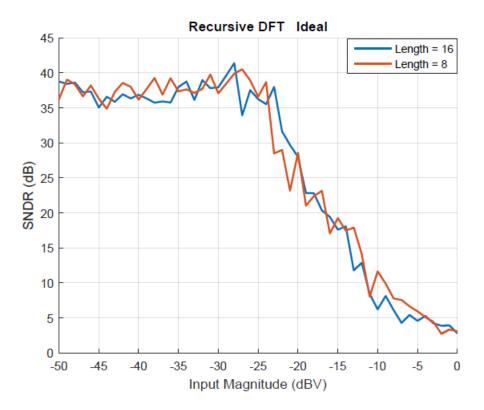

| FIGURE 5-25: SNDR CURVES OF REAL-TIME RECURSIVE DFT PROCESSORS WITH DIFFERENT TRANSFORM LENGTHS   | 113 |

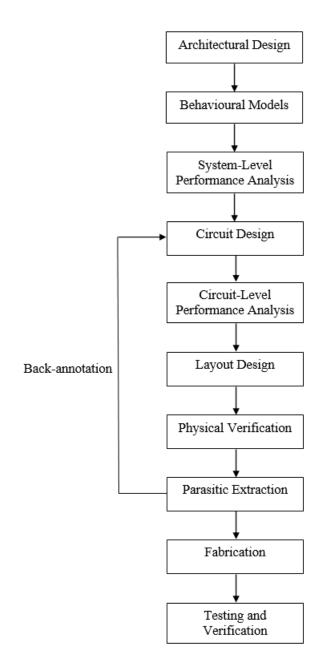

| FIGURE 5-26: STEPS IN THE INTEGRATED CIRCUIT DESIGN FLOW [115]                                    | 114 |

| FIGURE 6-1: EQUAL DRAWN AREA DEVICES (A) SHORT CHANNEL (B) NARROW CHANNEL                         | 119 |

| Figure 6-2: Modeling VTH variations using a DC voltage source in series with the MOS gate         |     |

| TERMINAL                                                                                          | 123 |

| FIGURE 6-3: MISMATCH ANALYSIS RESULTS OF THE REAL-TIME RECURSIVE DFT PROCESSOR OF LENGTH 8        | 124 |

| FIGURE 6-4: DYNAMIC RANGE HISTOGRAM OF THE 8-POINT DFT PROCESSOR FOR BPSK MODULATED SIGNAL        | 125 |

| FIGURE 6-5: DYNAMIC RANGE HISTOGRAM OF THE 16-POINT DFT PROCESSOR FOR BPSK MODULATED SIGNAL       | 126 |

| FIGURE 6-6: DYNAMIC RANGE HISTOGRAM OF THE 8-POINT DFT PROCESSOR FOR QPSK MODULATED SIGNAL        | 126 |

| FIGURE 6-7: THE SNDR CURVES OF 8-POINT RECURSIVE DFT PROCESSORS WITH IDEAL DEVICES                | 129 |

|---------------------------------------------------------------------------------------------------|-----|

| FIGURE 6-8: THE SNDR CURVES OF 8-POINT RECURSIVE DFT PROCESSORS                                   | 130 |

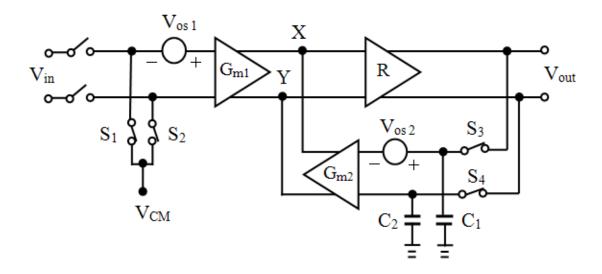

| FIGURE 6-9: OFFSET CANCELLATION BY AN AUXILIARY TRANSCONDUCTANCE IN A NEGATIVE FEEDBACK LOOP [80] | 131 |

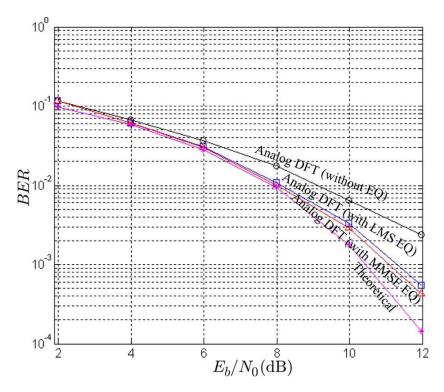

| FIGURE 6-10: PERFORMANCE COMPARISON OF A 4-PONIT ANALOGUE DFT IMPLEMENTED ON A FPAA [93]          | 133 |

### **LIST OF ABBREVIATIONS**

| 1G         | First Generation                               |

|------------|------------------------------------------------|

| 2G         | Second Generation                              |

| <b>3</b> G | Third Generation                               |

| 4 <b>G</b> | Fourth Generation                              |

| ACI        | Adjacent Channel Interference                  |

| ADC        | Analogue to Digital Converter                  |

| AGC        | Automatic Gain Control                         |

| AWGN       | Additive White Gaussian Noise                  |

| BER        | Bit Error Ratio                                |

| BJT        | Bipolar Junction Transistor                    |

| BPSK       | Binary Phase-Shift Keying                      |

| BSIM       | Berkeley Short-Channel IGFET Model             |

| CCDF       | Complementary Cumulative Distribution Function |

| CLT        | Central Limit Theorem                          |

| СМ         | Common Mode                                    |

| CMFB       | Common Mode Feedback                           |

| CMOS       | Complementary Metal-Oxide Semiconductor        |

|            | Complementary Metal-Oxide Semiconductor        |

| DAC             | Digital to Analogue Converter                     |

|-----------------|---------------------------------------------------|

| dB              | decibel                                           |

| DC              | Direct Current                                    |

| DFT             | Discrete Fourier Transform                        |

| DIF             | Decimation In Frequency                           |

| DIT             | Decimation In Time                                |

| DSP             | Digital Signal Processor                          |

| EVM             | Error Vector Magnitude                            |

| FDM             | Frequency Division Multiplexing                   |

| FEC             | Forward Error Correction                          |

| FFT             | Fast Fourier Transform                            |

| FIR             | Finite Impulse Response                           |

| FPAA            | Field Programmable Analogue Array                 |

| ICI             | Intercarrier Interference                         |

| IDFT            | Inverse Discrete Fourier Transform                |

| IEEE            | Institute of Electrical and Electronics Engineers |

| IF              | Intermediate Frequency                            |

| IFFT            | Inverse Fast Fourier Transform                    |

| iid             | independent and identically distributed           |

| IP <sub>2</sub> | Second Intercept Point                            |

| ISI    | Intersymbol Interference                      |

|--------|-----------------------------------------------|

| KCL    | Kirchhoff's Current Law                       |

| KVL    | Kirchhoff's Voltage Law                       |

| LDPC   | Low-Density Parity-Check                      |

| LLN    | Low of Large Numbers                          |

| LMS    | Least Mean Square                             |

| LPF    | Low Pass Filter                               |

| LSB    | Least Significant Bit                         |

| LTE    | Long Term Evolution                           |

| MMSE   | Minimum Mean Square Error                     |

| NMOS   | N-channel Metal-Oxide Semiconductor           |

| OFDM   | Orthogonal Frequency-Division Multiplexing    |

| OFDMA  | Orthogonal Frequency Division Multiple Access |

| Op-amp | Operational amplifier                         |

| PAPR   | Peak to Average Power Ratio                   |

| РСМ    | Pulse Code Modulation                         |

| PDF    | Probability Density Function                  |

| PDK    | Process Design Kit                            |

| РНҮ    | Physical layer                                |

| PMOS   | P-channel Metal-Oxide Semiconductor           |

| QAM    | Quadrature Amplitude Modulation                        |

|--------|--------------------------------------------------------|

| QPSK   | Quadrature Phase-Shift Keying                          |

| RF     | Radio Frequency                                        |

| RMS    | Root Mean Square                                       |

| SC     | Switched Capacitor                                     |

| SDR    | Software Defined Radio                                 |

| SNDR   | Signal to Noise and Distortion Ratio                   |

| SNR    | Signal to Noise Ratio                                  |

| SOFDMA | Scalable Orthogonal Frequency Division Multiple Access |

| SPICE  | Simulation Program with Integrated Circuit Emphasis    |

| SR     | Slew Rate                                              |

| TPC    | Turbo Product Code                                     |

| UWB    | Ultra-Wideband                                         |

| VLSI   | Very Large Scale Integration                           |

| VoIP   | Voice over Internet Protocol                           |

| WiFi   | Wireless Fidelity                                      |

| WiMAX  | Worldwide Interoperability for Microwave Access        |

| WLAN   | Wireless Local Area Network                            |

| WMAN   | Wireless Metropolitan Area Network                     |

# Chapter 1

### INTRODUCTION

In this chapter, a historical perspective on the development of communication systems is provided. The gaps in the previous research are discussed in the statement of the problem. Objectives and significance of the study are explained to clarify how this work will contribute to knowledge. Finally, an outline of the thesis structure is provided.

### 1.1 Evolution of Communication Systems

The proposal to use electricity in communication is dated back to the late 18<sup>th</sup> century. In 1795, Francisco Salvá Campillo proposed an electrical telegraph as an alternative to optical ones [2]. In 1809, an electrochemical telegraph was designed by Samuel Thomas von Sömmerring [3]. The first electrical telegraph was built by Francis Ronalds in 1816 [4]. The costs of using one wire for each letter of the alphabet in early designs of telegraph were prohibitive. Therefore, in 1835, Pavel L'vovitch Shilling reduced the number of wires by developing the first binary code for the telegraph [5]. In 1838, Samuel Morse and Alfred Vail invented a single-wire telegraph and the Morse code. The Morse/Vail telegraph became the forerunner of digital communication [6]. The idea of speaking telegraph was initially proposed by Innocenzo Manzetti in 1844 [7]. Later, in 1854, Charles Bourseul wrote a memorandum on the electrical transmission of speech [8]. In 1871, Antonio Meucci filed a patent caveat for his telephone invention (telettrofono). Meucci filed a patent caveat because he could not afford the \$250 fee necessary to file a patent application [9]. In 1876, Elisha Gray filed a patent caveat for a telephone on the very same day that Alexander Graham Bell filed a patent application for a telephone. After a month, Bell's telephone patent issued and telephone became the forerunner of analogue communication [10-12].

Digital communication remained attractive owing to the contributions of Guglielmo Marconi and Karl Ferdinand Braun to the invention of wireless telegraphy in 1896 [13, 14]. In 1906, Reginald Fessenden invented the heterodyne transceiver which used the Amplitude Modulation (AM) to transmit an audio signal via a radio carrier wave [15]. In 1912, the significant role of Marconi's wireless telegraphy in rescuing the survivors of Titanic proved its vital importance for marine communication [16]. In 1918, Edwin H. Armstrong invented the superheterodyne receiver which converted the frequency of received signal to a fixed Intermediate Frequency (IF). Comparing to the heterodyne receiver, the superheterodyne receiver provided better selectivity and sensitivity. Later, in 1933, Armstrong demonstrated the Frequency Modulation (FM) which provided better sound quality and fidelity than AM [17].

In 1937, Alec Harley Reeves invented the Pulse Code Modulation (PCM) to enhance the noise immunity of audio transmission over long distances [18]. In fact, Reeves invented the first all-electronic Analogue to Digital Converters (ADC) and Digital to Analogue Converter (DAC) [19]. Another landmark of 1937 was Claude Shannon's master's thesis. Shannon proved that Boolean algebra could optimise the design of electromechanical relays in telephone routing switches. Shannon's work on the electrical implementation of Boolean functions became the foundation of digital circuit design [20]. In 1948, Shannon laid the theoretical foundations of digital communications in his paper "A Mathematical Theory of Communication" [21]. In 1947, Walter H. Brattain, John Bardeen, and William Shockley invented the transistor at Bell Laboratories [22]. In 1958, Jack Kilby realized the first germanium Integrated Circuit (IC) [23]. Few months later, Robert Noyce produced the first silicon IC [24]. These landmark innovations changed the nature of the communication systems in the second half of the 20<sup>th</sup> century [6].

In 1965, James Cooley and John Tukey developed the Fast Fourier transform (FFT) algorithm for efficient computation of the Discrete Fourier Transform (DFT) [25]. In 1966, Robert W. Chang invented the Orthogonal Frequency Division Multiplexing (OFDM) for simultaneous transmission of data on multiple channels [26, 27]. In 1971, Weinstein and Ebert suggested to use the FFT for realization of OFDM modulator and demodulator [28].

In 1973, the first handheld mobile cell phone was invented by Martin Cooper (Figure 1.1) and his fellow teammates at Motorola [29]. 10 years after Cooper's invention, the first-generation of mobile communication (1G) systems was launched. 1G was based on analogue communication [30]. The first commercially available mobile phone (DynaTAC 8000x) resembled a brick in terms of size and weight. Besides, its battery only lasted 30 minutes after 10 hours of recharge [31].

The second-generation of mobile communication (2G) systems emerged in 1991. 2G was based on digital communication. While 1G systems had no security, 2G systems provided security by encrypting the digital signals. Moreover, 2G digital systems made error detection and error correction possible by encoding and decoding. Since error correction minimises the effect of interference, 2G systems achieved better communication quality than 1G systems. Furthermore, comparing to 1G systems, 2G systems provided higher spectrum efficiency by compressing the digital data. Additionally, 2G systems applied multiple access techniques which allow multiple users to share the frequency band. Thereby, 2G systems achieved higher capacity than 1G systems. Comparing to 1G analogue systems, 2G digital systems had longer battery life and cheaper equipment. These advantages led to the prevalence of the digital communication standards [30].

Figure 1-1: Martin Cooper holds the DynaTAC 8000x phone and his current mobile phone during the Prince of Asturias Awards ceremony in 2009 [32].

The proliferation of mobile phone users led to the growing demand for mobile internet access. In response to this demand, the third-generation of mobile communication (3G) systems emerged in 2001. 3G systems use packet switching for data transmission and circuit switching for voice calls [17, 30].

3G systems can not satisfy the growing demand for streaming media. Hence, the fourthgeneration of mobile communication (4G) systems emerged in 2011. 4G systems provide higher data rate than the existing 3G systems. Moreover, 4G networks use packet switching with Internet Protocol (IP) for data and voice transmission. The circuit switching in 3G networks is replaced by the Voice over Internet Protocol (VoIP) in 4G networks. Worldwide Interoperability for Microwave Access (WiMAX) and Long Term Evolution (LTE) are the two competing technologies for 4G systems [17, 30]. Table 1-1 shows the landmark innovations in the history of analogue and digital communication systems. The earliest form of electronic communication system (telegraph) was digital. However, digital signals could not convey the continuous waves of speech. Conversion from digital to analogue made the speech communication possible. For more than a century (1876-1991), analogue communication systems had been used to transmit audio signals. Laying the theoretical and practical foundations of modern digital communications took more than 50 years (1937-1991). Comparing to analogue systems, modern digital communication systems provide higher security, better communication quality, higher spectrum efficiency, and higher capacity.

Year Innovation 1838 Telegraph Telephone 1876 1896 Wireless telegraphy Heterodyne transceiver, AM broadcasting 1906 Superheterodyne receiver 1918 1933 FM broadcasting 1937 PCM 1937 Electrical implementation of Boolean functions 1947 Transistor 1948 Mathematical Theory of Communication 1958 **Integrated Circuit** FFT algorithm 1965 **OFDM** 1966 1983 1G1991 2G2001 **3G** 2011 4GFoundation of modern Digital systems Digital Analogue Foundation of modern Analogue and Digital systems

Table 1-1: Evolution of Communication Systems

#### 1.2 Statement of the Problem

The previous section revealed that a new generation of mobile communication standard has emerged approximately every 10 years. Upgrading the technology of mobile networks in all areas takes few years. Hence, mobile phones should support the previous communication standards as well as the latest standards. Moreover, since WiFi [33] provides higher data rate than WiMAX [34], in areas where both WiFi and WiMAX are available (e.g. university campus, office, home, hotel) it is preferable to use WiFi [17].

The initial approach to realise a multi-standard mobile phone was to use multiple transceivers (Figure 1.2(a)) in parallel. However, as the number of communication standards increases, size and cost of the mobile handset increases [35, 36]. To resolve this issue, Joseph Mitola proposed the concept of Software Defined Radio (SDR) according to which a single transceiver can support multiple communication standards if it is reconfigurable by software [37]. Mitola suggested that the SDR can be achieved by replacing the analogue signal processing stages of the transceiver (i.e. analogue front-end) with a Digital Signal Processor (DSP) (Figure 1.2(b)) [37]. Moving the ADC and the DSP closer to the antenna means that the signal should be sampled and processed at the Radio Frequency (RF). Frequency bands that are allocated to the mobile communication standards and WiFi are between 800 MHz to 5.5 GHz. To digitize any signal from 800 MHz to 5.5 GHz, a 12 bit, 11 GS/s ADC is required. Such a demanding ADC is unrealizable with the current technology [38]. Also, since the progress of ADC dynamic range and conversion speed are slower than the Moore's law, the required ADC will remain infeasible in the foreseeable future [39]. Even if a 12 bit, 11 GS/s ADC were feasible, its power dissipation would be hundreds of watts [38]. Moreover, in the SDR receiver, the digital front-end performs the downconversion. The digital mixer requires four real multiplications per complex signal sample. Considering the sample rate of 11 GS/s, the DSP must perform 44 billion multiplications per second. Considering the power dissipation of the digital mixer, implementation of the downconversion on the DSP is not sensible [40]. Hence, the SDR that was envisaged by Mitola has remained elusive [38].

Figure 1-2: Analogue and Digital signal processing sections in (a) the classical OFDM receiver (b) the Software Defined Radio receiver (c) the OFDM receiver with an analogue FFT

Demanding ADC is also a serious impediment to the Ultra-Wideband (UWB) OFDM wireless transceivers [41]. In an effort to relax the ADC requirements in the UWB OFDM transceivers, an analogue FFT processor was proposed (Figure 1.2(c)) [41]. Transferring the FFT processor from the digital back-end to the analogue front-end reduces the bit depth requirement of the ADC. Thereby, the power consumption of the ADC reduces. Moreover, the analogue FFT processor consumes significantly less power than the digital FFT [41]. However, the analogue FFT processor is not reconfigurable because it is hardwired. Hence, the analogue FFT processor is not suitable for multi-standard transceivers.

#### 1.3 Dissertation Objectives

After reviewing the requirements of the modern mobile handheld devices and impediments to realization of the SDR, it is clear that an alternative architecture for multi-standard transceivers must be explored. For OFDM-based transceivers, the analogue FFT processor is an attractive alternative to the power hungry digital FFT processor. Multiple OFDM-based transceivers can be integrated by a variable-length DFT processor. To consume the power efficiently, the power consumption of the variable-length DFT processor should be scalable with the length of the transform. In this thesis, a power-scalable variable-length analogue DFT processor that meets the specifications of WiFi and WiMAX standards is proposed.

The previous works on the analogue DFT processor merely focused on the circuit design methods and used the conventional architectures that were originally designed for the digital DFT processor or the discrete-time filters. Hence, a novel architecture that is designed based on the characteristics of the analogue signal processing domain is required. The main concern is the arithmetic precision of the analogue DFT processor. Therefore, performance of the proposed system should be analysed at various stages of the design process by statistical modelling of the mismatch.

### 1.4 Significance of the Research

Digital signal processing or analogue signal processing; that has been the question throughout the history of communication systems. Finding the answer to this question led to the invention of the telephone, the advent of 2G systems, and changing Mitola's paradigm of SDR [38]. A power-scalable variable-length analogue DFT processor can be another breakthrough in transceivers. Sharing the DFT processor between multiple transceivers and implementing it with analogue circuits can significantly reduce the hardware cost.

Moreover, a power-scalable analogue DFT processor can be the most power-efficient DFT processor. Hence, this research may lead to a new generation of mobile phones that are smaller, cheaper, and have longer battery life.

#### 1.5 Thesis Outline

In this chapter, the evolution of communication systems was overviewed. Also, limitations of previous research on the SDR and the analogue FFT processor were discussed. Additionally, objectives and significance of the research were explained.

Chapter 2 provides the background knowledge on the OFDM technology and the OFDM-based standards. State-of-the-art FFT processors are reviewed. Also, a comparison between the analogue and digital signal processing is provided to elaborate the trade-offs in each approach.

In Chapter 3, the proposed architecture for the power-scalable variable-length analogue DFT processor is explained. Advantages and novelty of the proposed architecture are revealed by making comparisons between the proposed architecture and previous Fourier transform architectures.

In Chapter 4, performance requirements of the analogue DFT processor are derived. The behavioural models of the processor building blocks are explained. System simulations based on the behavioural models are performed to determine the design specifications of circuits. Yield prediction based on the Monte Carlo method is discussed. Moreover, performance of the proposed architecture and the FFT architecture are compared together.

Chapter 5 reviews various design approaches for the building blocks of the analogue DFT processor. Circuits that can provide the required flexibility for the power-scalable variable-length DFT processor are selected. Selected circuits are designed in 180 nm CMOS technology. Speed-power-accuracy trade-offs in circuits with ideal devices are discussed.

Chapter 6 reviews the mismatch models available in the open literature. This chapter also explains the design trade-offs that impose limitations on the performance of analogue signal processors. The effect of technology scaling on mismatch is also discussed. The impact of device mismatch on the performance of the circuit is analysed. Results of this analysis are compared with previous work. Finally, techniques that can mitigate the effect of device mismatch are mentioned.

Chapter 7 presents the concluding remarks and the original contributions of this study. This chapter also provides recommendations for future research.

## Chapter 2 Background Study and Literature Review

In this chapter, the OFDM technology and the OFDM-based standards are overviewed. Also, achievements of the latest studies on the FFT processors are mentioned. A comparison between the analogue and digital circuits is provided. Furthermore, the existing architectures for the analogue Fourier transform processor are explained.

### 2.1 Fundamentals of OFDM

Orthogonal Frequency-Division Multiplexing (OFDM) and its variants are the predominant technology in the fourth-generation of mobile communication systems (4G). OFDM is an advanced form of the Frequency Division Multiplexing (FDM). FDM is a technique that facilitates the simultaneous transmission of multiple signals on a single medium by dividing the channel bandwidth into multiple subchannels (Figure 2.1). FDM is an effective technique to combat Intersymbol Interference (ISI) and multipath fading in wireless communications. However, since FDM prevents interference between subchannels by means of guard bands, it does not use the channel bandwidth efficiently [42].

Power

$$f_0$$

Guard band  $f_1$  Guard band  $f_2$   $f_{N-1}$  Frequency

Figure 2-1: the spectrum of the FDM signal consisting of nonoverlapping subchannels [43]

In OFDM a broad frequency spectrum is divided into multiple orthogonal narrowband subchannels by the Discrete Fourier Transform (DFT). OFDM modulation and demodulation are performed by the Inverse Discrete Fourier Transform (IDFT) and DFT, respectively. Both DFT and IDFT multiply discrete samples of signal by complex exponentials [1, 44].

*IDFT*:

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) e^{j2\pi \frac{kn}{N}}, \quad n = 0, 1, ..., N-1$$

(2.1)

DFT:

$$X(k) = \sum_{n=0}^{N-1} x(n) e^{-j2\pi \frac{kn}{N}}, \quad k = 0, 1, ..., N-1$$

(2.2)

In the above equations, x(n) and X(k) represent discrete samples of the modulated and demodulated signals, respectively. Hence, elements of the sequence  $\left\{e^{j2\pi(kn/N)}\right\}_{k=0}^{N-1}$  are the subcarriers of the x(n). The orthogonality of subcarriers to each other is proven by multiplying both sides of the equation (2.1) by  $e^{-j2\pi(mn/N)}$  and summing from n = 0 to n = N - 1 [44].

$$\sum_{n=0}^{N-1} x(n) e^{-j2\pi \frac{mn}{N}} = \sum_{n=0}^{N-1} \frac{1}{N} \sum_{k=0}^{N-1} X(k) e^{j2\pi \frac{(k-m)n}{N}}$$

(2.3)

Interchanging the order of summation on the right hand side of the equation (2.3) gives

$$\sum_{n=0}^{N-1} x(n) e^{-j2\pi \frac{mn}{N}} = \sum_{k=0}^{N-1} X(k) \left[ \frac{1}{N} \sum_{n=0}^{N-1} e^{j2\pi \frac{(k-m)n}{N}} \right]$$

(2.4)

The term inside the bracket is [44]

$$\frac{1}{N}\sum_{n=0}^{N-1}e^{j2\pi\frac{(k-m)n}{N}} = \begin{cases} 1 & k=m\\ 0 & Otherwise \end{cases}$$

(2.5)

Hence, subcarriers are orthogonal to each other. Combining equations (2.4) and (2.5) gives

$$\sum_{n=0}^{N-1} x(n) e^{-j2\pi \frac{mn}{N}} = X(m)$$

(2.6)

which is the formula for a DFT. Accordingly, applying DFT on the modulated samples demodulates them.

Elements of the sequence  $\{e^{j2\pi(kn/N)}\}_{n=0}^{N-1}$  are samples of the time-limited  $e^{j2\pi f_k t}$ which is the  $k^{th}$  subcarrier ( $f_k = k/T$  and  $-T/2 \le t \le T/2$ ). Hence, the Fourier transform of the  $k^{th}$  subcarrier is [1]

$$Y(f) = \int_{-T/2}^{T/2} e^{j2\pi f_k t} \cdot e^{-j2\pi f t} dt = \int_{-T/2}^{T/2} e^{-j2\pi (f-f_k)t} dt = \frac{\sin(\pi (f-f_k))}{\pi (f-f_k)}$$

(2.7)

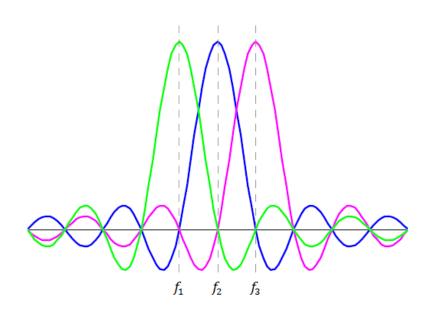

Thus,  $Y(f) = \operatorname{sinc}(f - f_k)$ . Figure 2.2 shows three subcarriers of the OFDM signal. Since subcarriers are orthogonal, zero crossings of each subcarrier falls on the peaks of other subcarriers. Therefore, not only is a guard band between adjacent subcarriers unnecessary, but also the subcarriers can overlap. Thereby, OFDM uses the channel bandwidth efficiently [45].

Figure 2-2: the spectrum of an OFDM signal consisting of three overlapping subcarriers [42]

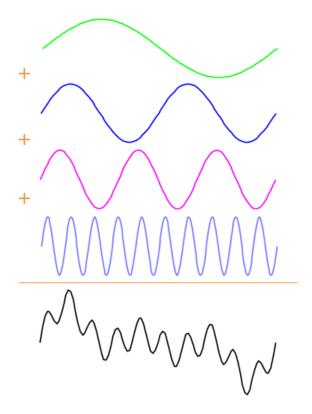

Figure 2.3 depicts the imaginary part of four subcarriers in the time domain. For a large number of modulated subcarriers ( $N \gg 1$ ) the OFDM symbol appears as Gaussian noise in the time domain [1].

Figure 2-3: summation of the OFDM subcarriers in the time domain [1]

The performance of the wireless communication systems depends on the channel characteristics. Multipath propagation results in phase shifting and fading. Thus, channel estimation is necessary to extract the original signal from the received signal. In order to estimate the channel, deterministic subcarriers called Pilot are added to the OFDM symbol [1].

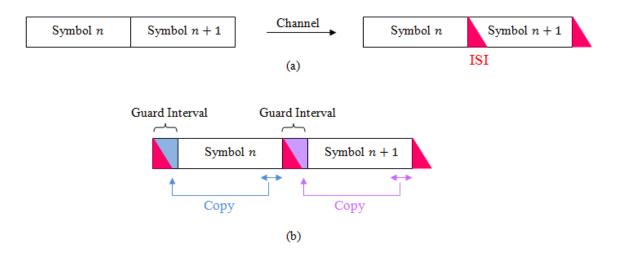

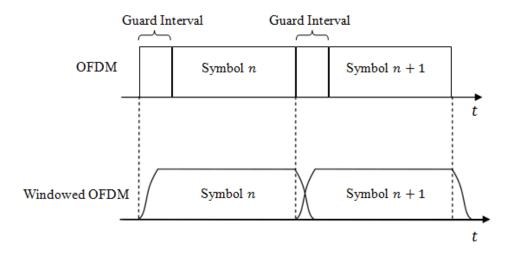

The channel delay spread in multipath propagation creates Intersymbol Interference (ISI) between successive OFDM symbols (Figure 2.4 (a)). Also, the time-dispersive channel creates Intercarrier Interference (ICI) which destroys the orthogonality between subcarriers. In order to eliminate the effect of ISI, guard intervals are added to the OFDM symbol (Figure 2.4 (b)). Subcarriers that are transmitted during the guard interval are null. The guard interval should exceed the maximum excess delay of the multipath propagation channel [46]. Since a guard interval is ineffective in cancelling ICI, the Cyclic Prefix (CP) is used instead. CP is the copy of the last part of the OFDM symbol which is prefixed to the OFDM symbol. Thus, the CP preserves the orthogonality between subcarriers by making the OFDM symbol periodic [47]. Figure 2.5 illustrates the OFDM symbol in the frequency domain.

Figure 2-4: effect of the ISI on the OFDM symbol in (a) the absence of the guard interval (b) the presence of the guard interval [1]

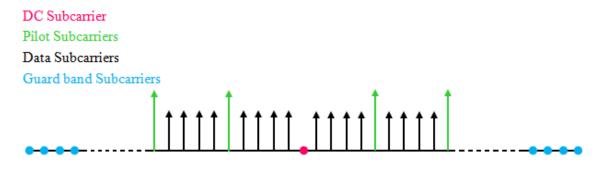

Figure 2-5: the OFDM symbol in the frequency domain [45]

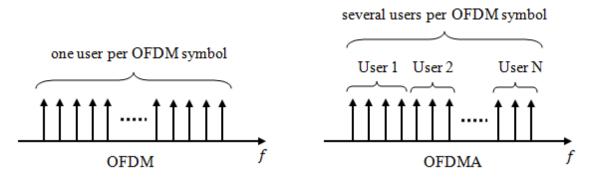

In OFDM technology, all the subcarriers of the OFDM symbol are allocated to one user. On the other hand, the Orthogonal Frequency Division Multiple Access (OFDMA) technology assigns the subcarriers of the OFDM symbol to different users (Figure 2.6). Thereby, the channel bandwidth is divided into subchannels and shared between several users. The data-rate of each user can be controlled by varying the number of subcarriers in the allocated subchannel [42].

Figure 2-6: allocation of subcarriers to users in the OFDM and OFDMA technologies [1]

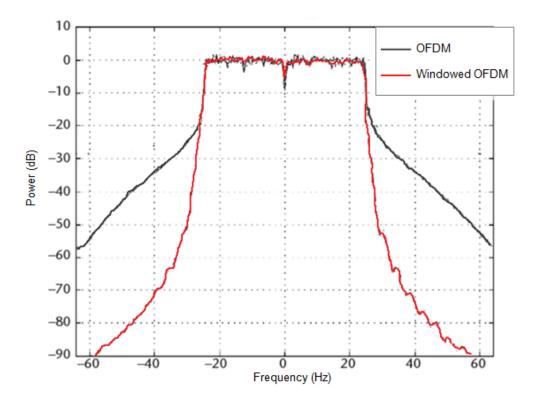

As mentioned earlier, the spectrum of the time-limited OFDM symbol is the sum of frequency shifted sinc functions. Thus, OFDM symbols produce large out-of-band power which leads to the Adjacent Channel Interference (ACI). Hence, a guard band is used to reduce the effect of ACI. Moreover, the out-of-band power is reduced by windowing the OFDM symbol [43]. Figure 2.7 and Figure 2.8 show the effect of windowing in the time domain and the frequency domain, respectively.

Figure 2-7: Windowed OFDM symbol in the time domain [1]

Figure 2-8: Spectrum of the OFDM signal before and after windowing [45]

The frequency-selective channel may severely attenuate some of the subcarriers. Attenuation of the data subcarriers leads to bit errors. Hence, Forward Error Correction (FEC) coding and interleaving are essential in order to spread the coded bits over the bandwidth [45]. FEC codes that are used by most of the OFDM-based standards include Concatenated code, Convolutional code, Block code, Turbo code, Low-Density Parity-Check (LDPC) code, and Reed-Solomon code [43].

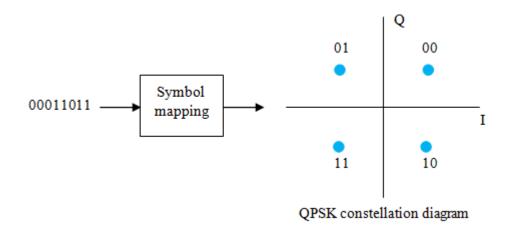

After the channel coding, the OFDM transmitter maps the bit stream on the constellation points. Thereby, each symbol is represented by a magnitude and a phase. Symbol mapping is performed based on the Quadrature Amplitude Modulation (QAM), the Binary Phase-Shift Keying (BPSK), or the Quadrature Phase-Shift Keying (QPSK) (Figure 2.9) [1].

Figure 2-9: Symbol mapping based on the QPSK modulation [1]

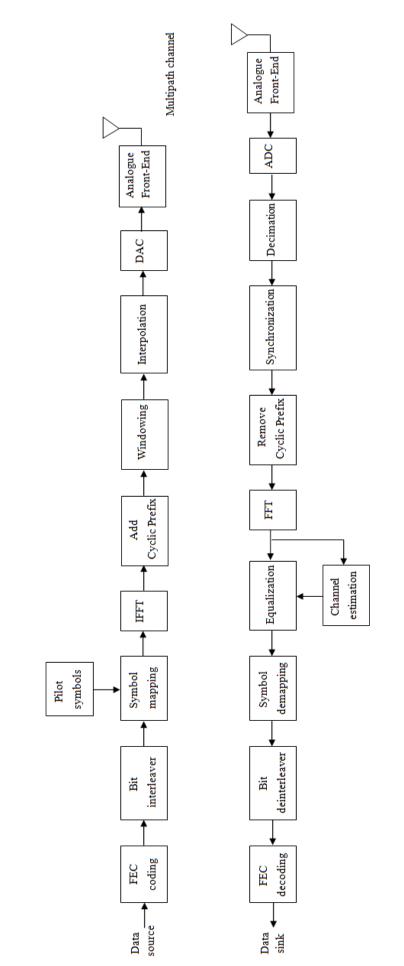

Figure 2.10 shows the block diagrams of the classical OFDM transmitter and receiver. The Fast Fourier Transform (FFT) and the Inverse Fast Fourier Transform (IFFT) processors are used to compute DFT and IDFT efficiently [1, 43]. In Figure 2.10, DAC and ADC denote the Digital to Analogue Converter and the Analogue to Digital Converter, respectively.

#### 2.2 WiFi and WiMAX Physical Layer Overview

WiFi (IEEE 802.11a/g) and WiMAX (IEEE 802.16e) are the OFDM-based standards that are supported by most 4G mobile handheld devices. Hence, these standards are considered for the purpose of this study. WiFi (Wireless Fidelity) standards are set for Wireless Local Area Networks (WLANs). The difference between 802.11a and 802.11g standards is that the former operates in the 5GHz band while the later operates in the 2.4GHz band [48]. Table 2-1 summarizes the Physical layer (PHY) specifications of the 802.11a and 802.11g standards [33, 49]. WiFi optimizes the data rate and maintains the required Bit Error Rate (BER) by adapting modulation and coding rate to the radio link quality [1]. Accordingly, the maximum data rate of the 802.11a/g is 54Mbits/s which is obtained by using 64-QAM (i.e. 6 bits on each of the data subcarriers) and coding rate of 3/4:  $((6 \times 48)/4\mu s) \times 3/4 = 54M/s$ .

| Channel bandwidth (MHz)                        | 20                                         |

|------------------------------------------------|--------------------------------------------|

| IFFT/FFT size                                  | 64                                         |

| IFFT/FFT clock (MHz)                           | 20                                         |

| Subcarrier spacing (kHz)                       | 312.5 ( 20MHz / 64)                        |

| Number of data subcarriers                     | 48                                         |

| Number of pilot subcarriers                    | 4                                          |

| Number of guard band subcarriers               | 11 (6 on the left and 5 on the right)      |

| Number of DC subcarriers                       | 1                                          |

| Total number of subcarriers                    | 64                                         |

| Modulation                                     | BPSK, QPSK, 16-QAM, 64-QAM                 |

| $T_{FFT}$ : Useful symbol duration ( $\mu s$ ) | 3.2                                        |

| $T_{CP}$ : Cyclic prefix duration ( $\mu s$ )  | 0.8 (T <sub>FFT</sub> /4)                  |

| OFDM symbol duration ( $\mu s$ )               | $4 (T_{FFT} + T_{CP})$                     |

| Channel coding                                 | Convolutional coding rates : 1/2, 2/3, 3/4 |

|                                                |                                            |

WiMAX (Worldwide Interoperability for Microwave Access) standard is set for Wireless Metropolitan Area Networks (WMANs). WiMAX can operate in licensed and unlicensed bands between 2 to 11 GHz. The 802.16e standard uses the Scalable OFDMA (SOFDMA) to support different channel bandwidths. The SOFDMA keeps the carrier spacing constant by scaling the FFT size to the channel bandwidth [50]. The mobile devices that are supported by this standard can travel at tens of kilometres per hour while communicating. Table 2-2 summarizes the PHY specifications of the 802.16e is 75 bits/s.

| Channel bandwidth (MHz)                        | 1.25                                   | 5                   | 10                  | 20                  |

|------------------------------------------------|----------------------------------------|---------------------|---------------------|---------------------|

| IFFT/FFT size                                  | 128                                    | 512                 | 1024                | 2048                |

| IFFT/FFT clock (MHz)                           | 1.4                                    | 5.6                 | 11.2                | 22.4                |

| Number of subchannels                          | 2                                      | 8                   | 16                  | 32                  |

| Subcarrier spacing (kHz)                       | 10.94                                  | 10.94               | 10.94               | 10.94               |

| Number of data subcarriers                     | 72                                     | 360                 | 720                 | 1440                |

| Number of pilot subcarriers                    | 12                                     | 60                  | 120                 | 240                 |

| Number of guard band and DC subcarriers        | 44                                     | 92                  | 184                 | 368                 |

| Total number of subcarriers                    | 128                                    | 512                 | 1024                | 2048                |

| Modulation                                     | BPSK, QPSK, 16-QAM, 64-QAM             |                     |                     |                     |

| $T_{FFT}$ : Useful symbol duration ( $\mu s$ ) | 91.4                                   | 91.4                | 91.4                | 91.4                |

| $T_{CP}$ : Cyclic prefix duration ( $\mu s$ )  | T <sub>FFT</sub> /8                    | T <sub>FFT</sub> /8 | T <sub>FFT</sub> /8 | T <sub>FFT</sub> /8 |

| OFDM symbol duration ( $\mu s$ )               | 102.8                                  | 102.8               | 102.8               | 102.8               |

| Channel coding                                 | Convolutional, Optional Convolutional, |                     |                     |                     |

|                                                | Turbo, Block Turbo, LDPC               |                     |                     |                     |

Table 2-2: IEEE 802.16e PHY specifications

#### 2.3 State-of-the-Art FFT Processors

The rapid proliferation of wireless communication standards has led to the emergence of multi-standard radios. Since classical transceiver architectures are not suitable for a one-product solution, new architectures should be proposed to fulfil this demand. In view of that, digital designers developed reconfigurable FFT processors to integrate multiple OFDM-based transceivers [51-53]. Transform length and throughput of the reconfigurable FFT processor must vary for each standard. Hence, energy-efficient reconfigurable FFT processors, that scale the power consumption with the transform length and throughput, were proposed [54, 55].

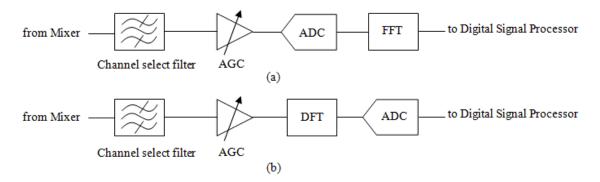

While at least 6-bit resolution is required to represent the Gaussian OFDM signal, 2 bits are sufficient to represent the QPSK symbols after the FFT demodulation. In an effort to ease the conversion burden on the ADC, FFT was applied on the discrete-time samples, prior to the ADC [41]. This approach reduces the bit depth requirement of the ADC, and consequently lowers the ADC power consumption [56]. More importantly, the analogue FFT processor consumes significantly less power than the digital FFT [57-59].

# 2.4 Comparison of Analogue and Digital signal processing

As mentioned in the previous section, latest studies show that the analogue FFT processor has significantly less power consumption than the digital FFT processor. This section provides an overview on the analogue and digital circuits to elaborate the reasons of computational efficiency in analogue circuits. In each case, the numbers of transistors that are required to implement basic operations of the Fourier transform (i.e. addition and multiplication) are given. Moreover, the compromise that is made by migrating from the digital signal processing domain to the analogue signal processing domain is mentioned.

In digital computation, variables have discrete values (i.e. 0 or 1); thus, each variable represents only one bit of information. Mathematical operations are performed by the Boolean algebraic functions (i.e. AND, OR, NOT, NAND, NOR, XOR, XNOR) [60]. Although digital computation is insensitive to device mismatch, quantization noise and round-off error degrade the accuracy of computation. Since the quantization noise and the round-off error only affect the Least Significant Bits (LSB), the degradation of accuracy is insignificant [61]. Addition of two 8-bit variables in the digital domain requires 240 transistors (i.e. 8 full adders). Also, multiplication of two 8-bit variables requires nearly 3000 transistors [62, 63].

In analogue computation, variables (i.e. current or voltage) have continuous values. Thus, each variable represents many bits of information. Mathematical operations are performed based on the physical characteristics of circuit elements (i.e. transistors, capacitors, resistors, floating gate devices) and Kirchhoff's current and voltage laws (KCL and KVL). Therefore, analogue computation is sensitive to device mismatch. In a cascade of analogue circuits, the computational errors due to mismatches accumulate. According to the KCL, a current-mode analogue adder that computes the sum of several variables can be implemented simply by connecting wires to the same node. Besides, multiplication of two variables by two-quadrant and four-quadrant analogue multipliers requires 3 and 7 transistors, respectively [62, 63].

This comparison leads to the conclusion that computation of the DFT in the analogue domain saves hardware cost and power consumption. However, these advantages are achieved at the expense of precision degradation. The following section explains the existing architectures for the analogue Fourier transform processor.

## 2.5 Analogue Fourier Transform Architectures

#### 2.5.1 The Direct Form Finite Impulse Response

The DFT of a sequence of length N is [64]

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk}, \qquad k = 0, 1, \dots, N-1$$

(2.8)

where  $W_N^{nk} = e^{-j(2\pi kn/N)} = \cos(2\pi kn/N) - j\sin(2\pi kn/N)$ . Hence, X[k] can be considered as the discrete convolution of x[n] with the impulse response

$$h(n) = \begin{cases} W_N^{nk} & n = 0, 1, \dots, N-1 \\ 0 & otherwise \end{cases}$$

(2.9)

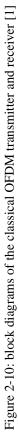

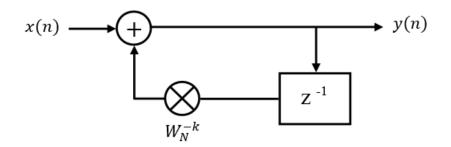

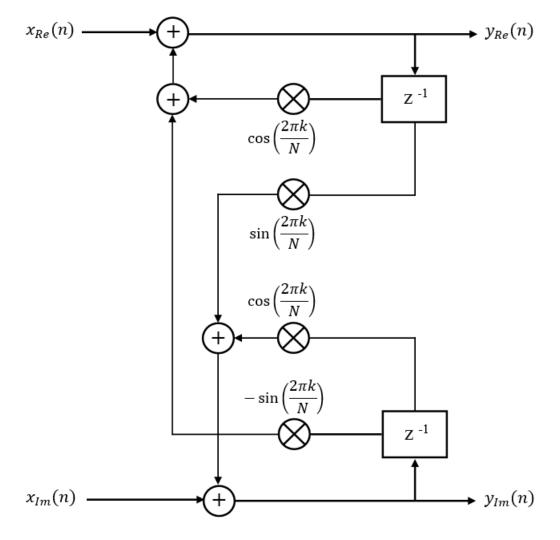

Therefore, the direct form Finite Impulse Response (FIR) architecture (Figure 2.11) can be used to implement the DFT. In this structure, the tapped delay line is made by  $z^{-1}$ blocks. At each tap, signal is weighted by the impulse response value. DFT processors that were implemented by using this architecture are available in [65, 66].

Figure 2-11: direct form realization of an FIR system [44]

Since x(n) is a complex number, expanding the complex multiplication  $x(n)W_N^{nk}$  in equation (2.8) gives

$$X_{Re}(k) = \sum_{n=0}^{N-1} x_{Re}(n) \cos\left(\frac{2\pi kn}{N}\right) + x_{Im}(n) \sin\left(\frac{2\pi kn}{N}\right), \quad k = 0, 1, \dots, N-1$$

(2.10a)

$$X_{Im}(k) = \sum_{n=0}^{N-1} x_{Im}(n) \cos\left(\frac{2\pi kn}{N}\right) - x_{Re}(n) \sin\left(\frac{2\pi kn}{N}\right), \quad k = 0, 1, \dots, N-1$$

(2.10b)

Therefore, each complex multiplication  $x(n)W_N^{nk}$  requires four real multiplications. Thus, the direct computation of X(k) requires 4N multiplications. Since X(k) must be computed for different values of k, the FIR architecture requires  $4N^2$  multipliers [44]. Accordingly, for large values of N, the area and power consumption of the FIR architecture are prohibitively large. Moreover, since mismatches in the multiplier circuits lead to erroneous calculations, the computational error in the FIR architecture has a quadratic growth.

By using the current-mode multipliers, additions can be implemented simply by connecting the outputs of two multipliers to the same node (KCL). Thus, additions do not consume area or power. More importantly, additions do not contribute to the computational error. However, since the outputs of 2N - 1 multipliers are connected together, the connection capacitance increases by increasing *N*. Hence, as *N* increases, the speed of processing decreases.

#### 2.5.2 The Fast Fourier Transform

The FFT algorithms improve the computational efficiency of the DFT by exploiting the properties of  $W_N^{nk}$  [67]

$$W_N^{r+N/2} = -W_N^r \qquad (symmetry) \qquad (2.11a)$$

$$W_N^{k(N-n)} = W_N^{n(N-k)} = W_N^{-kn}$$

(symmetry) (2.11b)

$$W_N^{k(n+N)} = W_N^{n(k+N)} = W_N^{kn} \quad \text{(periodicity)} \tag{2.11c}$$

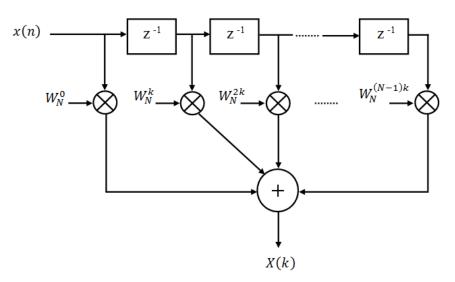

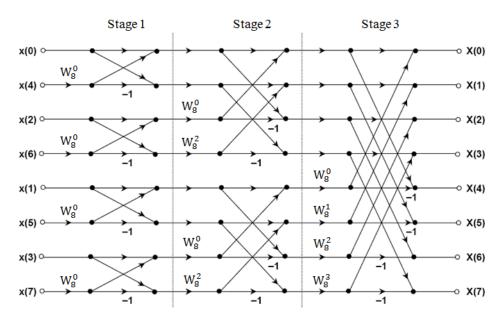

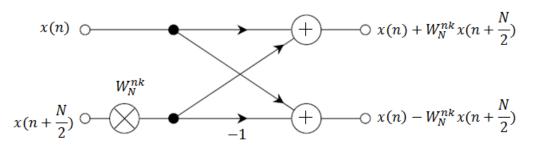

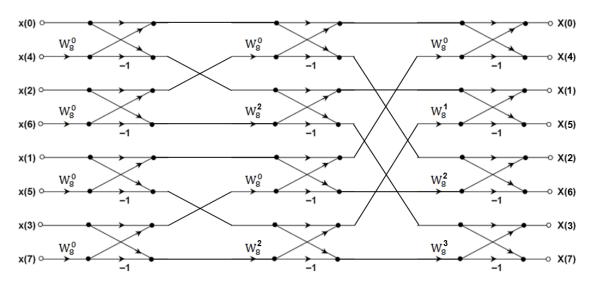

Moreover, for certain values of the product nk,  $W_N^{nk}$  is simplified (i.e.  $W_N^0 = 1$  and  $W_N^{N/4} = -j$ ). The most commonly used FFT algorithm is the Cooley-Tukey algorithm which recursively breaks down the DFT into smaller DFTs [25]. Decimation-In-Time (DIT), Decimation-In-Frequency (DIF), Mixed-Radix, and Split-Radix are some of the variants of the Cooley-Tukey algorithm. The signal flow graph of an 8-point DIT FFT is shown in Figure 2.12. The Radix-2 FFT of length 8 is obtained by decomposing the 8-point DFT into 2-point DFTs. Figure 2.13 depicts the signal flow graph of the 2-point DFT [44, 67, 68].

Figure 2-12: signal flow graph of a Radix-2 DIT FFT of length 8 [44]

Figure 2-13: signal flow graph of the 2-point DFT [44]

A Radix-2 (DIT or DIF) FFT computes the DFT with  $(N/2)\log_2 N - (N-1)$ **complex** multiplications. Thus, the number of analogue multipliers that are required to implement a Radix-2 FFT is [41]

$$M = 4N + 16\sum_{k=2}^{\log_2 N} \frac{N}{2^k} + 12\sum_{k=3}^{\log_2 N} \frac{N}{4}$$

(2.12)

Bandwidth of the FFT architecture with S stages is approximated by [69]

$$BW_{FFT} = BW_{DFT} \sqrt[2L]{2^{1/S} - 1}$$

(2.13)

where  $BW_{DFT}$  is the bandwidth of the DFT circuit that is used as the building block of the FFT architecture, and *L* is the order of the equivalent Low Pass Filter (LPF). The number of stages should be reduced to increase the bandwidth. The number of stages is obtained from [67]

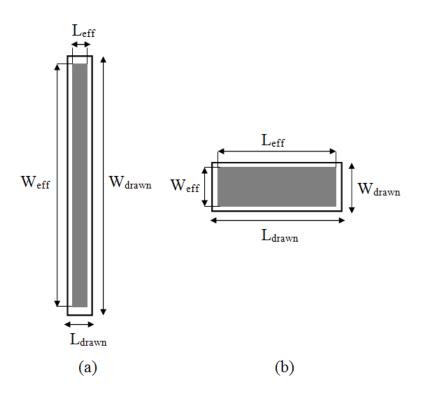

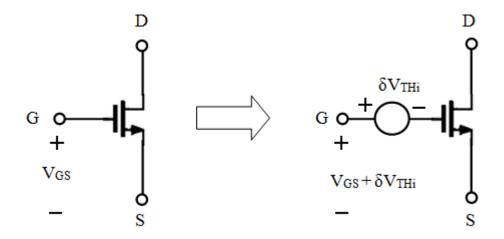

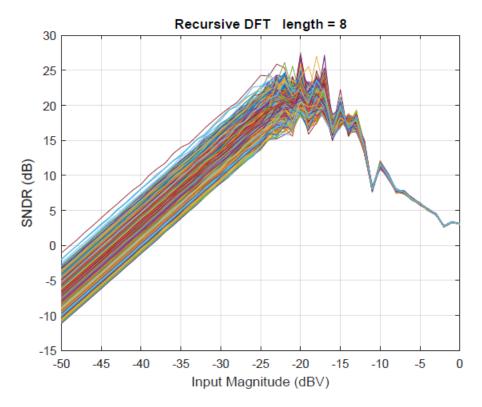

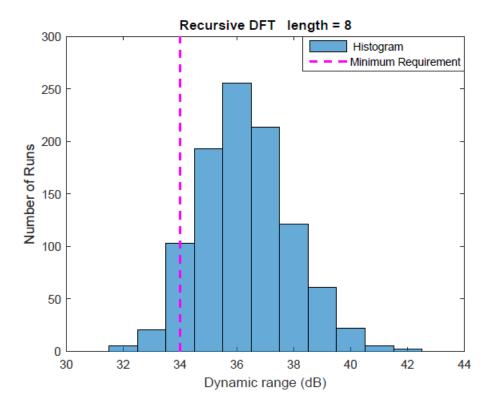

$$S = \log_R N \tag{2.14}$$