Speech Recognition in Programmable Logic

by

Stephen Jonathan Melnikoff

A thesis submitted to

The University of Birmingham for the degree of

Doctor of Philosophy

Electronic, Electrical and Computer Engineering

The University of Birmingham

November 2003

## UNIVERSITY<sup>OF</sup> BIRMINGHAM

# **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

## The University of Birmingham

Electronic, Electrical and Computer Engineering

## **Degree of Doctor of Philosophy**

in Electronic and Electrical Engineering

# **Speech Recognition in Programmable Logic**

Stephen Jonathan Melnikoff Beng(Hons) MSc MIEE

#### **PhD Thesis**

Revision 75 — 27<sup>th</sup> October 2003

Final Edition (Electronic Version)

E-mail: s.j.melnikoff@iee.org

University No.: 311254

Supervisor: Dr Steven F Quigley

© 2003 Stephen Jonathan Melnikoff

## **Abstract**

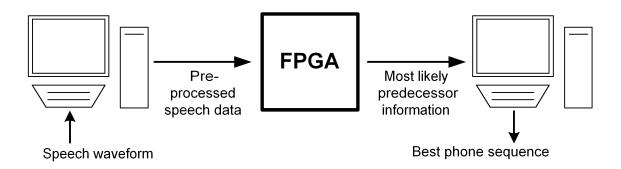

Speech recognition is a computationally demanding task, especially the decoding part, which converts pre-processed speech data into words or sub-word units, and which incorporates Viterbi decoding and Gaussian distribution calculations.

In this thesis, this part of the recognition process is implemented in programmable logic, specifically, on a field-programmable gate array (FPGA).

Relevant background material about speech recognition is presented, along with a critical review of previous hardware implementations. Designs for a decoder suitable for implementation in hardware are then described. These include details of how multiple speech files can be processed in parallel, and an original implementation of an algorithm for summing Gaussian mixture components in the log domain. These designs are then implemented on an FPGA.

An assessment is made as to how appropriate it is to use hardware for speech recognition. It is concluded that while certain parts of the recognition algorithm are not well suited to this medium, much of it is, and so an efficient implementation is possible.

Also presented is an original analysis of the requirements of speech recognition for hardware and software, which relates the parameters that dictate the complexity of the system to processing speed and bandwidth.

The FPGA implementations are compared to equivalent software, written for that purpose. For a contemporary FPGA and processor, the FPGA outperforms the software by an order of magnitude.

For M&D

ls

PhD...Doctor of Philosophy, earned by several years' postgraduate study regardless of subject title, perhaps because at the end of ten years in higher education, you have to be philosophical about the value of it all.

- Robert Ainsley, Bluff Your Way at University

# Acknowledgments

#### I would like to thank:

- My friends, for making these five years in Brum such an enjoyable experience;

- My parents, for their unwavering support;

- Jonathan Bilmen, BMedSci, PhD, for his friendship, ceaseless exploits, and for learning far more about speech recognition and programmable logic than any biochemist/medic ever should;

- And finally: Dr Steven Quigley, supervisor extraordinaire, for his assistance, advice, good humour in the face of adversity (e.g. undergraduates, impending deadlines, paperwork), and startlingly brightly coloured ("tasteful") shirts.

<sup>&</sup>lt;sup>1</sup>Source: Dr S Quigley

# Contents

| 1 Introduction |      |                                  | 1        |

|----------------|------|----------------------------------|----------|

|                | 1.1  | Aims and objectives              | 2        |

|                | 1.2  | Speech recognition               | 2        |

|                |      | 1.2.1 Overview                   | 2        |

|                |      | 1.2.2 Speech pre-processing      | 3        |

|                |      | 1.2.3 HTK                        | 5        |

|                | 1.3  | Field-programmable gate arrays   | 6        |

|                | 1.4  | Motivation                       | 9        |

|                | 1.5  | Contribution                     | 11       |

|                | 1.6  | Structure of the thesis          | 12       |

| 2              | Spec | ech recognition theory           | 14       |

|                | 2.1  | The speech recognition problem   | 14       |

|                | 2.2  | Hidden Markov models             | 16       |

|                | 2.3  | Viterbi decoding                 | 18       |

|                |      | 2.3.1 Decoding                   | 18       |

|                |      |                                  |          |

|                |      |                                  | 19       |

|                |      | 2.3.2 Termination & backtracking | 19<br>20 |

|                |      | 2.3.2 Termination & backtracking |          |

|                | 2.4  | 2.3.2 Termination & backtracking | 20       |

|   | 2.5  | Discrete HMMs                                  | 23 |

|---|------|------------------------------------------------|----|

|   | 2.6  | Continuous HMMs                                | 24 |

|   | 2.7  | Gaussian mixture summation (log-add algorithm) | 26 |

|   | 2.8  | Duration modelling                             | 27 |

|   | 2.9  | Summary                                        | 28 |

| 3 | Spec | ech recognition in hardware                    | 29 |

|   | 3.1  | Accuracy measures                              | 30 |

|   | 3.2  | Parallel systems                               | 31 |

|   |      | 3.2.1 Custom ICs                               | 31 |

|   |      | 3.2.2 SIMD arrays                              | 32 |

|   |      | 3.2.3 MIMD arrays                              | 35 |

|   |      | 3.2.4 Associative string processors            | 36 |

|   | 3.3  | Serial systems                                 | 37 |

|   | 3.4  | FPGAs                                          | 38 |

|   | 3.5  | Commercial products                            | 40 |

|   | 3.6  | Alternative recognition methods                | 41 |

|   | 3.7  | Gaussian mixture summation                     | 42 |

|   | 3.8  | Other hardware implementations                 | 43 |

|   |      | 3.8.1 Convolutional decoding                   | 43 |

|   |      | 3.8.2 Traceback                                | 45 |

|   |      | 3.8.3 Training                                 | 45 |

|   |      | 3.8.4 Trees                                    | 46 |

|   | 3.9  | Summary                                        | 46 |

| 4 | Syst | e <mark>m design</mark>                        | 47 |

|   | 4.1  | Structure                                      | 48 |

| 5 | Imp | lementa  | tion                          | 69 |

|---|-----|----------|-------------------------------|----|

|   | 4.9 | Summa    | ury                           | 67 |

|   |     | 4.8.3    | Non-emitting states           | 67 |

|   |     | 4.8.2    | Pruning                       | 66 |

|   |     | 4.8.1    | Control                       | 65 |

|   | 4.8 | Further  | design issues                 | 65 |

|   | 4.7 | Full lar | nguage model                  | 63 |

|   |     | 4.6.2    | Serial architecture           | 63 |

|   |     | 4.6.1    | Parallel architecture         | 61 |

|   | 4.6 | Duratio  | on modelling                  | 61 |

|   |     | 4.5.2    | Data analysis & design        | 59 |

|   |     | 4.5.1    | Top-level structure           | 58 |

|   | 4.5 | Gaussia  | an mixture summation          | 58 |

|   |     | 4.4.3    | Data storage                  | 57 |

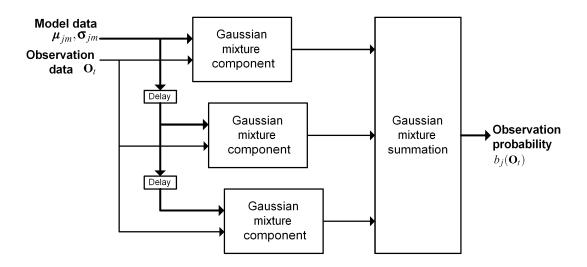

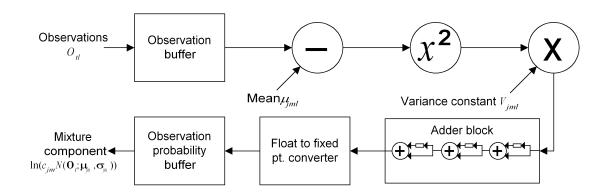

|   |     | 4.4.2    | Gaussian mixture components   | 55 |

|   |     | 4.4.1    | Parallelism                   | 54 |

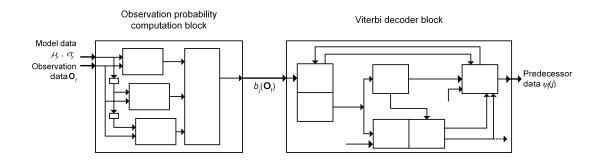

|   | 4.4 | Observ   | ation probability computation | 54 |

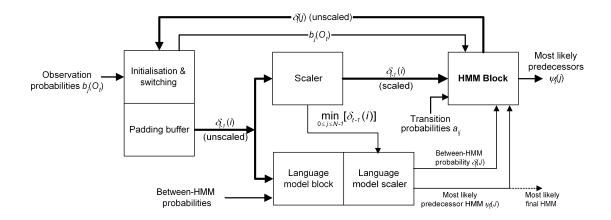

|   |     | 4.3.5    | Padding buffer                | 54 |

|   |     | 4.3.4    | HMM block                     | 52 |

|   |     | 4.3.3    | Language model                | 51 |

|   |     | 4.3.2    | Scaler                        | 51 |

|   |     | 4.3.1    | Initialisation and switching  | 50 |

|   | 4.3 | Viterbi  | decoder                       | 50 |

|   |     | 4.2.2    | HTK                           | 49 |

|   |     | 4.2.1    | General                       | 49 |

|   | 4.2 | Data re  | presentation                  | 49 |

6

| 5.1 | System environment                                                    | 69 |

|-----|-----------------------------------------------------------------------|----|

|     | 5.1.1 Hardware                                                        | 69 |

|     | 5.1.2 Software                                                        | 70 |

|     | 5.1.3 Speech data & models                                            | 75 |

|     | 5.1.4 Virtex/Virtex-E FPGAs                                           | 77 |

| 5.2 | Disc1: discrete, monophones                                           | 77 |

|     | 5.2.1 49-HMM implementation                                           | 78 |

|     | 5.2.2 7-HMM implementation                                            | 78 |

|     | 5.2.3 1-HMM implementation                                            | 79 |

| 5.3 | Cont1: continuous, monophones                                         | 80 |

| 5.4 | Cont1P: continuous, monophones, parallel                              | 82 |

| 5.5 | Cont3P: continuous, biphones/triphones, parallel                      | 83 |

| 5.6 | Cont3_4: continuous, biphones/triphones, parallel, Gaussian mixtures  | 83 |

| 5.7 | Cont3_4D1: continuous, biphones/triphones, Gaussian mixtures, hard-   |    |

|     | ware/software hybrid                                                  | 84 |

| 5.8 | Cont3_4D: continuous, biphones/triphones, Gaussian mixtures, duration |    |

|     | modelling, software                                                   | 85 |

| 5.9 | Summary                                                               | 85 |

| Rea | uirements analysis                                                    | 88 |

| 6.1 | Number of HMMs                                                        | 89 |

| 6.2 | Number of HMMs implemented                                            | 89 |

| 6.3 | Number of mixture components & number implemented                     | 90 |

| 6.4 | Language model                                                        | 90 |

| 6.5 | Duration modelling                                                    | 91 |

| 6.6 | Parallel files                                                        | 92 |

| 6.7 | Results                                                               | 92 |

|     |                                                                       |    |

|    | 6.8    | Summary                                                       | 94  |  |  |  |  |

|----|--------|---------------------------------------------------------------|-----|--|--|--|--|

| 7  | Resi   | esults                                                        |     |  |  |  |  |

|    | 7.1    | Hardware vs software                                          | 96  |  |  |  |  |

|    |        | 7.1.1 Virtex/Virtex-E vs Pentium-III 450 (debug mode)         | 98  |  |  |  |  |

|    |        | 7.1.2 Virtex/Virtex-E vs Pentium-III 450 (release mode)       | 101 |  |  |  |  |

|    |        | 7.1.3 Virtex/Virtex-E vs Athlon XP 2000+ (release mode)       | 102 |  |  |  |  |

|    |        | 7.1.4 Virtex-II (projected) vs Athlon XP 2000+ (release mode) | 104 |  |  |  |  |

|    | 7.2    | Resource usage                                                | 105 |  |  |  |  |

|    | 7.3    | Recognition rates                                             | 106 |  |  |  |  |

|    | 7.4    | <b>Summary</b>                                                | 110 |  |  |  |  |

| 8  | Con    | aclusions                                                     | 111 |  |  |  |  |

|    | 8.1    | Key conclusions                                               | 112 |  |  |  |  |

|    |        | <b>8.1.1 Suitability</b>                                      | 112 |  |  |  |  |

|    |        | 8.1.2 Hardware vs software                                    | 112 |  |  |  |  |

|    |        | 8.1.3 Requirements                                            | 113 |  |  |  |  |

|    | 8.2    | <b>Summary</b>                                                | 114 |  |  |  |  |

|    | 8.3    | Further work                                                  | 114 |  |  |  |  |

|    | 8.4    | The future                                                    | 116 |  |  |  |  |

| Re | eferen | nces 1                                                        | 118 |  |  |  |  |

| Αı | mend   | lix: Publications                                             | 127 |  |  |  |  |

# **Figures**

| 2.1  | HMM finite state machine                              | 17 |

|------|-------------------------------------------------------|----|

| 2.2  | HMM trellis                                           | 17 |

| 4.1  | System structure                                      | 48 |

| 4.2  | Recogniser structure                                  | 48 |

| 4.3  | Viterbi decoder core                                  | 50 |

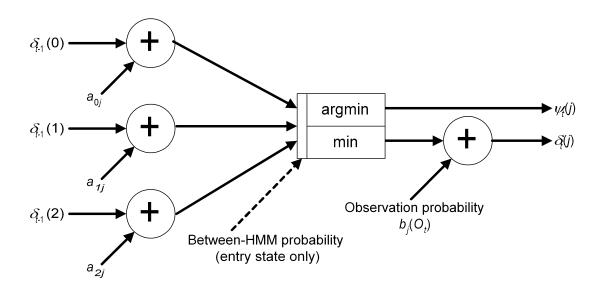

| 4.4  | Node structure                                        | 53 |

| 4.5  | Observation probability computation block             | 55 |

| 4.6  | Gaussian mixture component (GMC) block                | 56 |

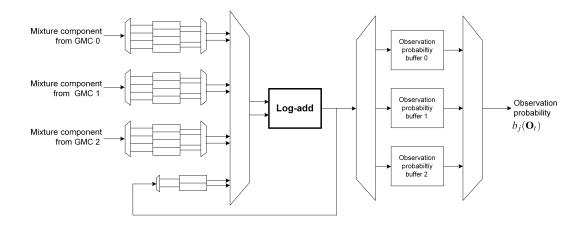

| 4.7  | Gaussian mixture summation block                      | 58 |

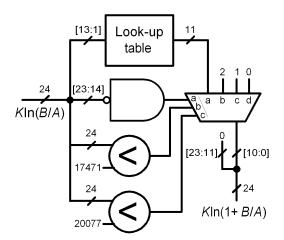

| 4.8  | Log-add table structure                               | 60 |

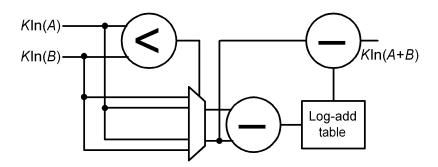

| 4.9  | Log-add structure                                     | 60 |

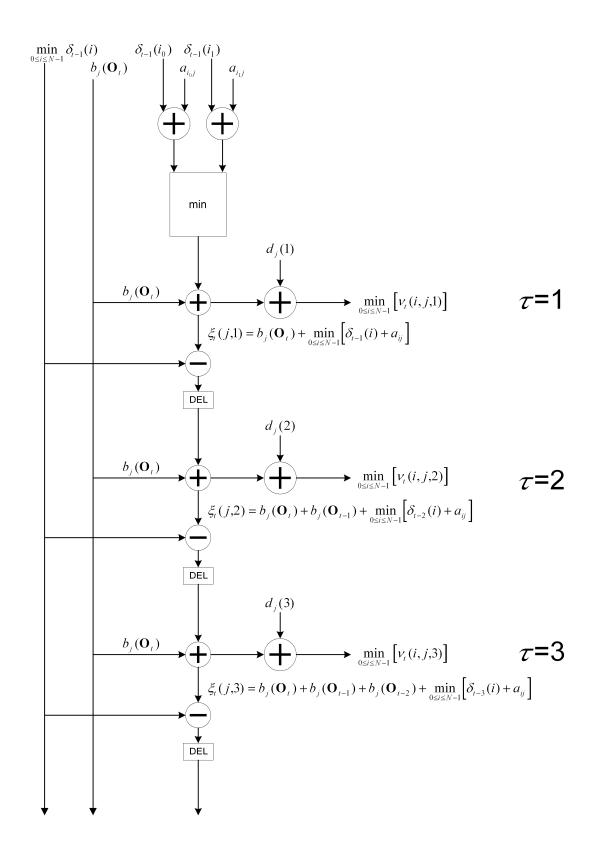

| 4.10 | Proposed architecture for explicit duration modelling | 62 |

| 4.11 | Proposed architecture for language model block        | 64 |

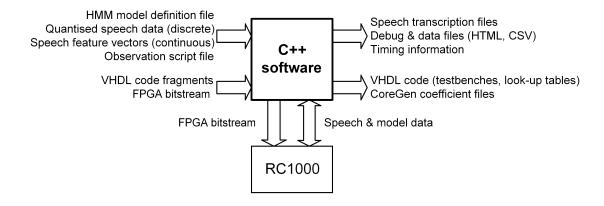

| 5.1  | Software input and outputs                            | 71 |

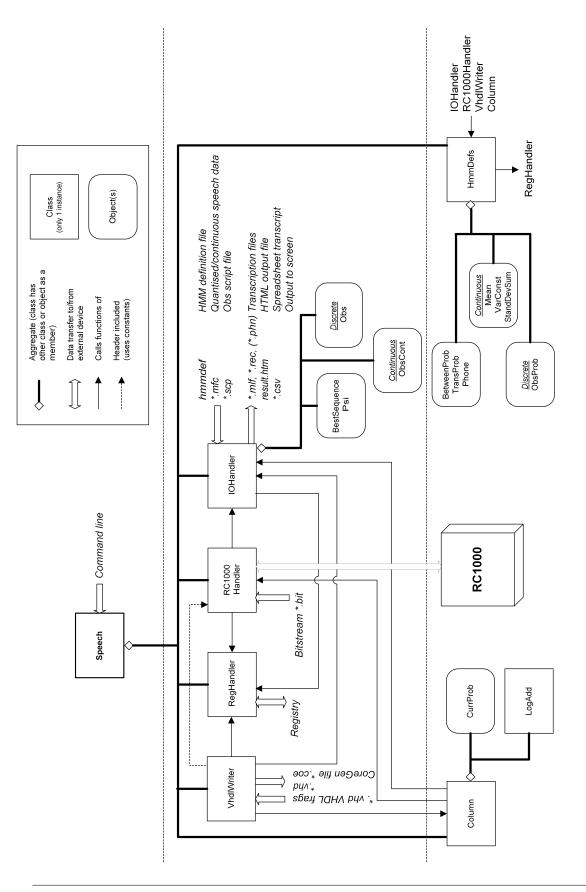

| 5.2  | Software object model                                 | 73 |

# **Tables**

| 5.1 | Speech models                                                       |

|-----|---------------------------------------------------------------------|

| 5.2 | Summary of implementations                                          |

| 6.1 | Summary of effects on time per observation and bandwidth 95         |

| 6.2 | Summary of effects on speedup                                       |

| 7.1 | Timing: Virtex/Virtex-E vs Pentium-III 450 (debug mode) 100         |

| 7.2 | Timing: Virtex/Virtex-E vs Pentium-III 450 (release mode) 100       |

| 7.3 | Release dates for FPGAs and processors under test                   |

| 7.4 | Timing: Virtex/Virtex-E vs Athlon XP 2000+ (release mode) 103       |

| 7.5 | Timing: Virtex-II (projected) vs Athlon XP 2000+ (release mode) 103 |

| 7.6 | Resource usage                                                      |

| 7.7 | Recognition rates                                                   |

#### **Acronyms & abbreviations**

ASIC application-specific integrated circuit

BRAM block RAM

CLB configurable logic block

CORDIC co-ordinate rotation digital computer

DSP digital signal processor/processing

DTW dynamic time warping

FF flip-flop

FIFO first-in, first-out (queue)

FPGA field-programmable gate array

FSM finite state machine

GMC Gaussian mixture component (block) [made up by the author]

HMM hidden Markov model

HTK HMM toolkit

IC integrated circuit ("chip")

I/O input/output

IP intellectual property

LUT look-up table

MFCC mel-frequency cepstral coefficient

MIMD multiple instruction, multiple data

PC personal computer

PCB printed circuit board

PCI peripheral component interconnect p.d.f. probability density/distribution function

PE processing element

PLD programmable logic device RAM random-access memory

ROM read-only memory

RTR run-time reconfiguration

SIMD single instruction, multiple data

SoC system on a chip

SRAM static RAM

SRL shift register (shift right logical)

VHDL very high speed integrated circuit hardware description language

# **Roman symbols**

| $a_{ij}$            | transition probability: probability of a transition from state $i$ to state $j$           |

|---------------------|-------------------------------------------------------------------------------------------|

| $b_j(\mathbf{O}_t)$ | observation probability: probability of state $j$ emitting the observation $\mathbf{O}_t$ |

|                     | at time t                                                                                 |

| $c_{jm}$            | mixture weight for state $j$ and mixture component $m$                                    |

| D                   | maximum duration                                                                          |

| $d_j(	au)$          | duration probability: probability of staying in state $j$ for duration $\tau$             |

| H                   | total number of HMMs                                                                      |

| i                   | previous state                                                                            |

| j                   | current state                                                                             |

| K                   | constant multiplier for log-domain probabilities                                          |

| L                   | number of elements in observation feature vector and Gaussian vectors                     |

| l                   | current element                                                                           |

| M                   | number of mixture components in Gaussian mixture                                          |

| m                   | current mixture component                                                                 |

| K                   | normal (Gaussian) distribution                                                            |

| N                   | total number of states in all HMMs                                                        |

| O                   | observation sequence $\mathbf{O} = \mathbf{O}_0, \mathbf{O}_1 \dots \mathbf{O}_{T-1}$     |

| ${\cal P}$          | probability                                                                               |

| $P^*$               | probability of most likely final state                                                    |

| p                   | word insertion penalty                                                                    |

| Q                   | state sequence $q_0, q_1 \dots q_{T-1}$                                                   |

| $Q^*$               | most likely state sequence $q_0^*, q_1^* \dots q_{T-1}^*$                                 |

| S                   | grammar scale factor                                                                      |

| T                   | length of sequence (maximum time)                                                         |

| t                   | current time                                                                              |

## **Greek symbols**

- $\delta_t(j)$  maximum probability, over all partial state sequences ending in state j at time t, that the HMM emits the sequence  $\mathbf{O} = \mathbf{O}_0, \mathbf{O}_1 \dots \mathbf{O}_t$

- $\lambda^*$  the set of all models representing spoken utterances (word or sub-word unit)

- $\boldsymbol{\lambda}$  a model sequence, representing a sequence of spoken utterances

- $\mu$  mean

- $v_t(i, j, \tau)$  probability at time t, of the system having moved to state j at time  $t \tau + 1$  from state i at time  $t \tau$ , and then having stayed in state j for duration  $\tau$

- $\xi_t(j,\tau)$  probability at time t, of the system having moved to state j at time  $t-\tau+1$  from its most likely predecessor state at time  $t-\tau$ , and emitting the observation sequence from time  $t-\tau+1$  to t

- $\pi_j$  probability of being in state j at time t = 0

- σ standard deviation

- $\sigma^2$  variance

- τ current duration, i.e. length of time spend in the current state

- $\psi_t(j)$  most likely predecessor state of state j at time t

Speak properly, and in as few words as you can, but always plainly; for the end of speech is not ostentation, but to be understood.

William Penn (1644–1718)

# Introduction

omputer! Write me a PhD thesis!" The idea of being able to talk to a computer, and have it understand you, has been a recurring theme in science fiction for decades. While we are not yet at the stage where computers can comprehend our every word, and act on them, these machines are becoming ever more complex and ubiquitous.

But before a computer (or, for that matter, a human being) can attempt to understand speech, it must first convert the audio stream it receives into what that stream actually represents: initially, the basic sounds that make up a language, and ultimately, words. To do that with greater reliability and fidelity, and to be able to cope with different speakers and noisy environments, are the goals of current research in speech recognition.

While others concentrate on developing the algorithms and models, there still remains the question of how to implement them. Commercial software packages already exist which can run on a PC — but they are limited by having to operate on a general-purpose processor. In the end, to achieve the maximum processing power, application-specific hardware is the answer. Accordingly, in this thesis, a hardware implementation of a speech recognition system is presented.

#### 1.1 Aims and objectives

The aim of this research is to design and implement a speech recognition system, with the decoding stage implemented in hardware, in order to:

- assess the suitability of so doing for the various parts of the recognition algorithm;

- compare the processing speed of hardware and software implementations, in order to ascertain the possible speedup;

- determine the requirements inherent in applying hardware to speech recognition.

The hardware in question is a field-programmable gate array (FPGA).

## 1.2 Speech recognition

#### 1.2.1 Overview

A typical speech recognition system consists of three stages. The first is the pre-processing stage, described in more detail below, which takes a speech waveform as its input, and extracts from it feature vectors or observations which represent the information required to perform recognition.

The second stage is recognition, or decoding, which is performed using a set of statistical models called hidden Markov models (HMMs). At their simplest, the HMMs represent monophones, i.e. the basic distinct sounds of a particular language, of which English has around 50. However, when people speak, these sounds are affected by those uttered immediately before and after them. In order to model this effect, a larger number of models, now representing pairs and triplets of monophones (biphones and triphones), can be used, leading to improved recognition ability. In addition, a language model can

be used, which contains further information as to the probability of one recognition unit (monophone or biphone/triphone, as appropriate) following another.

For small- to medium-sized vocabularies, the word and language models are compiled into a single, integrated model. Recognition is performed using the Viterbi algorithm to find the route through this model which best explains the data. For large vocabulary systems, this approach is not viable due to the large size of the search space, and so methods of restricting its size are required. Besides the standard practice of pruning the least likely paths, this can be achieved by incorporating other information, such as data based on language usage [57] or the formation of speech, by using multiple passes, or by heuristic methods such as stack decoding [18][42].

In the third stage, word-level acoustic models are formed by concatenating the recognition units according to a pronunciation dictionary. The word models are then combined with a language model, which constrains the recogniser to recognise only valid word sequences.

The first and third stages can be performed efficiently in software (though some of the pre-processing may be better suited to a DSP). The decoding and associated observation probability calculations, however, place a particularly high load on the processor, and so it is these parts of the system that have been the subject of a number of implementations in hardware, often using custom-built chips. However, with ever more powerful programmable logic devices (PLDs) being available, such chips appear to offer an attractive alternative.

#### 1.2.2 Speech pre-processing

Automatic speech recognition systems make use of the modulation applied by the vocal tract (throat, tongue, teeth, lips and nasal cavity); the excitation produced by the larynx is not used, even though humans infer much information from it. (Note that in a number of

Far-Eastern languages, the inflection of a syllable can profoundly affect its meaning, so requiring this information to be retained [23]).

Converting a speech waveform into a form suitable for processing by the decoder requires several stages. A typical such process [60][65] is as follows:

- 1. The waveform is sent through a low pass filter, typically 4 to 8 kHz. As is evidenced by the bandwidth of the telephone system being around 4 kHz, this is sufficient for comprehension.

- 2. The resulting waveform is sampled. Sampling theory requires a sampling rate of double the maximum frequency (so 8 to 16 kHz as appropriate).

- 3. The data undergoes frequency analysis using a discrete Fourier transform. This produces information about the frequency within each analysis window, which is typically 20 ms wide, with each one overlapping its neighbour by 10 ms.

- 4. Human hearing is not particularly sensitive to phase, so this information is removed by taking the modulus of the complex frequency data.

- 5. Loudness is perceived by humans on a log scale, rather than a linear one, so the log of the power is computed for the frequency data.

- 6. Frequency is also perceived on a non-linear scale. In particular we discriminate better between low frequency sounds than high frequency ones, and so the mel scale is used to compensate for this. A filterbank analysis is performed, whereby the frequency magnitudes are grouped into a number of bins, with the bins spaced out according to the mel scale so as to take account of our non-linear perception. Twelve such bins are typical.

- 7. In order to make recognition calculations less complex (specifically, to ensure that the covariance matrix is diagonal), it is required that the mel-scale filterbank com-

ponents be uncorrelated, which is not normally the case. In order to achieve this, a discrete cosine transform is effected, as a more computationally efficient approximation to principal component analysis, in order to a produce a set of mel-frequency cepstral coefficients (MFCC).

- 8. An additional parameter can be added in the form of an energy term, computed as the log of the signal energy.

- 9. Finally, further information about the "shape" of the speech data can be obtained by taking the first and second derivatives of the cepstral coefficients. Hence, starting with twelve bins, adding an energy value, and then taking the derivatives, we end up with a 39-dimensional vector.

An alternative to mel filterbank analysis is linear prediction, where the vocal tract is modelled by a transfer function, and the filter coefficients are calculated from the data in order to minimise the prediction error.

Whichever method is used, the extracted data values represent the movements of the vocal tract, and not the excitation provided by the larynx. Because the elements of the vocal tract move so slowly in comparison, the effective sampling rate is typically of the order of 100 Hz, and so one observation is produced every 10 ms.

#### 1.2.3 HTK

HTK, the Hidden Markov Model Toolkit [60], developed by Cambridge University Engineering Department, is referred to throughout this thesis.

It consists of a suite of software tools running under UNIX, designed to facilitate the development of speech recognition applications. It can generate and train models of various different types, pre-process speech data, perform recognition, and produce accuracy figures from recogniser data. It was used for all of these functions during this research.

It was particularly useful as a benchmark against which to compare the results of the hardware and software recognisers described in this thesis, in order to verify that they were producing sensible results.

## 1.3 Field-programmable gate arrays

A field-programmable gate array (FPGA) is a form of programmable logic device (PLD). It typically consists of a rectangular array of configurable logic blocks (CLBs). Each CLB can contain assorted logic resources, such as look-up tables (LUTs), capable of implementing any desired boolean function; dedicated arithmetic logic, such as carry chain logic; registers, latches, shift registers, distributed memories, and so on.

The resources within a CLB can be configured as required. Similarly, the data lines that link the resources within the CLB can be configured in order to connect them together in particular ways. And the CLB array itself is immersed in a web of configurable routing, allowing the CLBs to be connected in myriad ways.

There is currently a trend towards combining fixed-function logic with reconfigurable logic, producing a so-called "system on a chip" (SoC). This started with the inclusion of blocks of dedicated RAM — themselves configurable with regard to the widths of their address and data buses — and now includes dedicated multipliers, DSP blocks, and processor cores.

In order to give the reader an idea of the numbers involved here, the FPGA used in the larger designs (XCV2000E) contains 38,400 LUTs (which can be used as any 4-input logic gate, or a 16-stage shift register, or a 16-bit RAM), the same number of flip flops (configurable as registers or level-sensitive latches), and 160 Block RAMs, each providing storage of 4,096 bits.

The field-programmable part of an FPGA comes from the fact that FPGAs can be

programmed and reprogrammed *in situ*, without having to be removed from their target PCB and placed in a chip programmer every time a new design needs to loaded, as is the case with some other types of PLD. Most FPGAs are now SRAM based, and so require a separate ROM to store their configuration data, as they are unable to retain this data themselves when switched off.

With so many resources at the designer's disposal, an FPGA provides a very powerful platform for hardware development. Its flexibility allows for all manner of complex designs; its numerous resources allow for a great deal of parallelism if the application allows it; and its ability to be reprogrammed without limitation makes it an invaluable tool for hardware development.

This is not, however, the only thing that FPGAs are good for. Making ASICs is a very expensive process, and as feature size shrinks, the cost of producing the die is increasing. The economics are such that a manufacturer needs to be expecting to ship a very large number of chips — currently of the order of hundreds of thousands for the smaller feature sizes, and continuing to rise [28][29] — before producing an ASIC becomes costeffective. For smaller quantities, an FPGA or other PLD is cheaper.

Additionally, an FPGA's in-system programmability can be put to other uses. Unlike an ASIC, the FPGA's design can be updated after the PCB has been made and populated, and after the product has been deployed, akin to software patches being downloaded after a product has been shipped.

Taking this a stage further, one chip can be supplied with a library of designs, enabling it to perform different functions depending on the situation. For example, an FPGA could be used as part of a communications subsystem, with different configurations for different protocols, allowing hardware acceleration for all of them, but with just one chip.

Some FPGAs allow parts of the device to be reconfigured, while leaving the rest of the chip untouched. The suggestion has therefore been made for run-time reconfiguration (RTR) (e.g. [22][47]), where some or all of the chip is reprogrammed at run time, providing more processing power than might otherwise be available.

Unfortunately, RTR has not been as successful as hoped, for a number of reasons. Firstly, the reconfiguration times for FPGAs, particularly the larger ones, is of the order of milliseconds, which for devices that can operate at hundreds of megahertz, is a lifetime.

To illustrate this, [17] uses RTR to update the contents of LUTs configured as ROMs, and compares this with the alternative of configuring them as RAMs instead. The authors report that while the RAM-based design has a slower clock speed and uses more resources, the LUTs can be updated much faster, by a factor of over 100.

Secondly, for partial reconfiguration, reprogramming one chunk of an FPGA affects the routing in neighbouring areas, and there is currently no obvious solution as to how to deal with that. The problem can be sidestepped by limiting the reconfiguration to replacing the contents of LUTs or RAM, or by constraining the placement of logic resources so that no routing crosses areas that will be reconfigured.

Thirdly, any complex chip relies heavily on the software that supports it, and current tools have limited support for RTR-based designs. FPGA design software continues to improve, but does still require a lot of skill of the designer — indeed, the question of whether adapting software languages in order to make it easier for software engineers to produce FPGA designs ("C-to-gates") is an ongoing debate.

Additionally, a commercial slant is mentioned in [15]: "There's no market for reconfigurability [right now]. There's a degree of reconfigurability in cellular systems, as in for changing the protocols as you move between countries, but that's a specialist area and it's done by software. The case of design reconfigurability in hardware is yet to be proved, as software is a pretty good way of achieving reconfigurability."

At present, FPGAs' power-hungry nature makes them unsuitable for mobile devices. However, once that changes, their versatility and ability to be repeatedly updated — even if only once in a while — could see them become much more widespread than they are now.

#### 1.4 Motivation

Speech recognition systems work best if they are allowed to adapt to a new speaker, the environment is quiet, and the user speaks relatively carefully; any deviation from this "ideal" will result in significantly increased errors. At present it is not clear whether these problems can be overcome by incremental development of the current HMM-based approach, or whether more fundamental developments are needed. In either case, it is likely that the result will place increased computing demands on the host computer. Hence, as is the case for graphics, it may be advantageous to transfer speech processing to some form of co-processor or other hardware implementation.

For most speech recognition applications, it is sufficient to produce results in real time, and software solutions that do this already exist. However, there are several scenarios that require faster recognition speeds, and so could benefit from hardware acceleration.

For example, in telephony-based call-centre applications, the speech recogniser is required to process a large number of spoken queries in parallel. If one chip could do the job of several PCs, even an expensive device could result in significant savings (not to mention taking up less space). This is typified by the AT&T system described by Gorin *et al* (1997) [12], which classifies responses to the question, "How may I help you?", in order to route calls according to their subject matter.

The possibility of saving time and money is also true of analogous non-real time applications, such as off-line transcription for dictation, where a single system would be able to process multiple speech streams at high speed.

Alternatively, the additional processing power offered by an FPGA or ASIC might be

used for real-time implementation of the "next generation" of speech recognition algorithms, which are currently in development. For example, improved recognition of fluent, conversational speech may require multiple-level acoustic models which incorporate a representation of the speech production process, for example by modelling the movement of the vocal tract. Such models are much more complex than conventional HMMs and, if successful, would inevitably lead to a substantial increase in demand for computing power for speech recognition applications.

Greater computational power can also be used to make the change from speaker dependence to speaker independence, or to make the system more robust and less sensitive to background noise.

Finally, why use an FPGA? It was originally suggested that this project make use of an FPGA with the specific intention of utilising RTR. While there has been much excitement (in academic circles, at least) that the FPGA's unique ability to be reconfigured on the fly could be put to great use, the complexity of doing so, and the limited support of the tools, combined with the ever-increasing quantity of resources available on the device, has seen the idea pushed to one side. Instead, the FPGA's great value has been shown in its use as a prototyping platform, either as a stepping-stone on the path to an ASIC, or as an end in itself, where an ASIC is either undesirable or uneconomical.

While this does not rule out the use of RTR at some point in the future, perhaps in order to allow the user to switch between languages or vocabularies, it remains likely that the same could be achieved by storing the corresponding data off-chip, and loading them on as necessary.

To conclude, even though processor power is always increasing, ASICs and programmable logic devices are subject to the same improvements in technology. Hence whatever we can do in software, we should be able to improve upon by using hardware.

#### 1.5 Contribution

A PhD thesis must "represent an original contribution to knowledge, demonstrate that the student can exercise independent judgment and be worthy of publication in whole or in part in a learned journal or the equivalent."

In terms of an "original contribution," it will be shown in this thesis that hardware is indeed an appropriate platform for speech recognition, with an FPGA being suitable for much of the system, the other parts being best left to alternative architectures, or to software. While it is perhaps no surprise that an FPGA is found to outperform software, it will also be shown that bandwidth and hardware resources are the principal factors affecting the speedup of hardware over software, rather than the size of the speech recognition model.

As part of the process of reaching these conclusions, what is presented here is, as far as the author is aware, the first implementation in hardware of the decoder stage of a speech recognition system, incorporating a core which overcomes bandwidth restrictions to process Gaussian mixtures for multiple speech files in parallel, as well as a Viterbi decoder core. The most closely related work [52] is described in section 3.4.

This thesis also contains the first requirements analysis for a hardware-based speech recogniser, and an original hardware implementation of the log-add algorithm for summing Gaussian mixture components in the log domain.

The log-add implementation is covered in a letter [35], with the various recogniser implementations detailed in four international conference papers [30][31][33][34], and a conference poster [32]. These all appear in the Appendix. Additionally, the requirements analysis has been submitted as a journal paper [36].

In addition to the final "products," the tools and methods used to produce them are themselves an essential part of this research. As chips grow more and more complex,

<sup>&</sup>lt;sup>1</sup>University of Birmingham, Regulation 4.4.3.(3)

it becomes increasingly difficult for the design tools, and hence the designers, to utilise efficiently the wealth of resources at their disposal, and to implement, test and verify their designs within a realistic time frame.

So as a means to an end, also described here is the software toolkit that forms an integral part of this system, which — among other things — is used for benchmarking, verifying the results of the hardware, producing timing and debug information, and generating code for the FPGA designs themselves, as well as for the testbenches used in simulations.

Also worthy of mention is the hardware interface written for the FPGA development board on which the designs were implemented, which was posted on the board manufacturer's website, and has gone on to be included in the designs of other users of the hardware.

#### 1.6 Structure of the thesis

The thesis is composed of eight chapters. Following this introduction, **Chapter 2** provides a comprehensive review of speech recognition theory, as it relates to the work described herein.

**Chapter 3** is a critical review of previous speech recognition systems implemented in hardware, including the use of FPGAs, parallel processors, and serial processors, as well as current commercial speech cores and ASICs.

**Chapter 4** details the designs of the various parts of the recognition system, including the parts that have been implemented in hardware, and proposed designs for those that have not.

In **Chapter 5**, the implementations themselves are discussed, focussing on issues that arose such as resource usage and speed. The system software is also described.

Departing from the main stream of the thesis, **Chapter 6** takes a look at the requirements of implementing speech recognition in hardware and software, in terms of processing time and bandwidth, and draws some general conclusions.

In **Chapter 7** are presented the results of the implementations, in the form of timing information, resource usage, and accuracy figures, along with analyses of the data.

**Chapter 8** then rounds things off with a summary of findings, and conclusions.

Following this are the list of references, and also the credits page, a list of specific individuals, organisations, pieces of software, and items of hardware, which (and whom) have all played a role in this project.

Finally, the **Appendix** contains the publications produced as a result of this research.

Speech is after all only a system of gestures, having the peculiarity that each gesture produces a characteristic sound, so that it can be perceived through the ear as well as through the eye.

Robin George Collingwood (1889–1943)

2

# Speech recognition theory

This chapter provides a comprehensive guide to speech recognition theory, as it relates to the implementations described later in this thesis.

Hidden Markov models (HMMs), the most commonly used basis for recognition implementations, create scope for incremental increases in the complexity of the algorithm, and hence better modelling of real speech. Presented here is the basic underlying theory, followed by a number of such extensions.

Speech recognition theory has been around for some time, and so a number of more detailed texts on the subject exist [8][44][59]. A more gentle introduction can be found in [65].

## 2.1 The speech recognition problem

The underlying problem of speech recognition is as follows. Given an observation sequence  $\mathbf{O} = \mathbf{O}_0, \mathbf{O}_1 \dots \mathbf{O}_{T-1}$ , where each  $\mathbf{O}_t$  is a data value representing speech which

<sup>&</sup>lt;sup>1</sup>It is common in speech recognition literature to enumerate vector indices, state numbers, and time, from 1 to their respective upper limits. However, when implementing such things in hardware — and, for that

has been sampled at a fixed interval, the current time being t; and a set of potential models  $\lambda^*$ , each of which is a representation of a particular spoken utterance (e.g. word or sub-word unit); we would like to find the sequence of models which best describes the observation sequence, in the sense that the probability  $\mathcal{P}(\lambda|\mathbf{O})$  is maximised (i.e. the probability that  $\lambda$ , being a subset of  $\lambda^*$ , is the best sequence of models given  $\mathbf{O}$ ).

This value cannot be found directly, but can be computed via Bayes' Theorem [59]:

$$\mathcal{P}(\lambda|\mathbf{O}) = \frac{\mathcal{P}(\mathbf{O}|\lambda) \cdot \mathcal{P}(\lambda)}{\mathcal{P}(\mathbf{O})},$$

(2.1)

where  $\mathcal{P}(\mathbf{O}|\lambda)$  is the acoustic model probability, being the probability of the model sequence  $\lambda$  producing the observation sequence  $\mathbf{O}$ ; and  $\mathcal{P}(\lambda)$  is the language model probability, namely the *a priori* probability of the model sequence  $\lambda$  being produced (and hence the corresponding sequence of words or sub-word units being uttered).

Where  $\mathbf{O}$  is a set of continuous, rather than discrete, values,  $\mathcal{P}$  represents probability *density*, since the actual probability of a continuous value tends to zero. For generality,  $\mathcal{P}$  is used here for both continuous probability densities and discrete probabilities.

Hence by finding the model sequence  $\lambda$  which maximises  $\mathcal{P}(\mathbf{O}|\lambda)$ , we can maximise  $\mathcal{P}(\lambda|\mathbf{O})$ . Since  $\mathcal{P}(\mathbf{O})$  is independent of  $\lambda$ , this reduces to:

$$\underset{\lambda}{\arg\max} \, \mathcal{P}(\lambda|\mathbf{O}) = \underset{\lambda}{\arg\max} \, \mathcal{P}(\mathbf{O}|\lambda) \cdot \mathcal{P}(\lambda). \tag{2.2}$$

The algorithm used here subsumes the language model part, and hence  $\mathcal{P}(\lambda)$ , into the computations for the acoustic model probability.

The resulting recognised utterance is the one represented by the model sequence that is most likely to have produced **O**. The models themselves are based on HMMs.

matter, in software — it is more efficient to number items from 0 to limit—1, and the equations presented here take this into account. The only exception to this is the current duration  $\tau$ , which represents an actual quantity (the length of time spent in the current state), as opposed to an arbitrary index.

#### 2.2 Hidden Markov models

The most widespread and successful approach to speech recognition is based on the hidden Markov model (HMM) [8][44][59], whereby a probabilistic process models spoken utterances as the outputs of finite state machines. The notation here is based on [44].

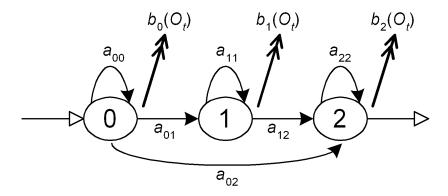

An N-state Markov model is completely defined by a set of N states forming a finite state machine, and an  $N \times N$  stochastic matrix defining transitions between states, whose elements  $a_{ij} = \mathcal{P}(\text{state } j \text{ at time } t | \text{state } i \text{ at time } t-1)$ ; these are the *transition probabilities*.

In a hidden Markov model (Fig. 2.1), each state additionally has associated with it a probability density function  $b_j(\mathbf{O}_t)$  which determines the probability that state j emits a particular observation  $\mathbf{O}_t$  at time t (the model is "hidden" because knowledge of the observation is not sufficient to unambiguously identify the state). The p.d.f. can be a probability density function for continuous data, or a probability distribution function for discrete data; accordingly the pre-processed speech data can be a multi-dimensional vector or one or more quantised values.  $b_j(\mathbf{O}_t)$  is known as the *observation probability*, and is described in more detail below.

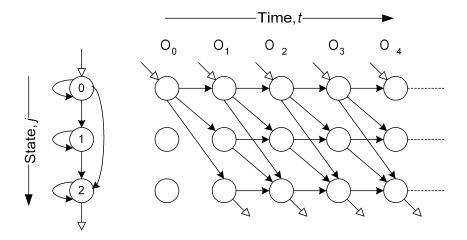

Such a model can only generate an observation sequence  $\mathbf{O} = \mathbf{O}_0, \mathbf{O}_1 \dots \mathbf{O}_{T-1}$  via a state sequence of length T, as a state only emits one observation at each time t. The set of all such state sequences can be represented as routes through the state-time trellis shown in Fig. 2.2. The  $(j,t)^{\text{th}}$  node within the trellis corresponds to the hypothesis that observation  $\mathbf{O}_t$  was generated by state j. Two nodes (i,t-1) and (j,t) are connected if and only if  $a_{ij} > 0$ .

As described above, we maximise  $\mathcal{P}(\lambda|\mathbf{O})$  by maximising  $\mathcal{P}(\mathbf{O}|\lambda)$ . Given a state sequence  $Q = q_0, q_1 \dots q_{T-1}$  (where  $q_t$  is the state at time t), observation sequence  $\mathbf{O}$ , and a model  $\lambda$ , the joint probability of the state sequence and observation sequence, given the

Figure 2.1: HMM finite state machine, showing the paths between states within the HMM (filled arrows), and paths between HMMs (unfilled arrows). The probability of a transition from state i to state j (transition probability  $a_{ij}$ ) is shown, as is the probability of each state emitting the observation corresponding to time t (observation probability  $b_j(\mathbf{O}_t)$  for each state j) (double-headed arrows)

Figure 2.2: HMM trellis, showing the finite state machine for the HMM (left), the observation sequence (top), the trellis representing all possible paths between states within the HMM (filled arrows), and paths between HMMs (unfilled arrows)

model, is:

$$\mathcal{P}(\mathbf{O}, Q|\lambda) = b_0(\mathbf{O}_0) \prod_{t=1}^{T-1} a_{q_{t-1}q_t} b_{q_t}(\mathbf{O}_t), \tag{2.3}$$

assuming that the HMM is in state 0 at time t = 0.  $\mathcal{P}(\mathbf{O}|\lambda)$  is then the sum over all possible routes through the trellis, i.e.:

$$\mathcal{P}(\mathbf{O}|\lambda) = \sum_{\text{all } Q} \mathcal{P}(\mathbf{O}, Q|\lambda). \tag{2.4}$$

The aim is to find the state sequence such that the joint probability of the system following that sequence, and the observation sequence being produced, given the model, is maximised. This can be computed efficiently using Viterbi decoding (below).

#### 2.3 Viterbi decoding

Viterbi decoding [55] was first proposed in 1967 as an efficient method for the decoding of convolutional codes, an encoding system designed to prevent and correct errors when transmitting data over a noisy channel. Its use has since been extended to other applications, including gene sequencing and speech recognition.

#### 2.3.1 Decoding

Rather than compute all possible paths though the trellis, as suggested by equation (2.4), we instead approximate  $\mathcal{P}(\mathbf{O}|\lambda)$  by finding the probability associated with the state sequence which *maximises*  $\mathcal{P}(\mathbf{O}, Q|\lambda)$ .

Firstly, we define the value  $\delta_t(j)$  as the maximum probability, over all partial state sequences  $q_0, q_1 \dots q_t$  ending in state j (enumerated from 0 to N-1, where N is the total number of states in all HMMs) at time t (where  $0 \le t \le T-1$ ), that the HMM emits the

sequence  $\mathbf{O}_0, \mathbf{O}_1 \dots \mathbf{O}_t$ :

$$\delta_t(j) = \max_{q_0, q_1 \dots q_t} \mathcal{P}(q_0, q_1 \dots q_t; q_t = j; \mathbf{O}_0, \mathbf{O}_1 \dots \mathbf{O}_t | \lambda). \tag{2.5}$$

It follows from equations (2.3) and (2.5) that the value of  $\delta_t(j)$  can be computed iteratively as follows:

$$\delta_t(j) = \max_{0 < i < N-1} [\delta_{t-1}(i) \cdot a_{ij}] \cdot b_j(\mathbf{O}_t), \tag{2.6}$$

where i is a possible previous state (i.e. at time t-1).

This value determines the most likely predecessor state  $\psi_t(j)$ , for the current state j at time t, given by:

$$\psi_t(j) = \underset{0 \le i \le N-1}{\arg \max} [\delta_{t-1}(i) \cdot a_{ij}]. \tag{2.7}$$

Because we are looking at the maximum of a set of  $\delta_t(j)$  values at each time frame, it is only their values relative to each other that are important, not their absolute values. As a result, we can perform operations on the data that affect the absolute values, in order to reduce the computational complexity or otherwise, as long as they maintain their position relative to each other.

#### 2.3.2 Termination & backtracking

Each state's most likely predecessor is stored at each time frame. At the end of the observation sequence, the most likely final state  $q_{T-1}^*$  is found by simply looking for the final state whose value of  $\delta_{T-1}(j)$  is highest. This value is denoted as  $P^*$ :

$$P^* = \max_{0 \le j \le N-1} [\delta_{T-1}(j)]$$

$$q_{T-1}^* = \arg\max_{0 \le j \le N-1} [\delta_{T-1}(j)]. \tag{2.8}$$

Finally, in order to ascertain the most likely state sequence  $Q^* = q_0^*, q_1^* \dots q_{T-1}^*$ , we trace backwards from  $q_{T-1}^*$ , looking at each state's most likely predecessor, until we reach the start of the sequence:

$$q_t^* = \psi_{t+1}(q_{t+1}^*). \tag{2.9}$$

So far, Viterbi decoding has been applied to finding the best path through an HMM representing a particular utterance. However, if we combine all of these HMMs, linking each HMM's exit state(s) to every HMM's entry state(s), one big HMM is created.

By applying Viterbi decoding to the trellis that results from this, the resulting sequence not only describes the most likely route through a particular HMM, but now, by this concatenation of HMMs, provides the most likely sequence of HMMs themselves, and hence the most likely sequence of words or sub-word units uttered.

This is known as the "one-pass" algorithm [5][6], and it allows connected speech recognition. This is distinct from continuous speech recognition, in that it assumes a finite sequence of observations, whereas the latter does not rely on the speech "ending" at a known time.

#### 2.3.3 Assumptions

It is assumed throughout that all state sequences begin in an HMM's entry state.

The initial value of  $\delta_t(j)$  often appears as:

$$\delta_0(j) = \pi_j \cdot b_j(\mathbf{O}_0), \tag{2.10}$$

where  $\pi_j$  is the probability of starting in state j at time t = 0,  $\sum_j \pi_j = 1$ , and  $0 \le j \le N - 1$ . If no language model is used, then  $\pi_j = 1/H$ , where j is an entry state, and H is the number of HMMs; for non-entry states,  $\pi_j = 0$ . Since we are only ever interested in the relative values of  $\delta_t(j)$ , there is no need to multiply them all by the same constant, so this value

can be ignored. If a language model is used, this may have an effect on the allowed initial HMMs, as well as the entry states.

Is it also assumed that all state sequences end in an HMM's exit state, so when computing  $P^*$  and  $q_{T-1}^*$ , non-exit states are ignored.

#### 2.3.4 Log-domain representation

For both software and hardware, multiplication is usually a more costly operation than addition. In particular, when designing for hardware, resource usage is a key factor, and multipliers use significantly more resources than adders. Even though some newer FPGAs have dedicated multipliers, the logic available for addition is faster and more plentiful.

Hence by performing Viterbi decoding in the log domain, all of the multiplications are converted to additions, and so can be implemented more efficiently.

Once again, the fact that it is only the relative values of  $\delta_t(j)$  that are of concern, not their absolute values, means that the logarithm function, being monotonic, does not affect the validity of the result.

In addition, the log of a probability is always a negative number (assuming that we use a base greater than 1), so we negate the result. This has the effect of turning the max operation into a min; accordingly, certainty is represented as zero, while impossibility is now  $+\infty$ .

Hence  $\delta_t(j)$  and  $\psi_t(j)$  are redefined as follows:

$$\delta_t(j) = \min_{0 \le i \le N-1} [\delta_{t-1}(i) + a_{ij}] + b_j(\mathbf{O}_t)$$

(2.11)

$$\delta_{t}(j) = \min_{0 \le i \le N-1} [\delta_{t-1}(i) + a_{ij}] + b_{j}(\mathbf{O}_{t})$$

$$\psi_{t}(j) = \underset{0 \le i \le N-1}{\arg \min} [\delta_{t-1}(i) + a_{ij}],$$

(2.11)

where  $1 \le t \le T - 1$ ,  $0 \le j \le N - 1$ . The transition probability is similarly updated so as to be the negated log of its old value, a calculation that can be done in advance. Other definitions are modified in the same way, and we continue in the negative log domain from this point onwards.

# 2.4 Language model

While the above equations can be applied to transitions both within and between HMMs, the latter are typically treated differently, in the form of a statistical language model.

Using I to represent the exit state of a previous HMM (there may be more than one exit state), and J the entry state of the current HMM, we introduce  $a_{IJ}$  as the language model probability, i.e. the probability of a transition from one HMM's exit state to another's entry state. In addition, each exit state has a probability of a transition  $a_I$  from that state to any other HMM.

Associated with the language model are two constants: s, the grammar scale factor, by which  $a_{IJ}$ , in the negative log domain, is multiplied, and p, the word insertion penalty, to which it is added. These correspond in the linear domain to  $a_{IJ}$  being raised to the power of s, and divided by p. Hence both of these values reduce the probability of a transition between utterances, thereby removing many spurious results (and the occasional correct one), and are found experimentally.<sup>2</sup>

Continuing in the log domain, these values are related by modifying equation (2.11) as follows:

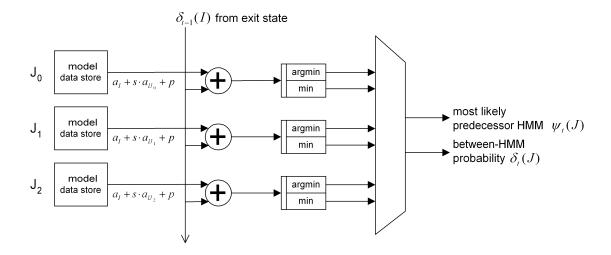

$$\delta_t(J) = \min_{0 \le J \le N-1} [\delta_{t-1}(I) + a_I + s \cdot a_{IJ}] + p, \tag{2.13}$$

where  $\delta_{t-1}(I) = \delta_{t-1}(i)$  for any i which is an exit state. This can be slightly optimised by grouping together the constants into one combined value dependent on I and J:

$$\delta_t(J) = \min_{0 \le I \le N-1} [\delta_{t-1}(I) + (a_I + s \cdot a_{IJ} + p)]. \tag{2.14}$$

<sup>&</sup>lt;sup>2</sup>The notation used here is not based on any particular paper, since little or no mention is made in the literature of the equations associated with language models. The use of s and p is from HTK.

The most likely predecessor HMM,  $\psi_t(J)$ , is found in the same way as before, namely by replacing the 'min' by an 'arg min'.

If no language model is used,  $a_{IJ}$  is same for all HMMs, and so is equal to 1/H in the linear domain, or  $-\ln(H)$  in the log domain, where H is the total number of HMMs (assuming each HMM has exactly one entry state). Accordingly,  $\delta_t(J)$  becomes simply  $\delta_t$ , being the same for *all* HMMs, so need only be computed once in each time frame:

$$\delta_t = \min_{0 \le I \le N-1} [\delta_{t-1}(I) + (a_I - s \cdot \ln(H) + p)]. \tag{2.15}$$

Conveniently, no special calculation (or in hardware, no additional computation block) is required to find the minimum (most likely) final value of  $\delta_{T-1}(j)$  and its corresponding most likely final state ( $P^*$  and  $q_{T-1}^*$  respectively, as defined in equation (2.8)). Because of the requirement that the state sequence end in an HMM's final state, the most likely final state is simply equal to  $\delta_T$ . In other words, the most likely final state is the exit state of the most likely predecessor HMM at time T (if the sequence were to continue to time T).

#### 2.5 Discrete HMMs

The simplest way of determining the value of the observation probability  $b_j(\mathbf{O}_t)$  is to look it up in a table (also referred to as a codebook), and that is what discrete HMMs do.

The observation feature vectors are compared to a number of candidate points in state space, and the "nearest", according to some kind of distance metric, is used to represent that observation. This is vector quantisation.

At each time frame t, the observation is quantised in this way, and for each state, the probability corresponding to the current state having produced that quantised value is looked up in a table.

This approach is computationally simpler than calculating the observation probability,

such as in the way described below, and can model any shape of probability distribution. However, vector quantisation introduces errors at an early stage in the recognition process which cannot be corrected later on, hence the tendency to use continuous HMMs nowadays.

### 2.6 Continuous HMMs

The use of a continuous p.d.f. seeks to overcome the problems inherent in discrete HMMs. We use a multivariate Gaussian (normal) distribution, with each state having a vector of means  $\mu_i$ , and covariance matrix  $C_i$ .

It is common to assume (or arrange) that the components of the feature vectors are mostly uncorrelated, which reduces  $C_j$  to being predominantly zero except along its main diagonal. This removes some of the computational complexity, leading to the following form of the Gaussian equation:

$$\mathcal{N}(\mathbf{O}_t; \boldsymbol{\mu}_j, \boldsymbol{\sigma}_j) = \prod_{l=0}^{L-1} \frac{1}{\sigma_{jl} \sqrt{2\pi}} \exp\left(-\frac{1}{2} \left(\frac{O_{tl} - \mu_{jl}}{\sigma_{jl}}\right)^2\right), \tag{2.16}$$

where  $\mathbf{O}_t$  is the vector of observation values at time t;  $\boldsymbol{\mu}_j$  and  $\boldsymbol{\sigma}_j$  are mean and variance vectors respectively for state j;  $O_{tl}$ ,  $\mu_{jl}$  and  $\boldsymbol{\sigma}_{jl}$  are the elements of the aforementioned vectors, enumerated from 0 to L-1.

This model is still limited by the fact that observed distributions are not Gaussianshaped, so a further extension is to use multiple-component Gaussian mixtures. For this, the final probability is the sum of a number of individually weighted Gaussian distributions:

$$b_{j}(\mathbf{O}_{t}) = \sum_{m=0}^{M-1} c_{jm} \cdot \mathcal{N}(\mathbf{O}_{t}; \boldsymbol{\mu}_{jm}, \boldsymbol{\sigma}_{jm}), \qquad (2.17)$$

where  $c_{jm}$  is the mixture weight for state j and mixture component m, the mixture com-

ponents are enumerated from 0 to M-1, and:

$$c_{jm} \ge 0, \quad \sum_{m=0}^{M-1} c_{jm} = 1.$$

(2.18)

As with Viterbi decoding, we can reduce the computational complexity by performing the necessary calculations in the negative log domain, resulting in the following equation for each mixture component:

$$-\ln(c_{jm}\cdot\mathcal{N}(\mathbf{O}_t;\boldsymbol{\mu}_{jm},\boldsymbol{\sigma}_{jm}))=$$

$$\left[ -\ln(c_{jm}) + \frac{L}{2}\ln(2\pi) + \sum_{l=0}^{L-1}\ln(\sigma_{jml}) \right] + \sum_{l=0}^{L-1}(O_{tl} - \mu_{jml})^2 \cdot \left[ \frac{1}{2\sigma_{jml}^2} \right]. \tag{2.19}$$

For the implementation that uses a simple Gaussian,  $c_{jm}$  is set to 1, hence  $\ln(c_{jm})$  disappears from the equation.

Note that the values in square brackets are dependent only on the current state, not the current observation, so can be computed in advance. This reduces the equation to its final form:

$$-\ln(c_{jm} \cdot \mathcal{N}(\mathbf{O}_t; \boldsymbol{\mu}_{jm}, \boldsymbol{\sigma}_{jm})) = S_{jm} + \sum_{l=0}^{L-1} (O_{tl} - \mu_{jml})^2 \cdot V_{jml}, \qquad (2.20)$$

where  $S_{jm}$  and  $V_{jml}$  replace the bracketed terms from above.

For computation in hardware,  $S_{jm}$  can be subsumed into the summation by adding an extra element to all of the vectors, assigning this value to  $V_{jml}$ , and setting  $O_{tl}$  to 1 and  $\mu_{jml}$  to 0. In software, we can keep a running total which is intialised to  $S_{jm}$ .

The result of this is that for each vector element of each state, we now require a subtraction, a square and a multiplication.

## 2.7 Gaussian mixture summation (log-add algorithm)

When it comes to summing the mixture components (equation (2.17)), we are faced with the problem of performing addition in the linear domain of values computed in the log domain.

While we could use look-up tables or CORDIC to convert between domains (as covered in section 3.7), a convenient algorithm exists for this specific problem [14]. It removes the need to convert between domains at all, instead relying on a look-up table significantly smaller than for the logarithm or exponential operations, along with some simple arithmetic computations — and hence well suited for implementation on an FPGA.

Given two values ln(A) and ln(B) for which we would like to compute ln(A+B):

$$A+B = A(1+B/A)$$

$$\Rightarrow \ln(A+B) = \ln(A(1+B/A))$$

$$\Rightarrow \ln(A+B) = \ln(A) + \ln(1+B/A). \tag{2.21}$$

To compute the result, we work out  $\ln(B/A)$ , which is equal to  $\ln(B) - \ln(A)$ , and then use a look-up table to map that value to  $\ln(1 + B/A)$ . Since the values in this table are dependent on the *relative* values of A and B, it can be smaller than one which relies on their actual values (see also section 4.5).

In order to minimise the size of the look-up table without compromising accuracy, we require that  $A \ge B$ , hence limiting 1 + B/A to the range [1,2], and switch the values if this condition is not met.

# 2.8 Duration modelling [25][37][44]

In the form described above, the probability of the system staying in state j for a duration  $\tau$  forms a geometric sequence, equal (in the linear domain) to  $a_{jj}^{\tau-1}(1-a_{jj})$ . However, this has not been found to model observed speech accurately. This can be improved on by replacing this implicit duration model with an explicit one  $d_j(\tau)$ .

Accordingly,  $\delta_t(j)$  is redefined (still in the negative log domain), with the constraint that the state at time t + 1 does not equal the state at time t, as follows:

$$\delta_t(j) = \min_{\substack{0 \le i \le N-1 \\ i \ne j}} \min_{1 \le \tau \le D} [v_t(i, j, \tau)], \tag{2.22}$$

where  $\tau$  is the number of times that we remain in state j, i is the state at time  $t - \tau$ , D is the maximum duration, and:

$$v_t(i,j,\tau) = \delta_{t-\tau}(i) + a_{ij} + d_j(\tau) + \sum_{s=0}^{\tau-1} b_j(\mathbf{O}_{t-s}).$$

(2.23)

$v_t(i, j, \tau)$  is the probability at time t, of the system having moved to state j at time  $t - \tau + 1$  from state i at time  $t - \tau$ , and then having stayed in state j for duration  $\tau$ . Note that, because self-transitions are now handled explicitly, cases where i = j (i.e. where the current and previous states are the same) are discounted. This can equally be effected by setting  $a_{jj}$  to zero ( $+\infty$  in the negative log domain).

As will become apparent in section 4.6, for more efficient implementation in hardware and software, it is convenient to extend these definitions. Firstly, if we take the minimum of  $v_t(i, j, \tau)$  over all previous states, we can group the terms into those that are dependent on the previous state, and those that are not:

$$\min_{\substack{0 \le i \le N-1 \\ i \ne j}} [\mathsf{v}_t(i,j,\tau)] = \left[ d_j(\tau) + \sum_{s=0}^{\tau-1} b_j(\mathbf{O}_{t-s}) \right] + \min_{\substack{0 \le i \le N-1 \\ i \ne j}} \left[ \delta_{t-\tau}(i) + a_{ij} \right]. \tag{2.24}$$

Secondly, by removing  $d_j(\tau)$ , we can define  $\xi_t(j,\tau)$  as the probability at time t, of the system having moved from its most likely predecessor state at time  $t - \tau$  to state j at time  $t - \tau + 1$ , and emitting the observation sequence from time  $t - \tau + 1$  to t:

$$\xi_t(j,\tau) = \sum_{s=0}^{\tau-1} b_j(\mathbf{O}_{t-s}) + \min_{\substack{0 \le i \le N-1 \\ i \ne j}} \left[ \delta_{t-\tau}(i) + a_{ij} \right]. \tag{2.25}$$

This value is useful, as it can also be defined iteratively, avoiding the need for any recomputation:

$$\xi_t(j,\tau) = \xi_{t-1}(j,\tau-1) + b_j(\mathbf{O}_t).$$

(2.26)

Finally, we can redefine  $\delta_t(j)$  in terms of  $\xi_t(j,\tau)$ :

$$\delta_t(j) = \min_{1 < \tau < D} [d_j(\tau) + \xi_t(j, \tau)]. \tag{2.27}$$

The way in which these values fit together is illustrated in Fig. 4.10 on page 62.

# 2.9 Summary

In this chapter, the aspects of speech recognition theory of relevance to this research have been presented. The underlying problem has been posed, and hidden Markov models introduced to provide a solution, with Viterbi decoding enabling them to do so. Discrete and continuous HMMs have been described, along with a number of extensions to the basic algorithm, namely the language model, Gaussian mixtures, and duration modelling.

Before looking at how this assortment of algorithms might be implemented in hardware, it is first necessary to cast a critical eye over previous such implementations, and so that is the area visited next. The newest computer can merely compound, at speed, the oldest problem in the relations between human beings, and in the end the communicator will be confronted with the old problem, of what to say and how to say it.

Edward R. Murrow (1909–1965)

3

# Speech recognition in hardware

It is only in the last few years that desktop PCs have been powerful enough to allow large-vocabulary continuous speech recognition to be performed, in real time, in software. At present though, for best results, they still rely on being trained to recognise one speaker, with minimal background noise. Even then, steps have to be taken in order to reduce the computational complexity so that real time recognition is feasible.

Before this was possible, or when it was necessary to try out more complex algorithms, only hardware had the computational resources to achieve this.

Initially, hardware implementations tended to be based on parallel arrays of one kind or another, often using custom chips. As the technology has improved, the focus has shifted towards serial implementations, making use once again of custom chips, or microcontrollers or DSPs. Since the appearance of the FPGA, that too has been used as an experimental platform.

Of the three principal stages of the speech recognition process, it is the decoding part that takes centre stage in hardware implementations. Pre-processing tends to be performed in software, or left to a DSP (though Gómez-Cipriano *et al* (2001) [11] use an FPGA for

feature extraction). Backtracking, as described below, is much better suited for processing in software, rather than hardware.

So it is Viterbi decoding, and latterly, observation probability computation, that are by far the most popular choice for implementations in hardware, and it is an assortment of such implementations that is reviewed in this chapter.

## 3.1 Accuracy measures

The accuracy figures which appear here are intended to give an indication of how good the cited recognition systems are. However, comparing values for different recognisers can be misleading, as there are a number of factors which can affect this value.

First is the type of recogniser. A small-vocabulary system, such as one used for digit recognition, has a smaller number of HMMs, with fewer parameters for the training process to set, and a correspondingly constrained search space. So *for its specified vocabulary*, it is likely to achieve a high score; for anything outside this, it will not. This contrasts with a large-vocabulary recogniser, which may give a lower recognition rate, but is capable of recognising many more words.

In a similar vein, a speaker-dependent system is likely to perform well for the speaker it has been trained for, and not so well otherwise, whereas a speaker-independent system is not tied to any one speaker.

The type of recogniser also places limits on recognition rate. Generally speaking, the better the model is at representing speech, the more processing that is required, and the higher the recognition rate is likely to be. So continuous HMMs tend to do better then discrete ones, and biphone & triphone models tend to outperform monophone models.

Finally, the accuracy rate can be manipulated by what is and is not included in that figure. The value used by HTK in section 7.3 takes both correctly identified recognition

units and incorrect insertions into account, resulting in a lower score than one which relies on correct utterances alone. This value can be further increased by treating similar-sounding units as being the same unit.

# 3.2 Parallel systems

Parallel implementations of speech recognition systems have been produced before, most using HMMs. In contrast to the approach described here, previous implementations have generally used multiple processing elements (PEs) of varying sophistication, either at the board or ASIC level, rather than a programmable logic device.

#### 3.2.1 Custom ICs

Murveit *et al* (1989) [39] use 5 custom integrated circuits (ICs) to implement a system whose Viterbi decoder has much in common with the designs presented in this thesis. Their decoder chip has 3 parallel adders to add  $\delta_t(j)$  and  $a_{ij}$ , a comparator to find the minimum, and another adder to add  $b_j(\mathbf{O}_t)$ . It also incorporates a scaler. Another IC handles the language model, with the model probabilities, and  $\delta_t(j)$  and  $\delta_{t-1}(i)$  stored in off-chip RAM.

The system is designed for continuous real-time speech, with a vocabulary of 3,000 words (9,000 states), based on bigrams and discrete HMMs. As is described in chapter 5 with reference to the implementations presented there, memory bandwidth is the major performance-limiting factor.

This work is continued by Stölzle *et al* (1991) [50], using 50,000 states and discrete HMMs. Again, a dedicated Viterbi decoder chip is used, accompanied now by a backtrack processor, which computes  $\psi_t(j)$  values for each state while the corresponding  $\delta_t(j)$  values are being computed.

It is pointed out in [37] that custom Viterbi decoders like these have two disadvantages. Firstly, pruning is made harder, as having multiple computations done in parallel means that for any time to be saved, *all* of the processing blocks' data must be pruned equally. If this does not happen, the other blocks must wait for the unpruned data to finish being processed.

Secondly, such decoders have less flexibility when it comes to interconnects. Both of these implementations assume that most states have up to three predecessors, and that only left-right transitions (i.e. transitions, within an HMM, that go from a state to itself, or to a state with a higher index) are allowed, thereby limiting themselves to one class of model.

In contrast, the implementations described in chapter 5 allow transitions in both directions, which is useful for silence models in particular. Also, although the underlying design assumes that states have three predecessors (four in the case of entry states), this could be changed at compile time if necessary.

## 3.2.2 SIMD arrays

Many of the first attempts at using hardware for speech recognition focussed on the single instruction, multiple data (SIMD) array, whereby all the processing elements (PEs) in the array carry out the same instructions on different data.

SIMD arrays are not directly comparable to FPGAs, since FPGAs do not contain processing elements as such. However, the way in which the algorithm is implemented on a SIMD array, in particular, the extent to which certain tasks can be pipelined and/or run concurrently, can be applied when implementing them on an FPGA.

Bisiani *et al* (1989) [3] use 3 general-purpose processors, with local and shared memory, to perform Viterbi decoding, splitting the 1,000 words in the model between them, and averaging a speed of 1.3 times real time.

They point out that while each PE is free to process states at its own pace, they must all finish processing the data for the current time frame before the next set of data can be loaded. Hence balancing the load between PEs is important in order to avoid them sitting idle, and this is an issue that comes up in a number of SIMD implementations. In this case, this is achieved by giving each processor its own data queue, but with a mechanism to allow data to be redistributed if an imbalance occurs.

The INMOS T800 transputer has proven to be a popular choice for SIMD implementations, with load balancing again a highly relevant issue. Alexandres *et al* (1990) [1] compare different topologies (linear, ring and tree) of PEs in a processor farm, whereby data values are sent by the host through the PEs in sequence, until a free one is found; the results of the processing are sent back through the network to the host. The load balancing mechanism is therefore distributed and automatic.

Pruning is also addressed: the host PE compares all the data to a threshold, and only sends values above the threshold to the processor farm. The authors report that this does not affect accuracy, while improving the processing speed by a factor of 3 to 4, or allowing fewer processors to be used.

The implementation uses discrete HMMs, and a vocabulary of 1,000 words.