# Early failure detection of insulated-gate bipolar transistor semiconductor devices for the power converters of wind turbines

#### Rana Moeini

A thesis submitted to the University of Birmingham for the degree of Doctor of Philosophy

Department of Civil Engineering School of Engineering University of Birmingham

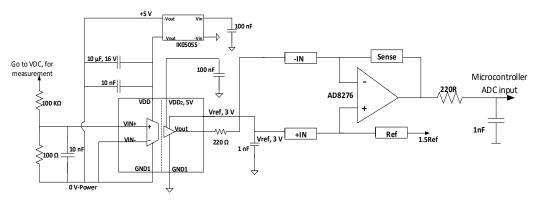

# UNIVERSITY<sup>OF</sup> BIRMINGHAM

## **University of Birmingham Research Archive**

#### e-theses repository

This unpublished thesis/dissertation is copyright of the author and/or third parties. The intellectual property rights of the author or third parties in respect of this work are as defined by The Copyright Designs and Patents Act 1988 or as modified by any successor legislation.

Any use made of information contained in this thesis/dissertation must be in accordance with that legislation and must be properly acknowledged. Further distribution or reproduction in any format is prohibited without the permission of the copyright holder.

#### **Abstract**

There has been a remarkable increase in the use of wind power generation over the past ten years. However, costly unplanned downtimes caused by reliability issues are a problem. The most common power semiconductor failure mechanisms are bond wire lift off and solder fatigue. Failure detectors should ideally be sensitive enough to detect the early signs of failure and the progress of failure, as well as being applicable during normal operation of a three-phase converter. The junction temperature of an IGBT module has been widely used as a potential failure detector. However, restricting monitoring to purely junction temperature is highly likely to lead to false alarms as the temperature naturally changes with wind conditions. The research in this thesis explores new methods for monitoring the health of IGBTs in an operational wind turbine using a combination of thermal and electrical modelling and a lab-based three-phase converter. The main key findings to the existing knowledge are finding a new method of temperature detection, which is uncoupled with the common failure mechanisms (the bond wire lift-off and solder fatigue) in wind turbines, but also introduce a new temperature estimation method that is uncoupled with progress of the failure.

# Acknowledgements

At the completion of this work it is wonderful to reflect on all those who have given me guidance, encouragement and support in so many ways from the time it all began to this moment. I am so thrilled that writing this part has given me the opportunity to acknowledge each individual's contribution and support that has made this all possible - with all the 'ups-and-downs' of life and PhD along the way – culminating in the completion of this work.

This PhD was carried out in conjunction with the "Aeolus4Future" project. This project has provided me invaluable opportunities beyond being just a researcher: raised my personal profile, allowed me to travel across Europe and work with fabulously bright people who became friends of the best sort – deeply understanding human beings that transcend geographical boundaries and race. This period has allowed me to find myself, to build my confidence and to start treasuring my achievements. With my Aeolus4Future 'family', I have the fondest memories and adventures, learning how to enjoy every moment and feeling at home.

My sincere thanks go to the European Commission, for bringing such opportunities for a young researcher from across the world to be involved in the H2020 wind farm work project. Also to the Marie Skłodowska-Curie Foundation for giving me the astonishing opportunity to flourish and build my life, all while doing a PhD. Creating the opportunity to gather young professionals with different backgrounds to learn how best to collaborate in a project with a common goal and to see all aspects of science with a wider view and so many angles! Having such a very different background to the others led me to expand my horizons of thought and be more flexible in my imagination.

My sincere thanks and appreciation goes to Pietro Tricoli, Hassan Hemida and Professor Lambis Banitopolous for having such trust when I was appointed to be part of Aelous4Future project; for being their PhD student and thanks for your patience and support and advice to grow my academic skills to become a better and professional researcher. Thanks for providing guidance and support from the first to the last moment. My thanks forever for having me as part of your research project which offered an opportunity for me to become familiar with world-renowned professors in wind and structure engineering across Europe.

I would like to share my regard individually with the astonishing and remarkable Aelous4Future family! Mirjana, Ana, Gonçalo, Gabriel, Rahim, Milan, Mohammad Reza, Andreu, Ali and Cansev. All of you will always be in my mind! I cannot wait to have more and more adventures with you - the most welcoming, happy and cheerful family ever! My mind is full of happy travelling and joy with you all and thanks for sharing your cultures and your interests with me! Full of emotion, energy and creative - my 'young candy brother' Giulio - thanks for being so amazing to your "bella Rana verde"! From the first moment that you picked me up from Birmingham International airport where my journey started and to now, then to our future — a sibling relative for ever!

My great thanks to my University of Birmingham family, my beloved friends in Civil engineering; my full-of-peace (and always with nice smile) Michaela, my calm friend Nick, adventurous Rafael, traveller Nafsika, Danial, Fred, Simon, Racheal and Steffi. Thanks for being my company and making my days!

To the most friendly environmental railway group, 'BCRRE'! Thanks for having me as part of your group, your close family. My great thanks to Felix, Stuart and Clive for being so caring to all of us! Thanks for including me in loco challenge too, giving me opportunity to build something with a tough deadline for a real locomotive competition. It was a joy to be with a group of lovely friends, smart Ivan and disciplined, lovely Heather. Thanks for being so amazing all of you from the Gisbert Kapp entrance door Mandy, with a fresh 'good morning' every day, full of energy Nadeen and kind Jenny to my friends in the research group who always made me feel I was at home while home is too far away!

My generous, kind and understanding friends Dela and Edd. Dela thanks for always sending me your best wishes! Easy going Dena, cute Tingyu, friendly Krishnan, Silivia and Chris, Dave, Rory, hard worker Zhongbei, Graeme and Sarah, Tricky Tauj and Rhys. Thanks to Mani for all lunch gathering and never offering me his salted popcorn, but cheering me up always! Louis the best host of New Year parties and thanks to the best lab technician in the world Adnan – for all the drilling and making of wooden boards for me in the lab. Thanks for caring about us and "Rana if you need anything just tell me".

The last but certainly not least, my thanks goes to the genuine and generous friend Paul. Paul – thanks for being so patient, kind and supportive for all of us. Thanks for all of your invaluable being and empowering me for this work. Thanks for teaching me to find happiness when making others happy; I always looked forward to our late afternoon tea times!

I wish to express my gratitude to my new senior colleagues Andrew McGordon, Andy Moore and Darren Hughes at WMG, University of Warwick, and of course, thanks a lot Andy for becoming one of my best friends, which is a great honour. The kind support and understanding of you all, has made it easier for me to handle the difficulty of being involved in such an amazing project in WMG and concurrently finalizing the last stage of my PhD. Acknowledgements to all my lovely friends in WMG for being so fabulous and for cheering me onwards.

My most love and regards goes to the best mother in the world, the best of my role models ever — who teaches me how to be committed, perseverant, ambitious, reliable and responsible. My mum has a fundamental role and shares in this and other achievements. My family, Safa, Ata and father: thanks for being always with me although you are so far from me.

مادری دارم بهتر از برگ درخت به آرامش آب و به زیبایی یاسی در خواب می شود وصفش کرد به شکوه یک کوه به درختی لب رود مادرم روزگارت پر نور

#### Notation

| $\Delta T_j$       | Temperature variations                      |

|--------------------|---------------------------------------------|

| $C_{GC}$           | Miller capacitance (gate to collector)      |

| $C_{GE}$           | Gate capacitance (gate to emitter)          |

| I <sub>C</sub>     | Collector current                           |

| $L_S$              | Stator inductance                           |

| P                  | Probability                                 |

| R <sub>on</sub>    | On resistance of IGBT                       |

| R(t)               | Reliability (over period of time <i>t</i> ) |

| $R_{j\_c,th}$      | Junction-to-case thermal resistance         |

| $R_s$              | Stator resistance                           |

| $t_{d,on}$         | Switching on delay time                     |

| $t_{off}$          | Switching off time                          |

| $t_{d,off}$        | Switching off delay time                    |

| $t_{on}$           | Switching on time                           |

| $t_r$              | Rise time                                   |

| $t_f$              | Fall time                                   |

| $T_C$              | Case temperature                            |

| $T_H$              | Heatsink temperature                        |

| $T_j$              | Junction temperature                        |

| $T_m$              | Maximum junction temperature                |

| $T_{j,max}$        | Maximum junction temperature                |

| V <sub>CE,on</sub> | Collector-emitter voltage when IGBT is on   |

| $V_{dep}$          | Depletion layer                             |

| $V_{GE}$           | Gate-emitter voltage                        |

| $V_{GP}$           | Voltage level of Miller plateau             |

| $V_d$              | Drift region voltage drop                   |

# Acronyms

| ALC  | Aluminium corrosion                    |

|------|----------------------------------------|

| BWLO | Bond wire lift off                     |

| CM   | Condition monitoring                   |

| CMS  | Condition monitoring system            |

| DCB  | Direct copper bonded                   |

| DFIG | Direct fed induction motor             |

| ETDS | Electrical train drive system          |

| FOC  | Field oriented control                 |

| GSc  | Grid-side controller                   |

| GSC  | Grid-side converter                    |

| IGBT | Insulated gate bipolar transistor      |

| MPPT | Maximum power point tracking           |

| MTTR | Mean time to repair                    |

| MTTF | Mean time to failure                   |

| MTBF | Mean time between failures             |

| PI   | Proportional-integral                  |

| PMSG | Permanent magnet synchronous generator |

| PMSM | Permanent magnet synchronous machine   |

| PWM  | Pulse width modulation                 |

| RPM  | Revolutions per minute                 |

| RSc  | Rotor-side controller                  |

| RSC  | Rotot-side converter                   |

| SF   | Solder fatigue                         |

| SEGR | Single Event Gate Rupture              |

| TDDB | Time-Dependent Dielectric Breakdown    |

| TSR  | Tip speed ratio                        |

| WT   | Wind turbine                           |

# Original research articles

- 1. **R. Moeini**, P. Tricoli, H. Hemida and C. Baniotopoulos, "Effect of wind speed variations on accuracy of healthy monitoring system used in power electronic converter of wind turbines". **In preparation.**

- 2. **R. Moeini**, M. Entezami, M. Ratkovac, P. Tricoli, H. Hemida, R. Hoeffer and C. Baniotopoulos, "*Perspectives on condition monitoring techniques of wind turbines*". Journal of wind engineering, Aug 2018, DOI:10.1177/0309524X18807028.

- 3. **R. Moeini**, P. Tricoli, H. Hemida and C. Baniotopoulos, "Increasing the reliability of wind turbines using condition monitoring of semiconductor devices: a review". IET renewable power generation journal, Nov 2017.

- 4. S. Daliento, A. Chouder, P. Guerriero, A. Massi Pavan, A. Mellit, **R. Moeini**, and P. Tricoli, "Monitoring, Diagnosis, and Power Forecasting for Photovoltaic Fields: A Review". Inter Journal of Photoenergy, Jan 2017.

#### **Contributions in conference proceedings**

- 1. **R. Moeini,** P. Weston, T-Q. Dinh, A. McGordon, "Enhancement of Reliability in Condition Monitoring Techniques in Wind Turbines" Oct 2019, Int. ICMT conf., Italy.

- 2. **R. Moeini**, P. Tricoli, "Detection of common failure mechanism of IGBT", Loughborough, University of Loughborough, Power electro conf, UK, 2018.

- 3. **R. Moeini,** P. Tricoli, H. Hemida and C. Baniotopoulos, "Sensitivity analysis of switching electrical parameters of semiconductor devices for wind turbine converters", 6<sup>th</sup> Intern conf on clean electrical power, Jun 2017.

- 4. **R. Moeini**, P. Tricoli, H. Hemida and C. Baniotopoulos, "Wind turbines and reliability", TU1304, Winercost conf., 21-22 April 2016, Ankara.

- 5. **R. Moeini**, P. Tricoli, H. Hemida and C. Baniotopoulos, "Condition monitoring of wind turbines: a review", 1<sup>st</sup> Intern, Winercost conf., 21-22 April 2017, Coimbra, Portugal.

- 6. **R. Moeini**, H. Hemida and C. Baniotopoulos, "Switching characteristics of IGBT as the initial failure indicator: A case study", 18 May 2017, CESARE'17, Dead Sea, Jordan.

- 7. **R. Moeini**, P. Tricoli, H. Hemida and C. Baniotopoulos, "Increasing the reliability of wind turbines using condition monitoring of semiconductor devices: a review", IET, RPG conf., Sept. 2016, London, UK.

- 8. **R. Moeini**, P. Tricoli, H. Hemida and C. Baniotopoulos, "Early failure detection of BWLO in A Semiconductor component of an operation AL three-phase converter", 2<sup>nd</sup> Intern Winercost and Aeolus4Future conf., March 2018, Catanzaro, Italy.

# List of figures

| Figure 1.1: The cumulative growth of wind power capacity in Europe [3]                                  | 1    |

|---------------------------------------------------------------------------------------------------------|------|

| Figure 1.2: Renewable power capacity investments in Europe in 2018 [3]                                  | 2    |

| Figure 1.3: Financing costs of an offshore farm in 2015 [5], in permission to use the figure            | 2    |

| Figure 1.4: Statistical figures for overall failure rates for 350 WTs [8], in permission to use the fig | gure |

| (Optimus project)                                                                                       | 4    |

| Figure 1.5: Statistical figures of overall downtime for 350 WTs [8], in permission to use the fig       | gure |

| (Optimus project)                                                                                       | 4    |

| Figure 1.6: Distribution of electrical component failures in a WT electrical drive train system [9]     | 5    |

| Figure 2.1: A horizontal axis WT (left) and schematic of the turbine's blade assembly and nacelle (ri   | ght) |

| [3]                                                                                                     | 12   |

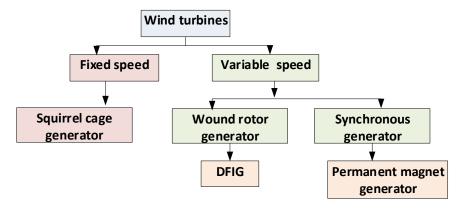

| Figure 2.2: Most common classification of WT according to their generator types                         | 12   |

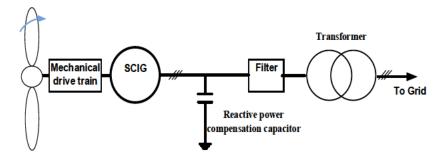

| Figure 2.3: Diagram of fixed-speed WTs, using SCIG                                                      | 13   |

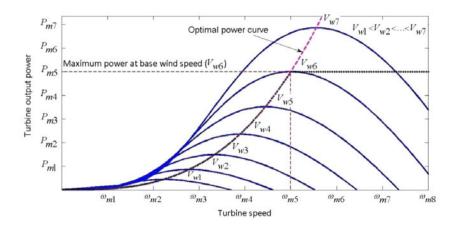

| Figure 2.4: Power control in different range of wind speed [7]                                          | 14   |

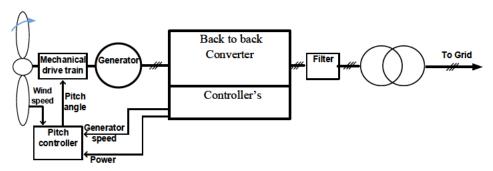

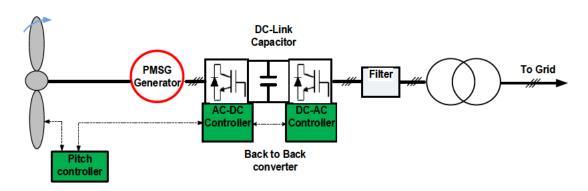

| Figure 2.5: Simplified block diagram of variable speed WTs including back-back converter                | 15   |

| Figure 2.6: Diagram of a variable speed WT with a DFIG                                                  | 16   |

| Figure 2.7: Diagram of a variable speed WT with a PMSG                                                  | 17   |

| Figure 2.8: An N-channel IGBT equivalent circuit                                                        | 18   |

| Figure 2.9: A 3-D view (top-left), cross section of a typical IGBT module (bottom-left) and IGBT la     | yers |

| (top-right) [24]                                                                                        | 18   |

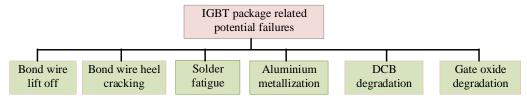

| Figure 2.10: Common failure mechanisms of the IGBT                                                      | 20   |

| Figure 2.11: Three major regions facing thermo-mechanical failures                                      | 21   |

| Figure 2.12: Initial crack at the heel of bond wires [46]                                               | 23   |

| Figure 2.13: Examples of bond wire damage [48]                                                          | 23   |

| Figure 2.14: Bathtub curve                                                                              | 25   |

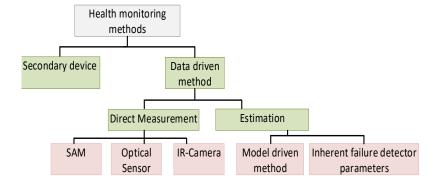

| Figure 3.1: Health condition monitoring techniques for IGBT                                             | 34   |

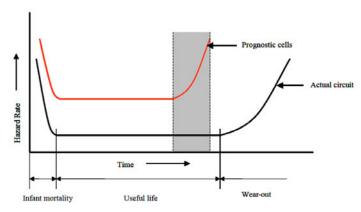

| Figure 3.2: The idealized 'bathtub' reliability curves for a test circuit and prognostic cell [12]      | 35   |

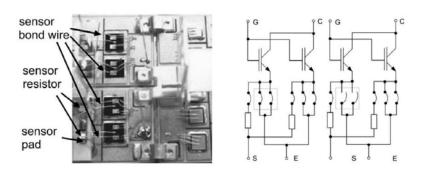

| Figure 3.3: Emitter bond wire lift-off [18]                                                             | 36   |

| Figure 3.4: The example of embedded sensor for monitoring of bond wire lift-off [19]                    | 37   |

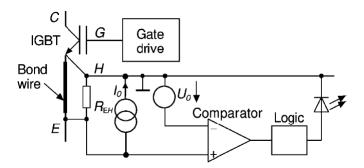

| Figure 3.5: Variations of IG during the progress of bond wire lift off [40]                             | 41   |

| Figure 3.6: Variations of VGE in the presence of BWLO [46]                                              | 42   |

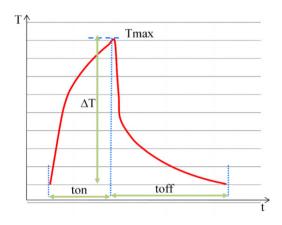

| Figure 3.7: △Tj during a power cycle [68]                                                               | 45   |

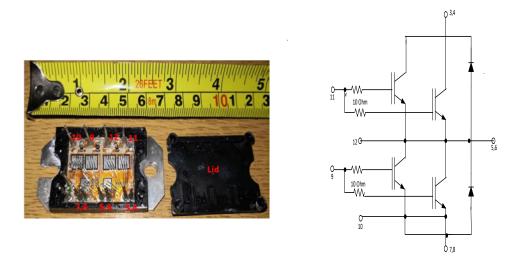

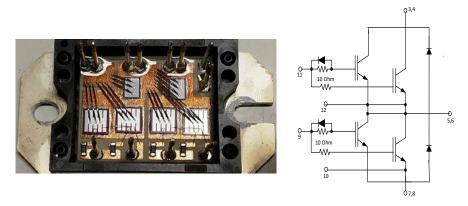

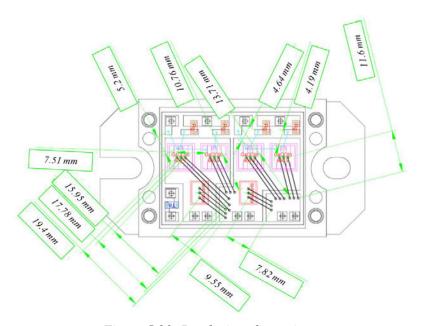

| Figure 4.1: (a) The physical half bridge IGBT module; (b) Electrical diagram of the IGBT module         | 61   |

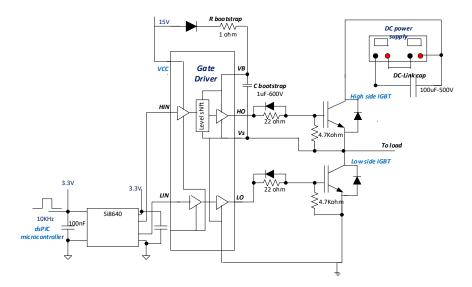

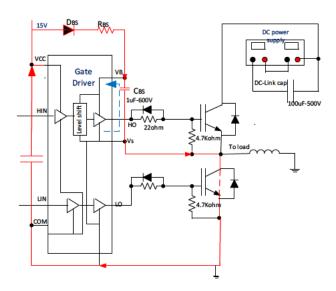

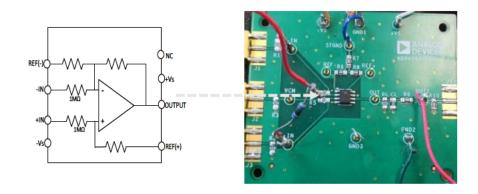

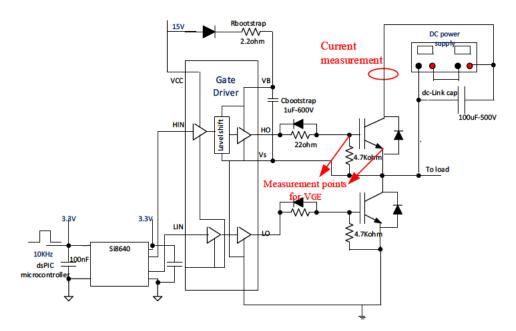

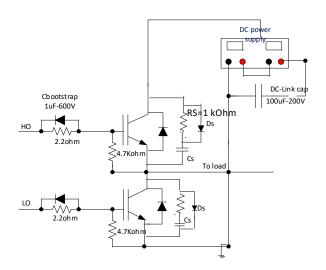

| Figure 4.2: Schematic of the designed gate driver                                                       | 62   |

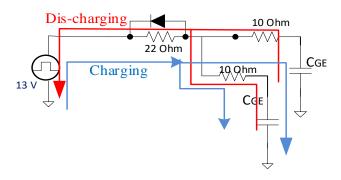

| Figure 4.3: Equivalent circuit of total resistors through the gate terminal                             | 63   |

| Figure 4.4: Charge and discharge of bootstrap capacitor (CBS)                                         | 64    |

|-------------------------------------------------------------------------------------------------------|-------|

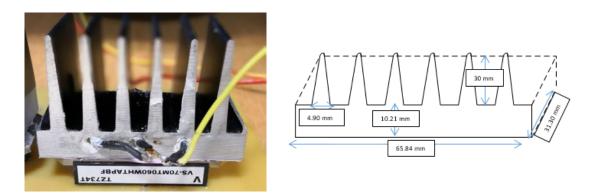

| Figure 4.5: Heatsink: (a) Controllable temperature; (b) dimensions                                    | 66    |

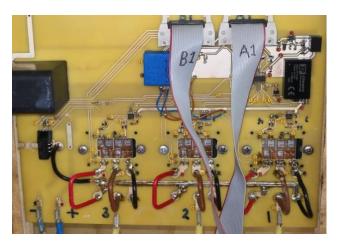

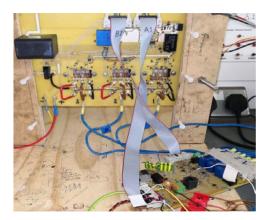

| Figure 4.6: Custom-made three-phase converter power board, front side                                 | 66    |

| Figure 4.7: Controller signals of power board for the three-phase converter                           | 67    |

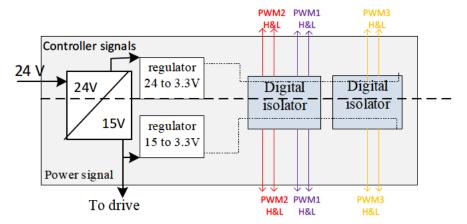

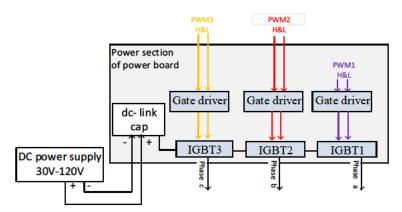

| Figure 4.8: Block diagram of power section of the power board                                         | 67    |

| Figure 4.9: Power converter board                                                                     | 68    |

| Figure 4.10: Controller board with the microcontroller                                                | 69    |

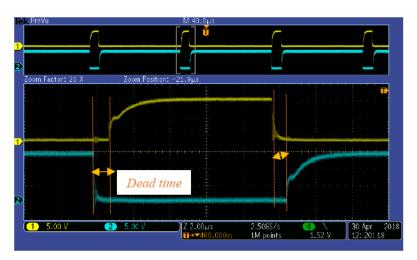

| Figure 4.11: Dead time between high side and low side of half bridge                                  | 69    |

| Figure 4.12: Phase current transducer                                                                 | 70    |

| Figure 4.13: DC-link voltage measurement circuit                                                      | 71    |

| Figure 4.14: Electrical schematic of the wiring connection of encoder to the microcontroller          | 71    |

| Figure 4.15: Encoder coupled to rotor shaft of the permanent magnet generator                         | 72    |

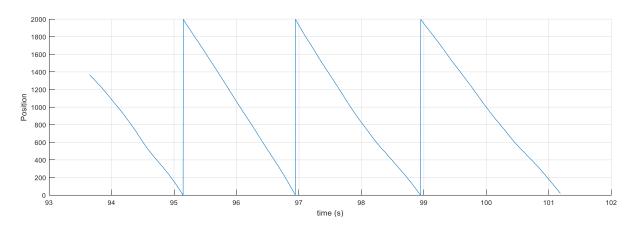

| Figure 4.16: Position (angle count 0-1999 for each rotation) vs time                                  | 72    |

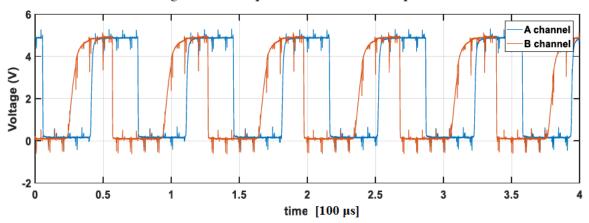

| Figure 4.17: Output of the encoder after opto-isolators                                               | 73    |

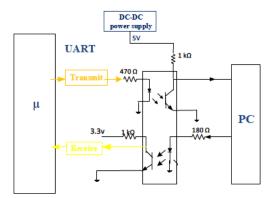

| Figure 4.18: Electrical circuit of UART and relevant electrical connections                           | 73    |

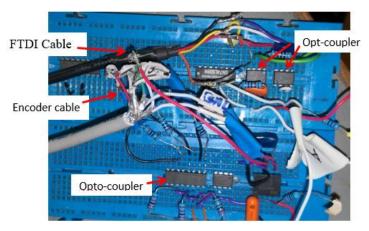

| Figure 4.19: UART and encoder circuit set up                                                          | 74    |

| Figure 4.20: Integrated display of UART output                                                        | 74    |

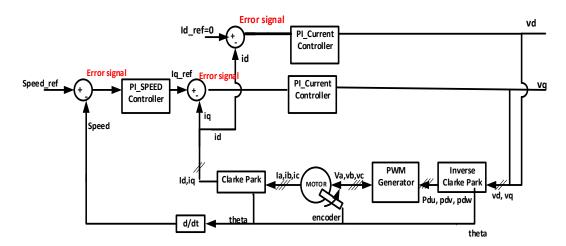

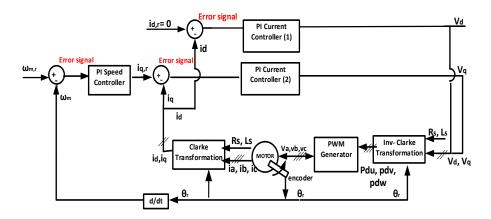

| Figure 4.21: Controller block used in the generator side converter                                    | 75    |

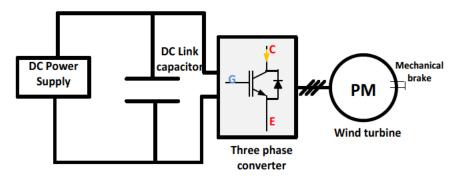

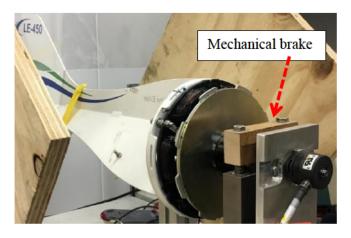

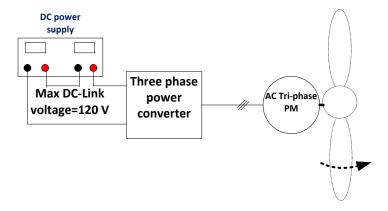

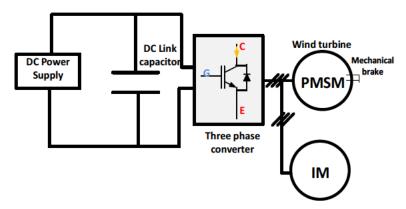

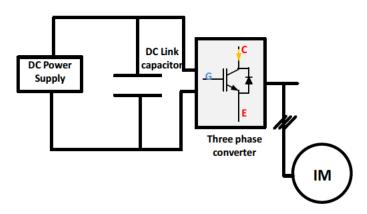

| Figure 4.22: The test set up                                                                          | 77    |

| Figure 4.23: The mechanical braking system                                                            | 77    |

| Figure 4.24: Three-phase outputs feeding a static load                                                | 78    |

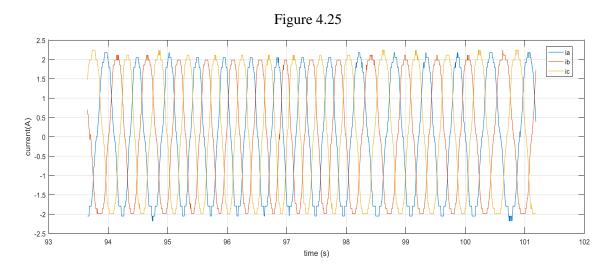

| Figure 4.25: Validation of the current controllers                                                    | 79    |

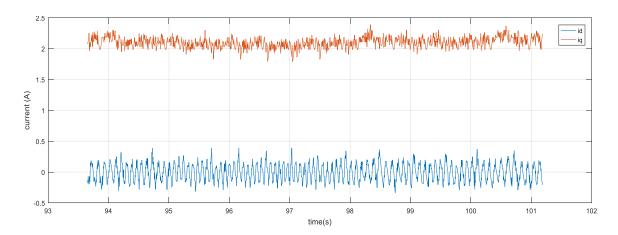

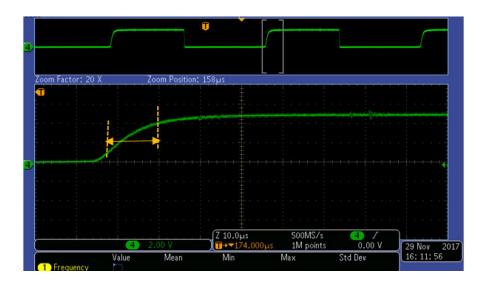

| Figure 4.26: The rise time of the current controller                                                  | 79    |

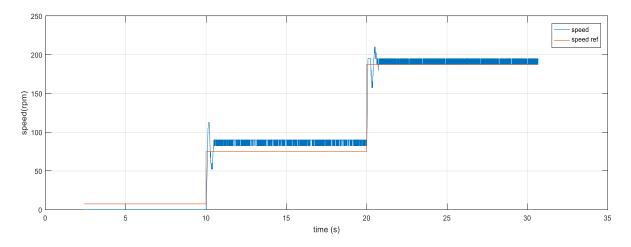

| Figure 4.27: Validation of the speed controller                                                       | 80    |

| Figure 5.1: Electrical diagram and power bond wires of the IGBT                                       | 84    |

| Figure 5.2: VCE, on measurement circuit                                                               | 86    |

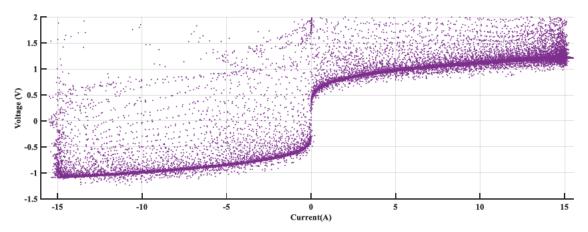

| Figure 5.3: VCE, on versus iC under an inductive load                                                 | 86    |

| Figure 5.4: The circuit used for calibration of VCE, on (a) Current path, high side on; (b) Current J | path, |

| high side off                                                                                         | 87    |

| Figure 5.5: Parallel resistors inserted inside the heatsink                                           | 87    |

| Figure 5.6: Measurement points                                                                        | 90    |

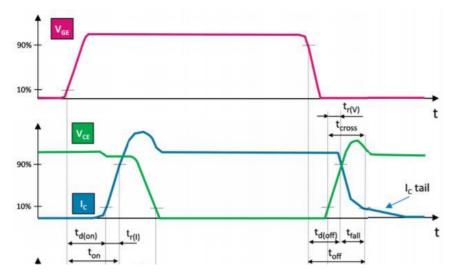

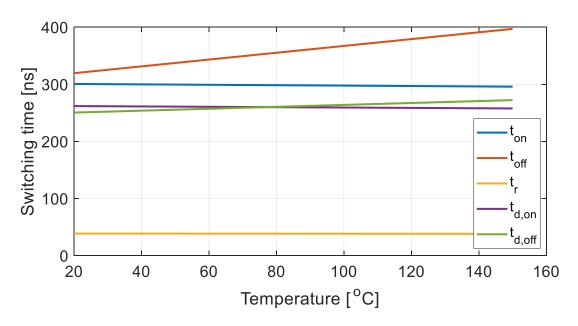

| Figure 5.7: Switching time parameters [15]                                                            | 96    |

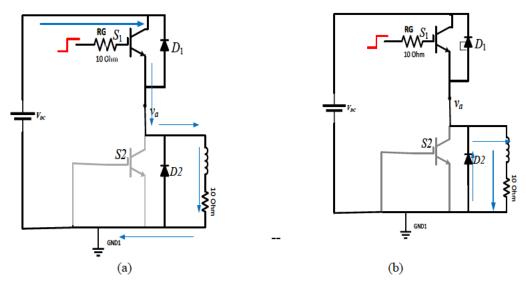

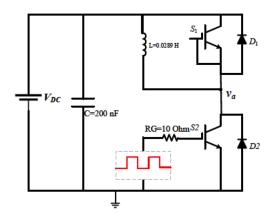

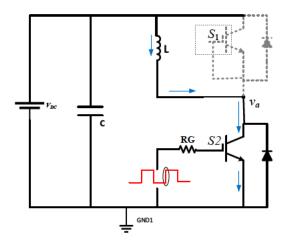

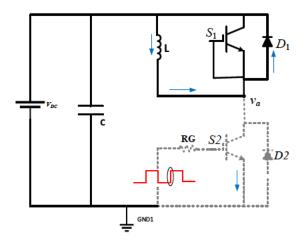

| Figure 5.8: Electrical schematic of double pulse test                                                 | 97    |

| Figure 5.9: Stage.1: the inductor current ramps up by the DC power supply                             | 97    |

| Figure 5.10: Stage.2: current path through high side the freewheeling diode and inductor              | 98    |

| Figure 5.11: Stage.3: discharge the inductor to the low side IGBT                                     | 98    |

| Figure 5.12: Stage.4: current circulation in the inductive loop                       | 98  |

|---------------------------------------------------------------------------------------|-----|

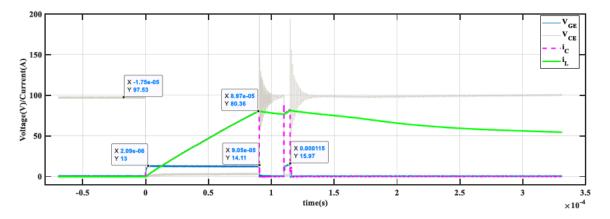

| Figure 5.13: Signal outputs seen during a double pulse test                           | 99  |

| Figure 5.14: Example of double pulse test output                                      | 99  |

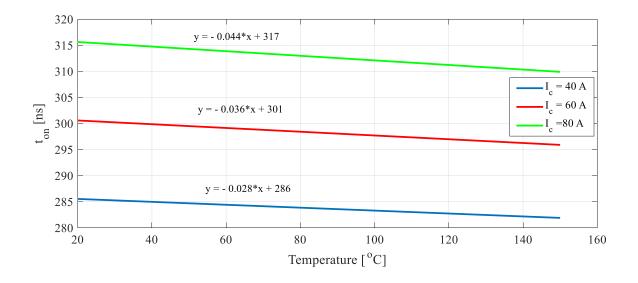

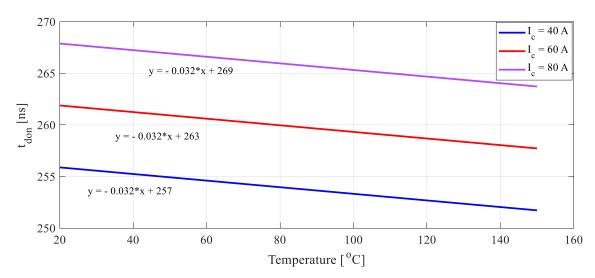

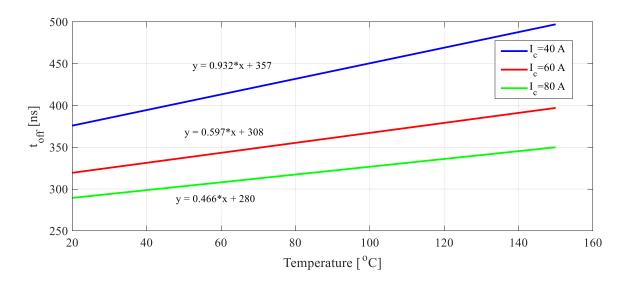

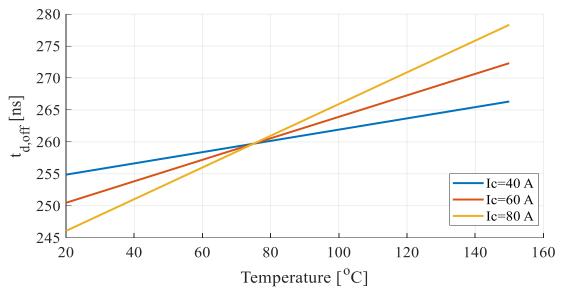

| Figure 5.15: ton versus temperature at different load currents                        | 100 |

| Figure 5.16: td, on versus temperature at different load currents                     | 101 |

| Figure 5.17: toff versus temperature at 3 different load currents                     | 101 |

| Figure 5.18: td, off versus temperature at 3 different load currents                  | 102 |

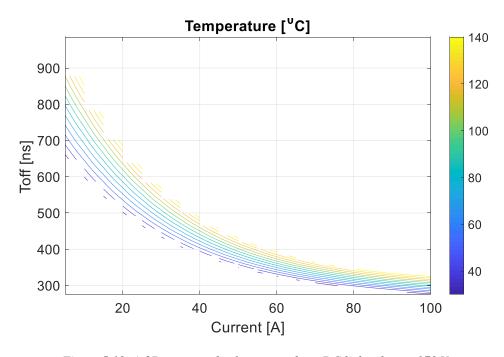

| Figure 5.19: A 2D contour plot for toff under a DC link voltage of 70 V               | 103 |

| Figure 5.20: BWLO                                                                     | 104 |

| Figure 5.21: Detection of BWLO                                                        | 106 |

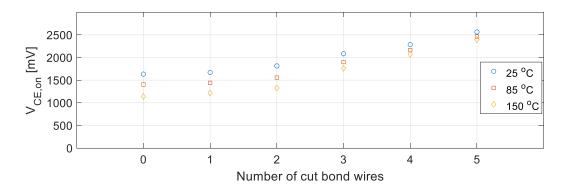

| Figure 5.22: Sensitivity of VCE, on to BWLO at 85 A                                   | 106 |

| Figure 5.23: The test set up                                                          | 107 |

| Figure 5.24: Induction machine in parallel with PMSM                                  | 108 |

| Figure 5.25: Induction machine only                                                   | 108 |

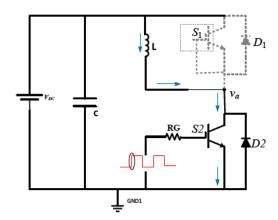

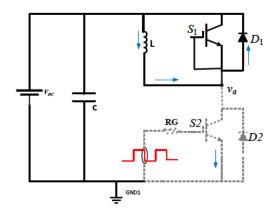

| Figure 5.26: Measured points to measure VGE and ic                                    | 109 |

| Figure 5.27: 90% and 10% of ic                                                        | 110 |

| Figure 5.28: 10 % VGE, 10% and 90% of ic                                              | 110 |

| Figure 5.29: 90% VGE, 10% and 90% of ic                                               | 110 |

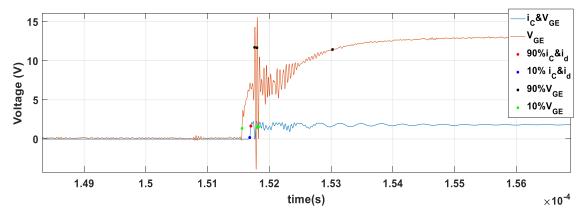

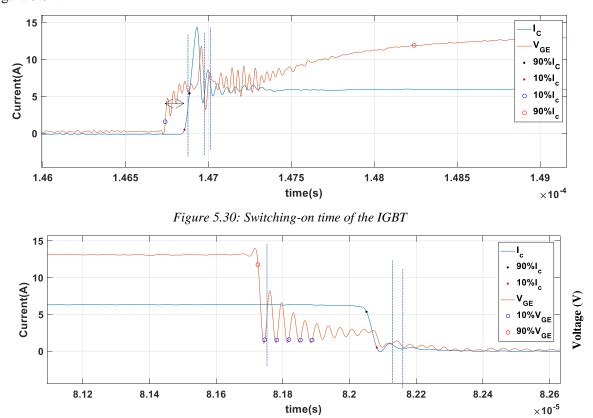

| Figure 5.30: Switching-on time of the IGBT                                            | 111 |

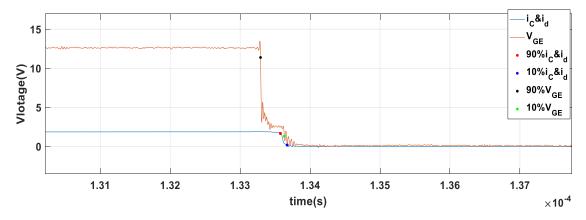

| Figure 5.31: Switching-off time of the IGBT                                           | 111 |

| Figure 5.32: Circuit schematic including the snubber                                  | 112 |

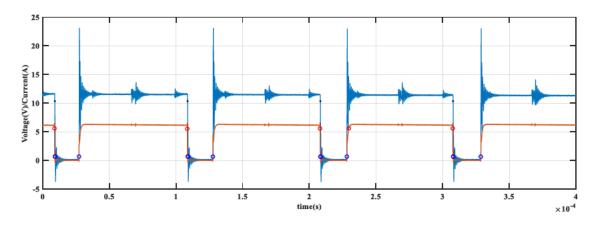

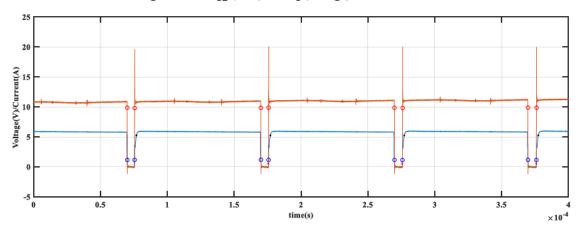

| Figure 5.33: VGE (blue) and IC (orange) without snubber                               | 113 |

| Figure 5.34: VGE (blue) and IC (orange) with snubber                                  | 113 |

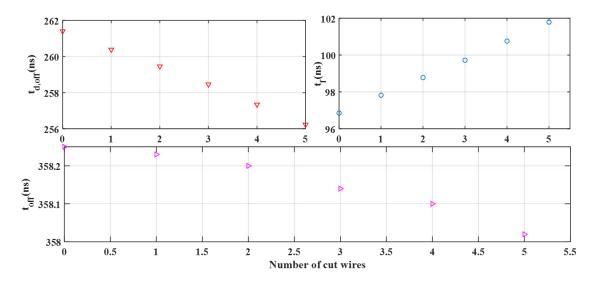

| Figure 5.35: Variations of td, off, tf and toff with the number of cut wires          | 115 |

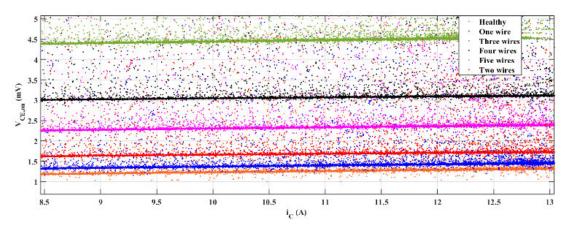

| Figure 5.36: VCE, on versus ic in different level of healthy status                   | 115 |

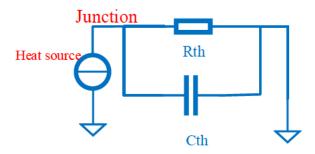

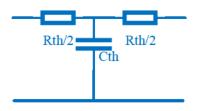

| Figure 6.1: Foster model                                                              | 119 |

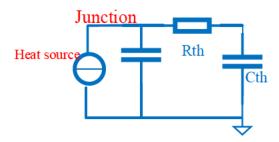

| Figure 6.2: Simple Cauer thermal network                                              | 120 |

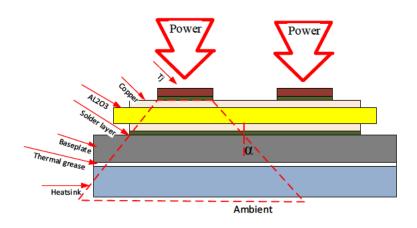

| Figure 6.3: A pyramid heat flow structure of the IGBT                                 | 122 |

| Figure 6.4: RCR model                                                                 | 123 |

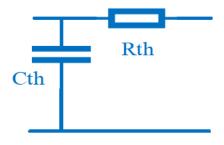

| Figure 6.5: RC model                                                                  | 123 |

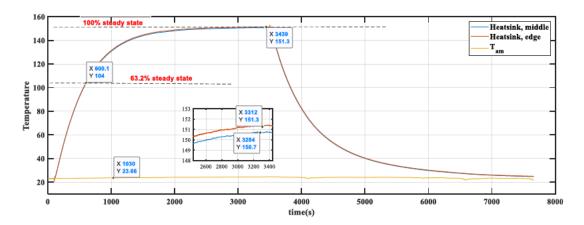

| Figure 6.6: Time constant of heatsink                                                 | 124 |

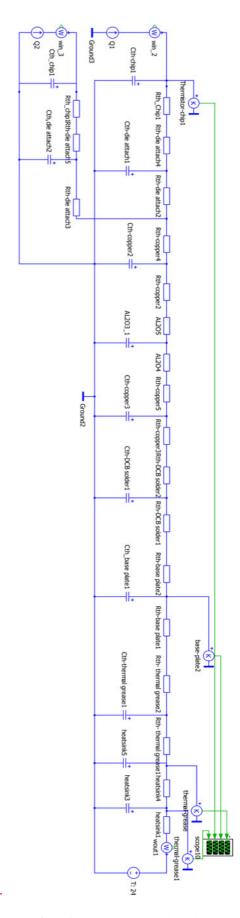

| Figure 6.7: The thermal network of the IGBT                                           | 125 |

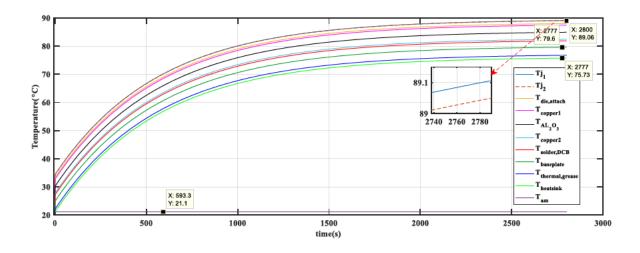

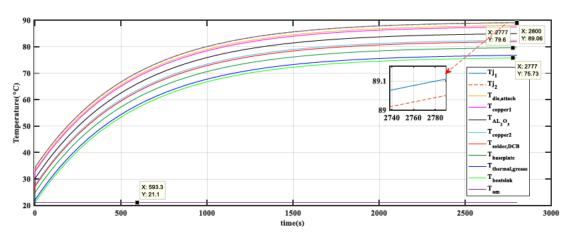

| Figure 6.8: Temperature behaviour in IGBT layers                                      | 126 |

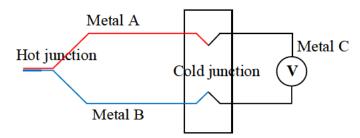

| Figure 6.9: Thermocouple Principle                                                    | 126 |

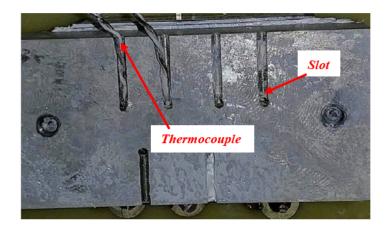

| Figure 6.10: Baseplate thermocouple arrangement (left) Heatsink thermocouples (right) | 127 |

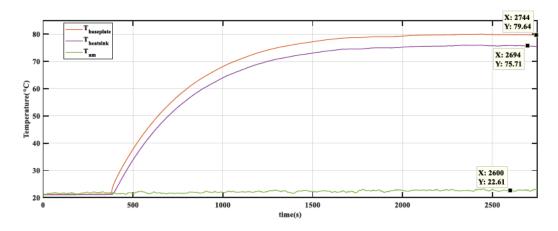

| Figure 6.11: Temperature of heatsink and baseplate                                    | 127 |

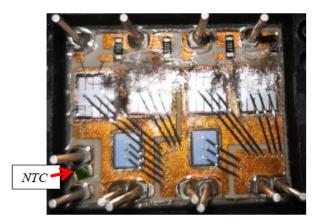

| Figure 6.12: NTC inside module                                            | 128 |

|---------------------------------------------------------------------------|-----|

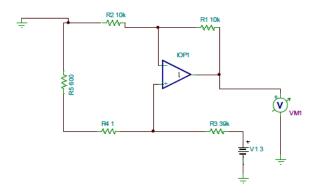

| Figure 6.13: Configuration of amplifier connected to the NTC terminals    | 128 |

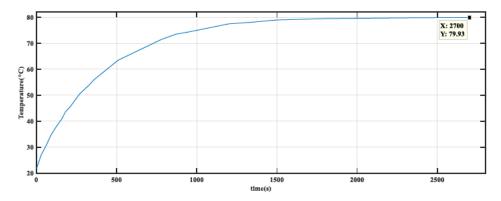

| Figure 6.14: Output of NTC temperature                                    | 129 |

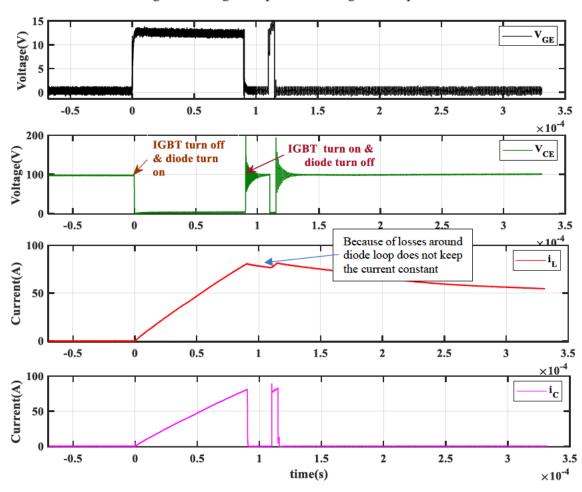

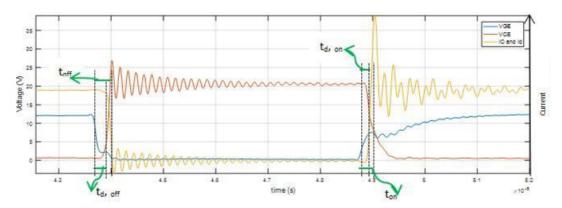

| Figure 6.15: Switching parameters of the IGBT under test                  | 129 |

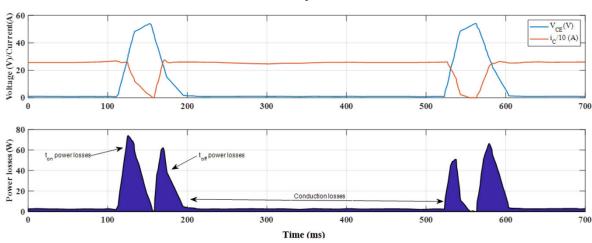

| Figure 6.16: Power losses of the IGBT under test at ambient temperature   | 131 |

| Figure 6.17: The 2D conduction energy loss look-up table                  | 133 |

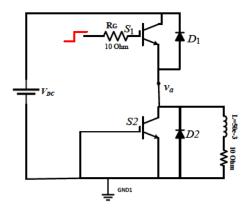

| Figure 6.18: Schematic of the test steup for calculation of power losses  | 133 |

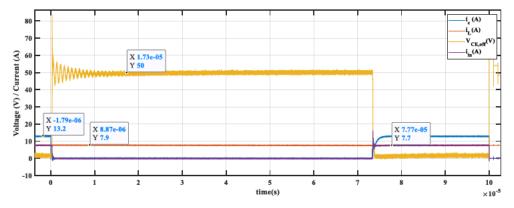

| Figure 6.19: Electrical parameters of the IGBT to find conduction loss    | 134 |

| Figure 6.20: Electrical power loss of the IGBT to find switching loss     | 134 |

| Figure 6.21: Cumulative power loss                                        | 135 |

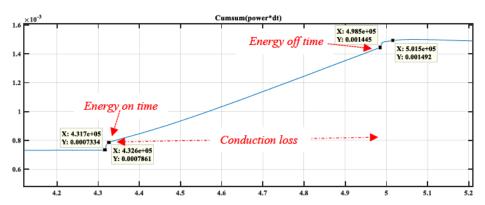

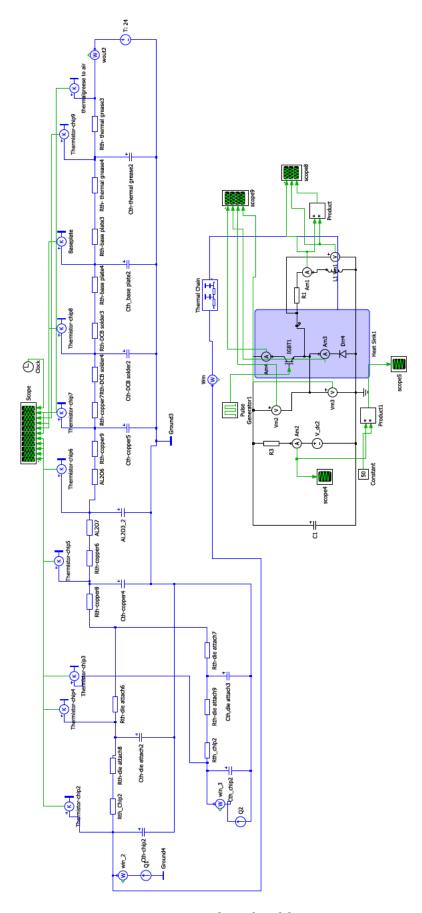

| Figure 6.22: Thermo-electric model of IGBT                                | 136 |

| Figure 6.23: Switching loss of the IGBT added to PLECS model              | 137 |

| Figure 6.24: Temperature rise in DCB silicon and baseplate layers         | 137 |

| Figure 6.25: Emulating solder fatigue by adding thermal pad               | 138 |

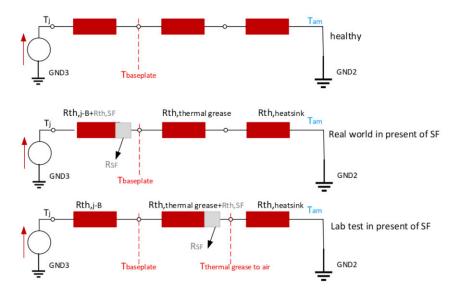

| Figure 6.26: Change in thermal path for IGBT in the presence of SF        | 139 |

| Figure 6.27: Thermal model                                                | 141 |

| Figure 6.28: Temperature differences against time                         | 142 |

| Figure 6.29: Effect of SF on VCE, on                                      | 143 |

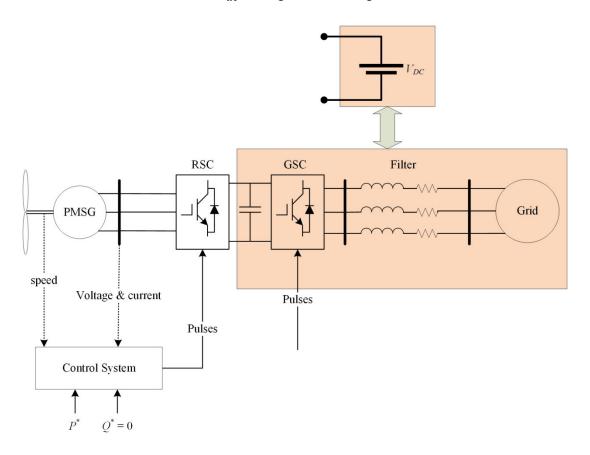

| Figure 7.1: Diagram of back-to-back converter and controllers             | 145 |

| Figure 7.2: Schematic representation of a 1-pole three-phase PMSM [1]     | 146 |

| Figure 7.3: Mechanical power vs rotor rotational speed                    | 147 |

| Figure 7.4: Diagram of pitch controller (and MPPT)                        | 148 |

| Figure 7.5: Rotor-side converter and controller diagram                   | 149 |

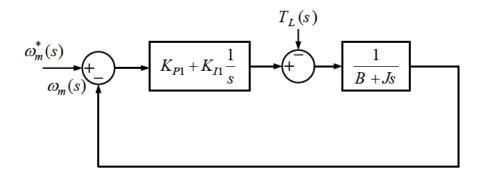

| Figure 7.6: Speed controller block diagram                                | 150 |

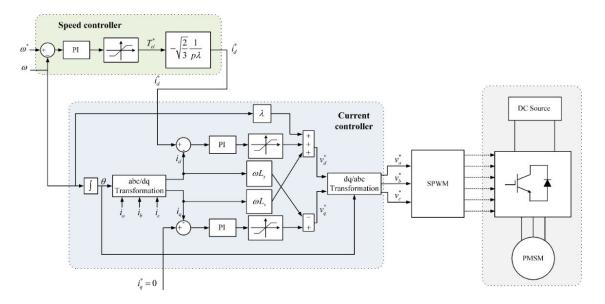

| Figure 7.7: d-q axes current and speed controller                         | 151 |

| Figure 7.8: d-q axes current controller and PLL for grid side controller  | 153 |

| Figure 7.9: Rotor-side diagram and controllers                            | 154 |

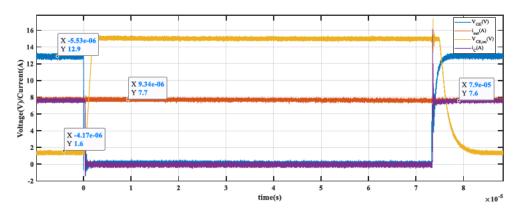

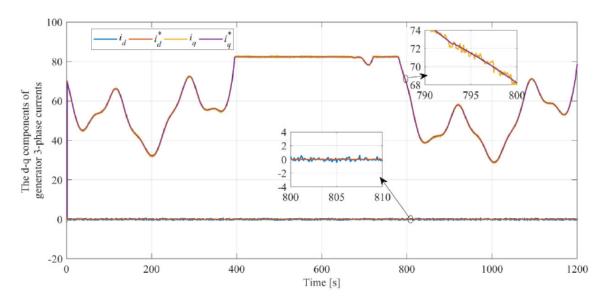

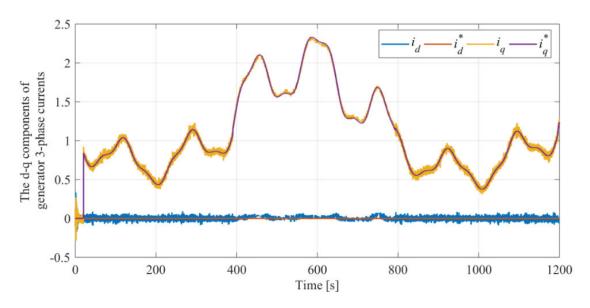

| Figure 7.10: Validation of current controller                             | 155 |

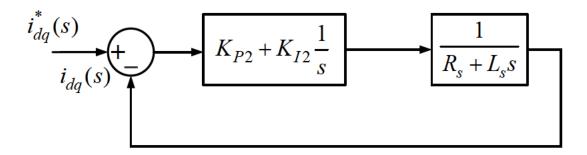

| Figure 7.11: Block diagram of current controller                          | 155 |

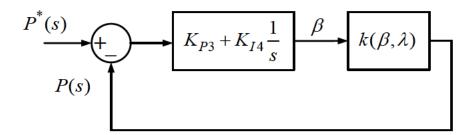

| Figure 7.12: Blade pitch controller                                       | 156 |

| Figure 7.13: Validation of blade pitch controller                         | 157 |

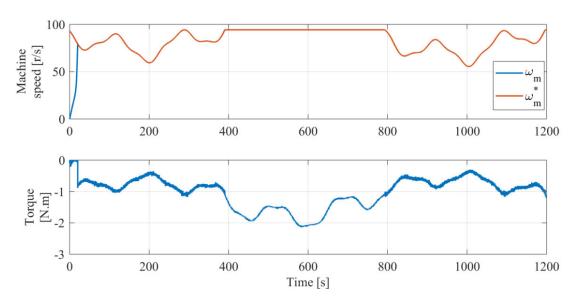

| Figure 7.14: Validation of speed controller                               | 158 |

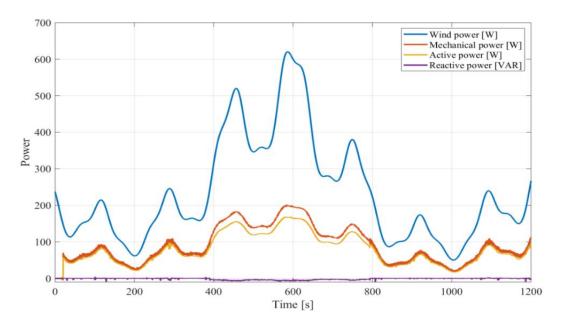

| Figure 7.15: Active and reactive power of the WT and applied wind profile | 158 |

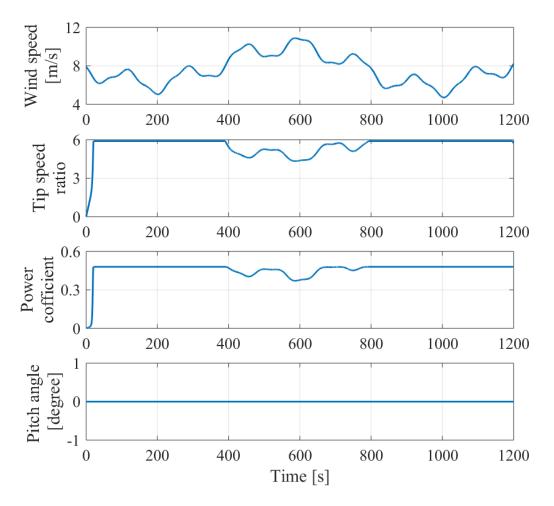

| Figure 7.16: Power coefficient and instantaneous power output of WT       | 159 |

| Figure 7.17: Line-to-line output voltages and currents                    | 160 |

| Figure 7.18: Validation of current controller                             | 161 |

|                                                                           |     |

| Figure 7.19: Validation of speed controller                                               | 162 |

|-------------------------------------------------------------------------------------------|-----|

| Figure 7.20: Active and reactive power                                                    | 162 |

| Figure 7.21: Tip speed ratio and power coefficient                                        | 163 |

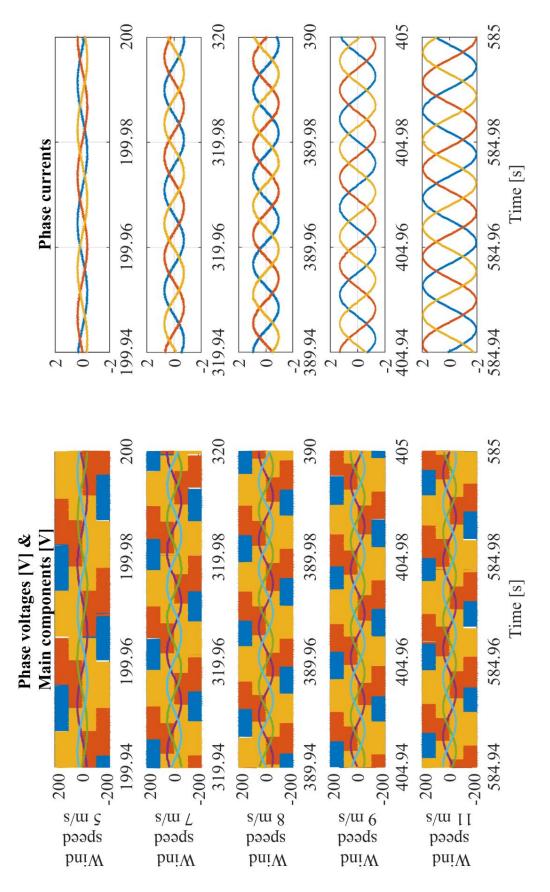

| Figure 7.22: Phase and current/voltage of converter                                       | 165 |

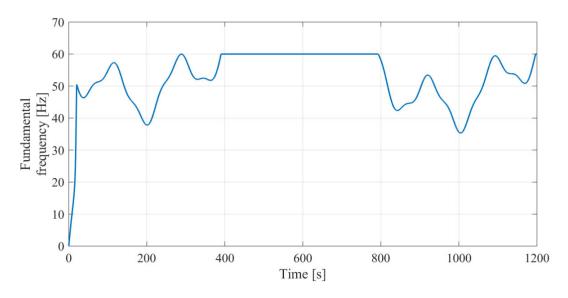

| Figure 7.23: Electrical fundamental frequency of generator                                | 166 |

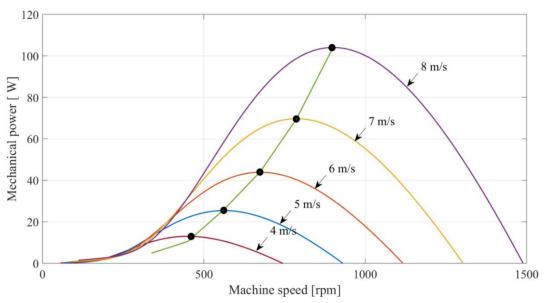

| Figure 7.24: Machine power vs machine speed                                               | 166 |

| Figure 8.1: Switching parameters of the IGBT under test                                   | 173 |

| Figure 8.2: ton, toff, tr and tf and td, on and td, off versus Tj ( $ic = 60 \text{ A}$ ) | 173 |

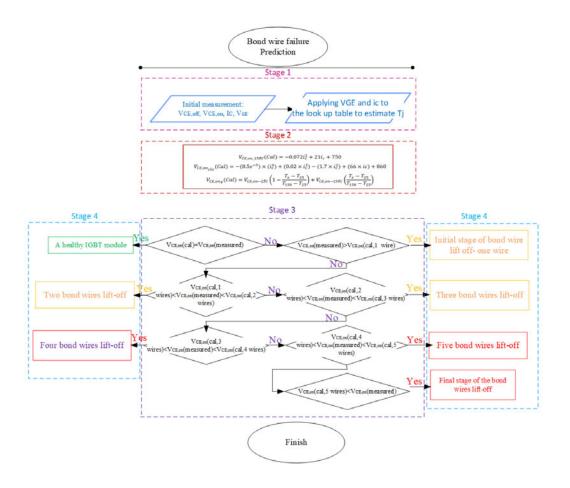

| Figure 8.3: Flowchart to detect BWLO                                                      | 176 |

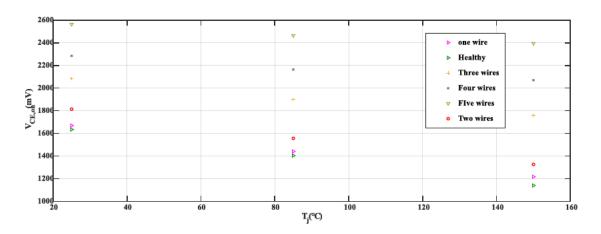

| Figure 8.4: VCE, on against number of cuting bond wires at three temperatures             | 177 |

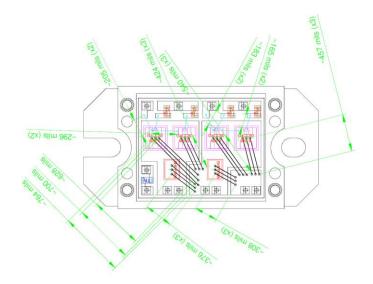

| Figure 8.5: VS-50mt060whtapbf power module                                                | 177 |

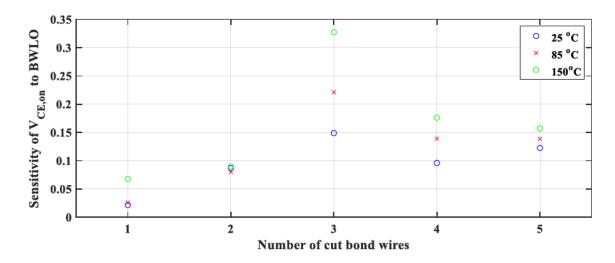

| Figure 8.6: Sensitivity of VCE, on to the progress of BWLO                                | 178 |

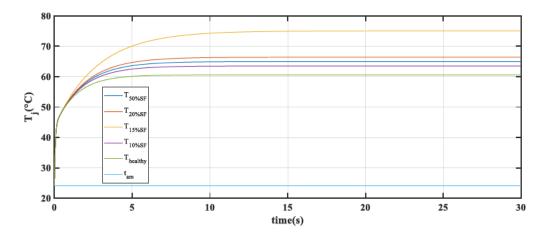

| Figure 8.7: Transient temperature rise achieved in thermal model                          | 178 |

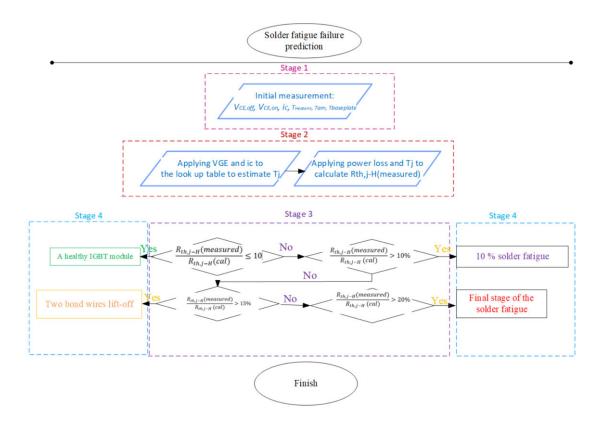

| Figure 8.8: Flowchart to detect solder fatigue                                            | 179 |

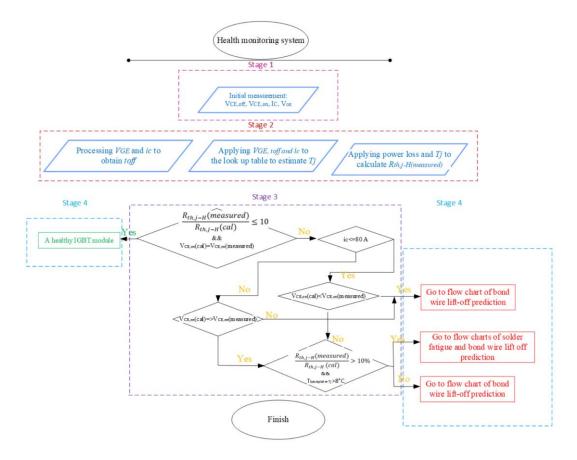

| Figure 8.9: Fowchart to detect solder fatigue and BWLO.                                   | 180 |

# List of tables

| Table 2.1: Thermal expansion coefficients for materials commonly found in IGBTs [36] | 21  |

|--------------------------------------------------------------------------------------|-----|

| Table 3.1: Comparison of different lifetime models                                   | 48  |

| Table 3.2: Comparison of failure mechanisms in IGBTs [9]                             | 48  |

| Table 3.3: Comparison of health condition monitoring methods in an IGBT              | 50  |

| Table 3.4: Failure mechanisms of IGBTs and their failure indicator parameters        | 51  |

| Table 4.1: Selected IGBT specifications                                              | 61  |

| Table 4.2: Specifications of the electric machine used in the wind turbine           | 76  |

| Table 5.1: Sensitivity of switching times to temperature (at 70V)                    | 102 |

| Table 5.2: Sensitivity of VCE, on to Tj with the progress of bond wire lift off      | 106 |

| Table 5.3: Switching times with and without snubber circuit                          | 114 |

| Table 6.1: IGBT layer dimensional properties                                         | 121 |

| Table 6.2: IGBT layer thermal characteristics                                        | 122 |

| Table 8.1: Sensitivity of toff to progress of bond wire lift off                     | 175 |

| Table 9.1: List of objectives and associated outcomes                                | 183 |

# **Contents**

| Chapter 1: Introduction                                                         | 1  |

|---------------------------------------------------------------------------------|----|

| 1.1 Motivation for this research                                                | 1  |

| 1.2 Overview of research methodology                                            | 6  |

| 1.3 Problem statement                                                           | 7  |

| 1.4 Aim of this research and objectives                                         | 7  |

| 1.5 Original research contributions                                             | 8  |

| 1.6 Thesis outline                                                              | 8  |

| 1.7 References                                                                  | 9  |

| Chapter 2: Review of condition monitoring of power converters for wind turbines | 11 |

| 2.1 Introduction                                                                | 11 |

| 2.2 Electric drive train system of a wind turbine                               | 11 |

| 2.3 Electrical drive system of wind turbines                                    | 12 |

| 2.3.1 Fixed-speed wind turbines                                                 | 12 |

| 2.3.2 Variable-speed wind turbines                                              | 13 |

| 2.4 DFIG type of wind turbine                                                   | 15 |

| 2.5 PMSG type of wind turbine                                                   | 16 |

| 2.6 IGBT module                                                                 | 17 |

| 2.7 IGBT structure                                                              | 18 |

| 2.8 Failure modes                                                               | 19 |

| 2.8.1 DCB degradation                                                           | 22 |

| 2.8.2 Gate oxide degradation                                                    | 22 |

| 2.8.3 Bond wires lift-off degradation                                           | 22 |

| 2.8.4 Solder fatigue                                                            | 24 |

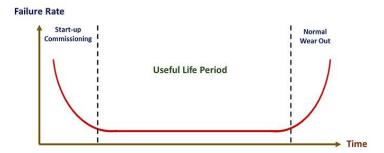

| 2.9 Reliability definition                                                      | 24 |

| 2.10 Summary                                                                    | 26 |

| 2.11 References                                                                 | 26 |

| Chapter 3: Review of failure modes of IGBT modules – mechanisms and effects     | 32 |

| 3.1 Introduction                                                                | 32 |

| 3.2 Faults and failures                                                         | 32 |

| 3.3 Health condition monitoring of IGBT                                         | 33 |

| 3.3.1 Diagnostic techniques based on secondary devices                          | 35 |

| 3.3.2 Data driven methods                                                                           | 35                   |

|-----------------------------------------------------------------------------------------------------|----------------------|

| 3.3.3 Model driven methods                                                                          | 43                   |

| 3.4 Residual lifetime prediction for IGBTs                                                          | 45                   |

| 3.5 Discussion and Summary                                                                          | 49                   |

| 3.6 References                                                                                      | 53                   |

| Chapter 4: Experimental set up                                                                      | 60                   |

| 4.1 Introduction                                                                                    | 60                   |

| 4.2 Design of the hardware                                                                          | 61                   |

| 4.2.1 IGBT under test                                                                               | 61                   |

| 4.2.2 Power section                                                                                 | 65                   |

| 4.2.3 Power circuit implementation                                                                  | 66                   |

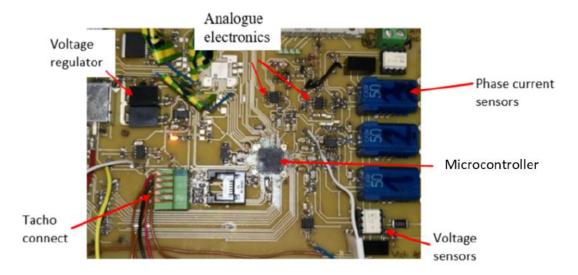

| 4.2.4 Controller board                                                                              | 68                   |

| 4.3 Load test set up                                                                                | 76                   |

| 4.4 Estimation of the parameters of the permanent magnet machine                                    | 77                   |

| 4.5 Validation of the current controller                                                            | 78                   |

| 4.6 Validation of the speed controller                                                              | 79                   |

| 4.7 Summary                                                                                         | 80                   |

| 4.8 References                                                                                      | 80                   |

| [1] R.S. Chokhawala, J. Catt; B.R. Pelly, "Gate drive considera modules", IEEE, PP. 603 – 611, 1995 |                      |

| Chapter 5: Experimental results: Bond wire lift-off                                                 | 82                   |

| 5.1 Introduction                                                                                    | 82                   |

| 5.2 Estimation of junction temperature and failure detectors                                        | 83                   |

| 5.3 Topology of interest for VCE, on as a failure detector                                          | 83                   |

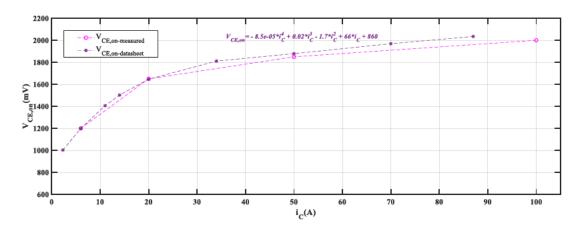

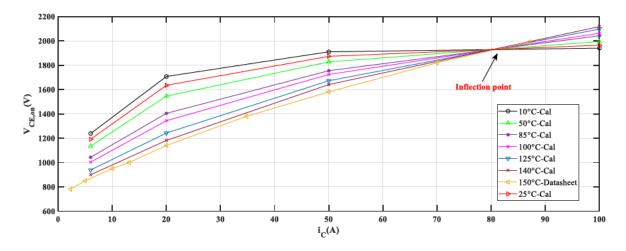

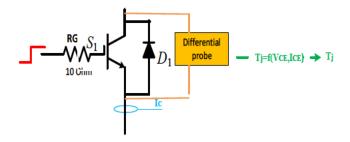

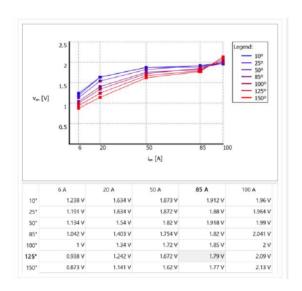

| 5.3.1 Correlation between VCE, on and temperature                                                   | 86                   |

| 5.3.2 Topology of interest to switching times                                                       | 91                   |

| 5.4 Calibration of switching times                                                                  | 96                   |

| 5.5 Results of calibration                                                                          | 100                  |

| 5.6 Emulating failure mechanisms                                                                    | 104                  |

| 5.6.1 Imposing bond wire lift-off                                                                   | 104                  |

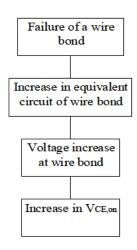

| 5.6.2 Detection of bond wire lift-off                                                               | 105                  |

| 5.6.3 Detection of BWLO using VCE, on as failure detector and toff as a                             | junction temperature |

| estimator                                                                                           | 107                  |

| 5.7 Measurement of switching time                                                | 108         |

|----------------------------------------------------------------------------------|-------------|

| 5.8 Summary                                                                      | 115         |

| 5.9 References                                                                   | 116         |

| Chapter 6: Experiment results II: Detection of solder fatigue                    | 118         |

| 6.1 Introduction                                                                 | 118         |

| 6.2 Thermal modelling of the IGBT                                                | 119         |

| 6.2.1 Foster model                                                               | 119         |

| 6.2.2 Cauer model                                                                | 120         |

| 6.2.3 Heat spreading for each layer                                              | 121         |

| 6.3 Temperature measurement/estimation of the IGBT                               | 126         |

| 6.4 Power loss calculation                                                       | 129         |

| 6.4.1 Steady state thermal analysis                                              | 132         |

| 6.4.2 Transient thermal analysis                                                 | 132         |

| 6.4.3 Power loss in experiment: switching and conduction losses                  | 133         |

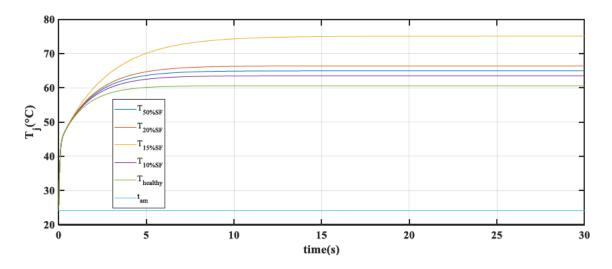

| 6.5 Detection of solder fatigue                                                  | 137         |

| 6.6 Detecting solder fatigue through monitoring VCE, on                          | 142         |

| 6.7 References                                                                   | 143         |

| Chapter 7: Numerical Modelling of the Electrical Drive Train in a Wind           | Turbine 145 |

| 7.1 Introduction                                                                 | 145         |

| 7.2 Overview of the drive train                                                  | 145         |

| 7.3 The permanent magnet synchronous generator                                   | 146         |

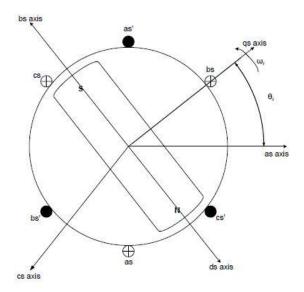

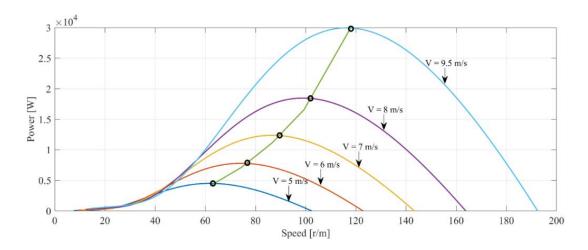

| 7.4 MPPT and pitch controller                                                    | 147         |

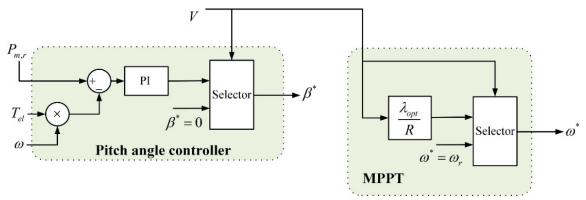

| 7.5 Pitch controller                                                             | 147         |

| 7.6 The rotor-side controller                                                    | 148         |

| 7.6.1 Rotor-side controller                                                      | 150         |

| 7.6.2 Rotor-side converter and controller rotor-side converter                   | 150         |

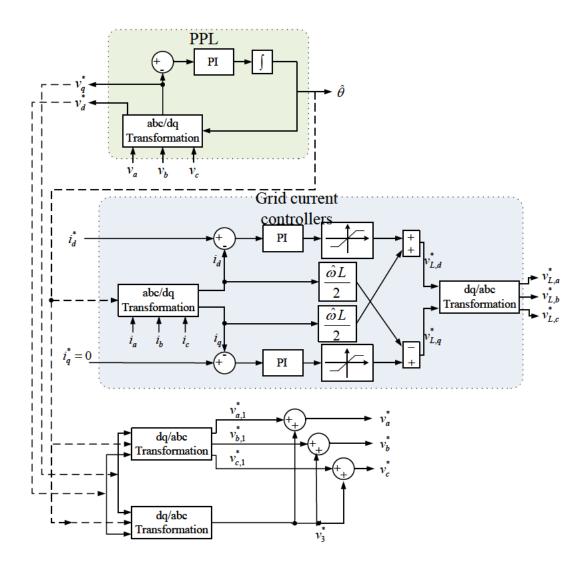

| 7.7 GSC and GSc                                                                  | 152         |

| 7.8 Modelling of RSC for a large wind turbine with pitch controller              | 153         |

| 7.8.1 Output of controllers                                                      | 155         |

| 7.9 Modelling of RSC and RSc without pitch angle for a micro wind turbine        | 161         |

| 7.9.1 Validation of rotor side controller without pitch angle                    |             |

| 7.9.1 Validation of rotor side controller without pitch angle                    | 161         |

| 7.10 Effect of wind condition on the efficiency and reliability of wind turbines |             |

| Chapter 8: Discussion and conclusion                     | 170 |

|----------------------------------------------------------|-----|

| 8.1 Research achievement and project specific            | 170 |

| 8.2 Modelling analysis                                   | 174 |

| 8.3 Results justifications and critical analysis of data | 175 |

| 8.4 Support findings                                     | 176 |

| 8.5 Conclusion and summary                               | 180 |

| Chapter 9: Thesis conclusions                            | 182 |

| 9.1 Final original contribution                          | 182 |

| 9.2 Key findings for detecting BWLO and SF               | 184 |

| 9.3 Future purpose and accountability                    | 185 |

# **Chapter 1: Introduction**

#### 1.1 Motivation for this research

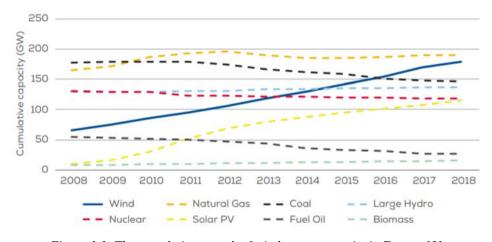

Wind power is ranked first as a source of power generation amongst renewable power sources [1]. In 2018, wind power generation accounted for 14% out of 362 TWh total generated energy in the EU [2]. Investment in wind power is growing annually as shown in Figure 1.1. A majority (63%) of new power capacity investment is allocated to wind power, with 160 GW onshore wind turbines (WT) and 18.5 GW offshore WT, with investments of, respectively,  $\in$ 16.3 bn and  $\in$ 10.3 bn [2]. The sharing of investment for the new installation capacity is shown in Figure 1.2.

Figure 1.1: The cumulative growth of wind power capacity in Europe [3]

The next highest power capacity investment after wind is photovoltaic (PV) followed by biomass with about 8 GW (39 %) and 1.1 GW (5 %) with respective investments of  $\in$ 10.4 bn and  $\in$ 1.9 bn [3]. Fossil fuel is ranked as the lowest with only a 4 % share [4].

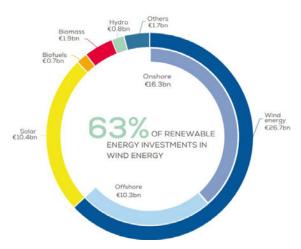

Figure 1.2: Renewable power capacity investments in Europe in 2018 [3]

The generated wind power is highly related to the availability of wind resources. In fact, during peak demand days (winter) up to a third of the energy consumption is serviced by WTs. The wind energy harvesting in urban areas is not straightforward due to lower wind speed resources in comparison with a hilly areas and coastal plains. Being far from urban area increases installation and maintenance costs such as foundations, substations and subsea cables for offshore WTs. In addition, the operation and maintenance (O&M) of WTs contribute a large cost overhead during the wind-farm lifetime. Figure 1.3 shows the capital expenditures associated with an offshore wind farm.

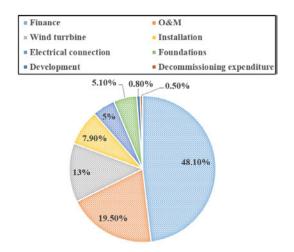

Figure 1.3: Financing costs of an offshore farm in 2015 [5]

'Operation and maintenance' (O&M) is the second largest expenditure (19.5%) with maintenance accounting for 65% of this cost [5]. O&M costs prolong the payback period of WTs [6]. Thus, it is more economically challenging to use a WT as an alternative source of power in remote or difficult locations. Enhancing the reliability of WTs can contribute to a reduction in maintenance costs by reducing the frequency of maintenance visits.

The drivetrain of a WT is a major contributor to the overall maintenance costs. Factors influencing maintenance costs include insurance, design reliability, transport and repair. Among these, design reliability can be improved by the manufacturer. However, it is not possible to achieve a 100% reliable design. Health condition monitoring of critical parts of WTs during operation can increase the chance of observing or detecting precursors to failure and assist in preventing catastrophic failures and reducing operational downtime.

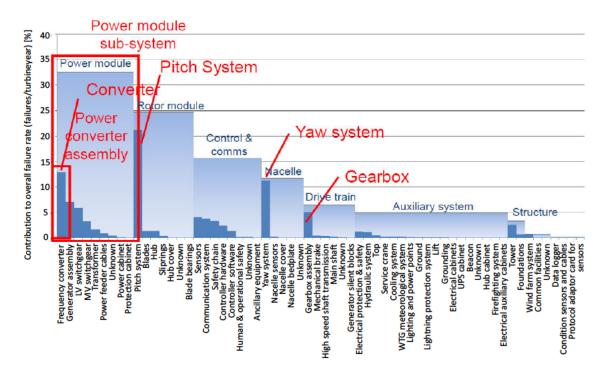

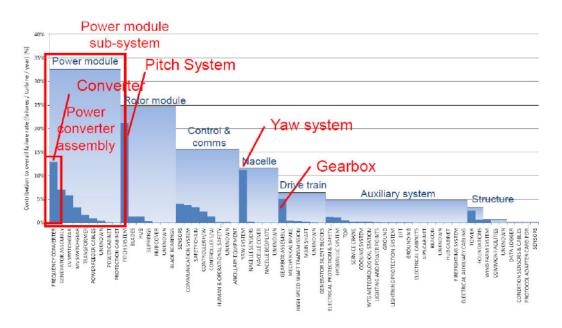

The graph in Figure 1.4 shows the percentage of various failure rates seen in WTs. The highest failure rates in the WT electrical drive train have been experienced in power modules (35%). The pitch system has also experienced relatively high failure rates, 20% [7]. Figure 1.5 shows the overall downtime in different parts of WTs. The power converter contributes the maximum downtime in WTs.

Figure 1.4: Statistical figures for overall failure rates for 350 WTs [8

Figure 1.5: Statistical figures of overall downtime for 350 WTs [8]

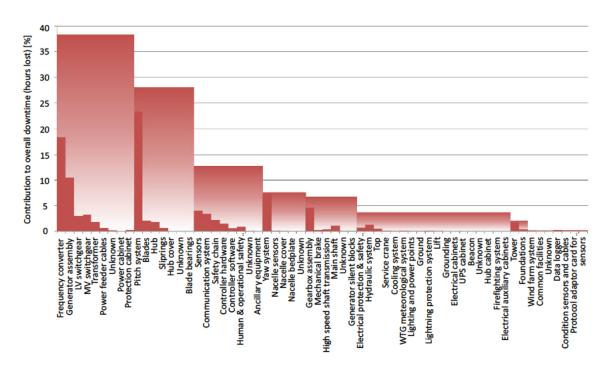

Statistical figures show that electrical systems contribute the majority of downtime and WT failures [8]. The electrical systems consist of generators, power converters and various control systems (such as yaw controller, pitch controller, speed controller, MPPT, rotor side controller, grid side controller). A power converter consists of various component types: semiconductor devices, gate drivers, direct current (DC), DC-link capacitor, resistive and inductive filters, switchgear and a controller. Figure 1.6 shows the typical downtime rates for these parts. Power semiconductor devices suffer the higher rate of failures

(31%), followed by capacitors (20%), and gate drivers (19%). Together these three components make up over half of all failures. Clearly, improving the reliability of the power electronic converters will lead to higher availability of the electrical drive train and hence to reduced downtime of WTs.

Figure 1.6: Distribution of electrical component failures in a WT electrical drive train system [9]

Insulated gate bipolar transistors (IGBTs) are widely used as the semiconductor devices in the power converters owing to their low power losses while carrying high currents at high voltages in comparison with MOSFETs due to the width of their channel region (although at lower voltages a MOSFET has a lower on resistance as the channel region is narrower). However, semiconductor power electronics components are sensitive to temperature and electrical stresses. IGBTs show the highest failure rate amongst converter components [10].

Thermal and electrical stresses mainly originate from load fluctuations that accelerate the degradation of the IGBTs. Because of the variability of wind speed, such stresses frequently arise in WTs and thus there is an interest in improving the reliability. Reliability here refers to the probability that a system will pass a target performance by yielding correct output over the desired lifetime. In other words, WT reliability refers how well a system can perform. As described, the reliability of the IGBT plays a significant role in reducing the downtime of the power electronic converters and hence increasing the converter availability and in turn the WTs. Availability refers to the percentage of time that a system remains operational under normal circumstances. Especially for critical applications where there are unpredictable load conditions. Unpredicted failure causes loss of energy generation and requires unplanned maintenance with consequent downtime. Unplanned maintenance in wind farms results in a high cost penalty [11]. Failure causes unplanned interruption to the power generation and generates unexpected costs.

Maintenance costs of WTs are often significant because of their remote locations. For example, the UK offshore WTs have a reported capacity factor of 50%. Based on this, the turbine expected power for a 5 MW offshore WT per day is 60 MWh. Considering the average base level energy generation price is about £140 per MWh, that equates to £8400 per day [12-13]. Conversely, this figure can be seen as the

daily lost revenue for each non-working 5 MW WT. Maintenance cost is at least £5k for a vessel and one expert human resource. The reported average downtime associated with an offshore WT is 5 days per fault [14]. This is due to remote location of WT, providing the components and organising the trip 5 days×£8400=£42k and plus the maintenance cost (£5k) can be £47k in total.

The typical cost of a WT controller and the health condition monitoring system (from Bachmann and Mita Teknik) is £70k per WT [15]. Considering that a wind farm with 20×5 MW turbines can experience a power converter failure every 2 years (the wind measurement & evaluation programme (WMEP) database specifics to 1.5 electrical failures per WT annually). The licensing of the monitoring system is £4k and sensor replacement costs £1k per WT. From these figures it can be concluded that a health condition monitoring system adds to the complexity and cost of running a WT. However, considering the average WT downtime and relatively low cost of a monitoring system, even if the system prevents one unplanned shutdown the additional system cost will be paid back [16].

Some efforts at the design stage can improve IGBT availability, such as improving the system architecture by including a fault tolerant design. In order to grow the popularity of WTs compared with fossil fuels, it is essential to minimise downtime costs and predict the requirement to replace the parts and hence optimise the maintenance schedule. Health condition monitoring of electrical, mechanical and structural components of a WT has the potential to address this issue [16]. To apply and develop an effective health condition monitoring system, a better understanding of the mechanisms underpinning the progress of damage is essential. A health condition monitoring system refers to the normal set of activities that contribute to the observation of instantaneous state of health of the system/device under study. By the addition on condition monitoring, the maintenance schedule and repair time will be improved. It is important to note that a condition monitoring system does not influence the lifetime or reliability of a component but rather indicates a requirement for the replacement of a degraded component before total failure occurs.

# 1.2 Overview of research methodology

- Calibration of  $V_{CE,on}$  against variations in  $T_j$  and  $i_c$  has been carried out in healthy mode by applying one short pulse in a controlled junction temperature condition.

- Thermo-electrical modelling of the IGBT is done to determine temperature rise in each layer. The IGBT transient thermal model has been tuned based on the experimental results. The same amount of heat flow has been applied to the IGBT model. The case temperature ( $T_c$ ) and substrate temperature ( $T_{substrate}$ ) predicted by the thermo-electrical model are compared with the measured  $T_c$  and  $T_{substrate}$  values.

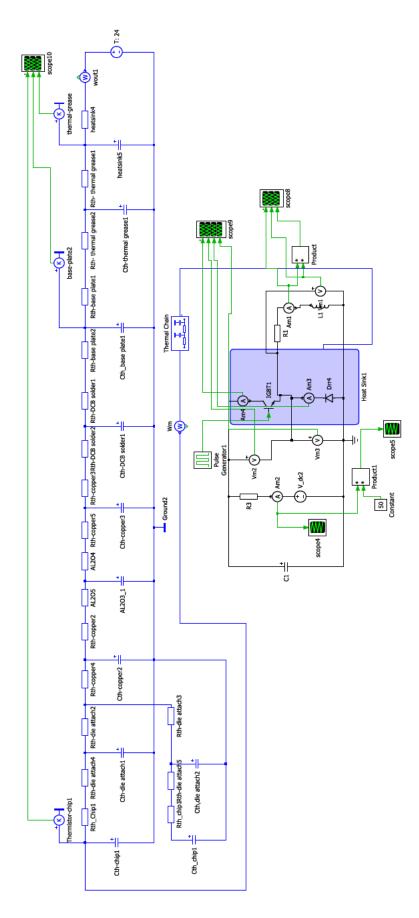

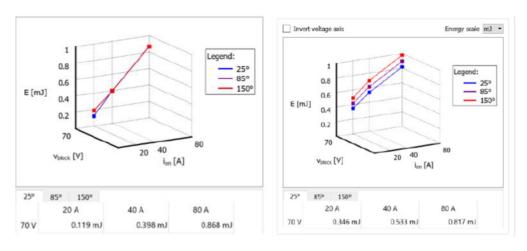

- To detect the progress of SF, the thermal resistance of the junction to case has been estimated by

using Joule heating rules. Power losses are calculated by using a 2D look up tables for conduction

power losses and a 3D look up table for switching power losses.

- A 15% increase in  $R_{th}$  compared to  $R_{th,cal}$  can represent the presence of SF.

- $V_{CE,on}$  is measured with a voltage differential amplifier. The  $V_{CE,on-measured}$  is also compared with  $V_{CE,cal}$ . Deviations can represent the presence of bond wire lift-off.

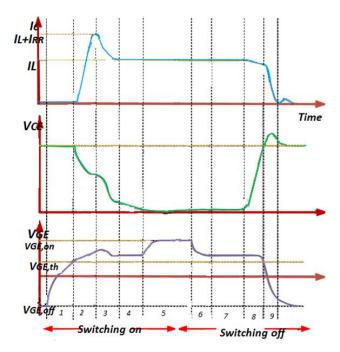

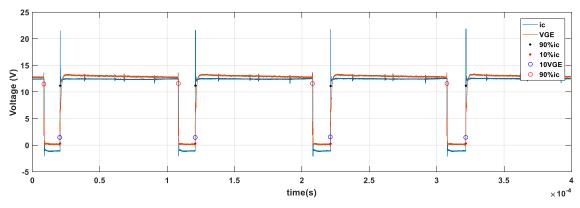

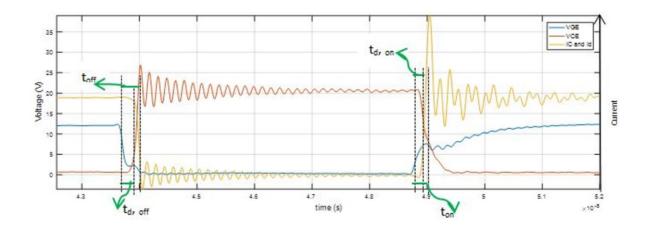

- $T_j$  is estimated from the switching off time  $(t_{off})$ . Time  $t_{off}$  is defined as the interval from  $V_{GE}$  at 90% to when  $i_c$  reaches 10%. To provide the measurement of 90% of  $V_{GE}$  and 10% of  $i_c$ , a state machine process has been developed.

- A wind profile has been applied to the rotor side converter numerically modelled in Simulink to investigate the effect of the fundamental frequency and load amplitude on the IGBT.

#### 1.3 Problem statement

- Proposing effective failure detectors that are sensitive to the progress of the failures and feasibly employable to measure within the operation of three-phase converter.

- Processing the data corresponding to the switching times and developing an accurate state machine to find out 90% and 10% points in  $i_c$  and  $V_{GE}$ .

- Proposing a temperature estimator to be independent of the progress of BWLO.

- Finding the effect of wind speed variations on the failure detectors and junction temperature.

# 1.4 Aim of this research and objectives

The main aim of this Ph.D is to investigate the fault detection of an IGBT used in a WT, bearing in mind the wind speed variations. A list of objectives is given below:

- O1. To find out what are the issues for the existing approach.

- O2. To propose effective electrical failure detectors that are sensitive to the progress of the failures and can be feasibly calibrated in healthy and unhealthy states of the IGBT.

- O3. To find an appropriate method of processing the measured data corresponding to the electrical failure detectors and also to validate the measured data.

- O4. To develop a thermal model of an IGBT in order to find its thermal resistance and thermal behaviour.

- O5. To generate a temperature estimator that is independent of the progress of BWLO in order to independently measure temperature variations from failure.

- O6. To measure and detect early failure mechanisms within the operation of a three-phase converter by the proposed electrical failure detectors.

O7. To numerically model the WT in order to understand the effect of wind speed variations on IGBT.

# 1.5 Original research contributions

With respect to failure detection for an IGBT module used in the power electronic converters, the main research contributions to existing knowledge are listed below:

- 1. Developed a state machine to process switching times within operation of a three-phase-converter

- 2. Developed an 'in-situ' measurement technique to detect premature failures; with an accuracy of detection of one wire lift-off. The technique is practically applicable to WT applications.

- 3. Developed a temperature estimator that is independent of the progress of failure.

- 4. Developed an algorithm that can detect common early failure mechanisms.

#### 1.6 Thesis outline

The thesis is structured to show in detail how the objectives in section 1.4 and the research contributions given in subsection 1.5 have been achieved and how. Chapter 2 provides a brief background on WT electrical drive train systems, power converters and most specifically the IGBT structure and various associated failure modes. Chapter 3 reviews previous research on failure detectors and health condition monitoring technologies to identify gaps in the research knowledge, allowing identification of the specific research to be undertaken for this thesis. Chapter 4 presents the design of the laboratory prototype of a power electronic converter controller.

Chapters 5 and 6 contain the experiment results from detection of a failure mechanism in an IGBT and the corresponding setup. The sensitivity of the proposed failure detectors to the two different failure mechanisms, namely BWLO (Chapter 5) and SF (Chapter 6), are studied and discussed for the calibration setups and in an operating three-phase converter. Chapter 7 presents the WT numerical model, in accordance with the experimental setup presented in the next chapter. Chapter 7 also contains an electrical model of the WT power train using a real wind profile to assess the effects of wind speed variations on IGBT performance. Chapter 8 is a detailed discussion of the outcomes of the research, together with specification of the key contributions to knowledge (novelty) of the work. Chapter 9 concludes the thesis and proposes possible future studies to allow exploitation of this research.

#### 1.7 References

- [1] M. Bhattacharya, S.R. Paramati, I. Ozturk and S.Bhattacharya "The effect of renewable energy consumption on economic growth: Evidence from top 38 countries", Applied energy. Springer Inter Publishing, pp. 733-741, Vol.162, 15th Jan 2016.

- [2] C. Walsh, and I. Pineda, Wind energy in Europe in 2018. Trends and statistics, in 2019 available at https://windeurope.org/wp-content/uploads/files/about-wind/statistics/WindEurope-Annual-Statistics-2018.pdf

- [3] G. Resch, et al. "Assessment of Policy Pathways for Reaching the EU Target of (At Least) 27% Renewable Energies by 2030", The European Dimension of Germany's Energy Trans. Cham: Springer Inter Publishing, pp. 45–65, 2019, doi: 10.1007/978-3-030-03374-3\_4.

- [4] M. Aly, E. Ahmed, and M. Shoyama, "Thermal and Reliability Assessment for Wind Energy Systems With DSTATCOM Functionality in Resilient Microgrids," IEEE Transon Sustainable Energy, vol. 8, no. 3, pp. 953 965, Dec, 2016.

- [5] Shipurkar, "Improving the availability of WT generator systems", 2019.

- [6] WindEurope Report, 201, in 2018. available at https://windeurope.org/wp-content/uploads/files/about-wind/statistics/WindEurope-Annual-Statistics-2018.pdf [7] EREC, 'Renewable energy technology roadmap 20% by 2020'.

- [8] M. Wilkinson and B. Hendricks, "Reliawind Deliverable D.1.3 Reliability Profiles Results," 2007.

- [9] P. Tavner, B. Hahn, S. Faulstich, "Eliability & availability of WT electrical & electronic components', Jan 2011.

- [10] Y.Avenas, L.Dupont and Z.Khatir "Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters-a review", IEEE Trans on Power Electro, Vol.27, (6), Jun 2012, pp. 3081-3092.

- [11] GL Garrad Hassan, "A guide to UK offshore wind operations and maintenance," Scottish Enterp. Crown Estate, p. 42, 2013.

- [12] S. Konaklieva "Power Module Condition Monitoring for Offshore Wind Applications with Focus on the Die Attach Degradation" PhD thesis, University of Warwick, 2017.

- [13] L. Ran, S. Konaklieva, P. McKeever and P. Mawby, "Condition Monitoring of Power Electronics for Offshore Wind" DOI: 10.1049/etr.2014.0004, IET journal in Engineering & Technology, 2014.

- [14] L. Ran, S. Konaklieva, P. Mawby, and P. McKeever, "Condition Monitoring of Power Electronics for Offshore Wind", IEEE Trans, Jun 2014, pp 1–10.

- [15] The Crown Estate, "A Guide to an Offshore Wind Farm," 2010.

- [16] S. Sheng, "NREL/PR-5000-59111," NREL, Jun 2013, available at https://www.nrel.gov/docs/fy13osti/59111.pdf.

- [17] R. Moeini, P. Tricoli, H. Hemida and C. Baniotopoulos, "Increasing the reliability of WTs using condition monitoring of semiconductor devices: a review", IET, RPG conf, Sept 2016.

# Chapter 2: Review of condition monitoring of power converters for wind turbines

#### 2.1 Introduction

WTs convert a proportion of the kinetic energy of wind into electrical energy using electrical generators [1]. The electrical systems and control algorithms used to convert the wind energy to electricity are discussed in this chapter. Due to wind speed variations, WT electrical systems will encounter diverse load swing variations. These load swings will reduce in the expected lifetime of the semiconductor 'power-switch' component (IGBT), used in the power converters. The ability of the lifetime can result in an unplanned halting of the system. Health condition monitoring can help to identify premature failure of the IGBT and predict the time remaining to failure. To design and implement an effective condition monitoring system it is essential to understand failure mechanisms and their root causes. The structure of IGBTs and different failure modes are discussed in this chapter.

# 2.2 Electric drive train system of a wind turbine

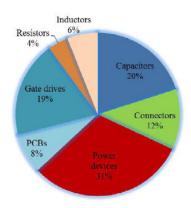

Wind energy passing a WT causes the blades to produce torque on a main shaft that is then converted into electrical power. The main WT shaft rotates the rotor of an electrical generator either directly, or indirectly by means of a gearbox. The foundations, the design of the blades and the mechanical structure of the WTs are not of concern in this thesis. The main electrical drive system mainly comprises the generator, power electronic converters and their controller systems, an electric breaker, pitch angle controller, yaw motor and its driver and actuator. The focus of this thesis is on the electrical drive train system and most specifically on the power electronic converters and their control system. This is because the control system defines the operation strategy of the power converter. For example, the pitch angle controller can keep the generated power constant, so constant thermal stresses are applied to the IGBTs of the power converter despite changes in wind speed; this will discussed further in chapter 7. This subsection describes the electrical parts of the electrical drive train of WT in terms of efficiency

and potential maintenance costs. The drive train system of the WT is located in a nacelle that houses all of the generating components in a WT. The nacelle is connected to the hub where the blades are attached. The drive train can be divided into two sections: the mechanical and electrical drive system [2], shown in Figure 2.1.

Figure 2.1: A horizontal axis WT (left) and schematic of the turbine's blade assembly and nacelle (right) [3]

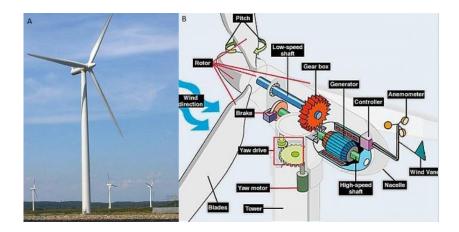

#### 2.3 Electrical drive system of wind turbines

Three types of electrical power generator are typically found in WTs:; squirrel-cage induction generators (SCIGs); doubly-fed induction generators (DFIGs); and permanent magnet synchronous generators (PMSGs). They are classified in Figure 2.2.

Figure 2.2: Most common classification of WT according to their generator types

#### 2.3.1 Fixed-speed wind turbines

SCIGs without power electronic converters are used for fixed-speed WTs directly connected to the grid [4]. A block diagram of this type of WT is shown in Figure 2.3. The SCIG speed can change by only a few percent because the torque-speed characteristic of SCIGs is steep around the synchronous speed, so the pull-out torque (that guarantees stability) is close to the synchronous speed.

Figure 2.3: Diagram of fixed-speed WTs, using SCIG

The drivetrain consists of a mechanical section (a variable-ratio gearbox and a mechanical breaker) and an electrical section (electrical generator, reactive power compensator and transformer). The generator requires a higher shaft speed than the WT rotor produces so a gearbox is required. The gearbox is essential because wind speed variations lead to mechanical rotational speed fluctuations and thus to variations in electrical power output. These variations yield voltage fluctuations at the point of connection to the grid. Fixed-speed WTs draw varying amounts of reactive power from the grid. Therefore, in these types of WT, a capacitor bank is used to compensate reactive power.

The fixed-speed type of WT is cost-effective, especially for small and medium systems. However, its best efficiency (optimum tip speed ratio) occurs over a rather limited range of wind speeds [5]. The tip-speed ratio ' $\lambda$ ' for a WT is the ratio between the tangential speed of the tip of WT blade and the actual speed of the wind speed ( $\nu$ ). The tip-speed ratio is related to efficiency, with the optimal value varying with blade design in equation (2.5). Furthermore, a fixed-speed WT requires an electrically stable grid as a load and the mechanical drive train needs to withstand the high mechanical stresses caused by wind gusts and turbulent flow.

$$\lambda = \frac{\omega \cdot R}{\nu} \tag{2.5}$$

where  $\nu$  is the wind speed, R is the rotor radius and  $\omega$  is the rotational speed.

#### 2.3.2 Variable-speed wind turbines

Variable-speed WTs can operate at peak electrical efficiency over a wide range of wind speeds. Both asynchronous and synchronous generators can be used for these types of WT in combination with back-to-back power converters (AC to DC and DC to AC converters). The use of a back-to-back converter enables a WT to maximise the generated electrical power by implementing maximum power point tracking (MPPT) strategies [6]. To extract maximum power from the wind (between cut-in and rated speed) the WT shaft speed is varied so that the optimum tip-speed ratio is achieved. MPPT is a control strategy that is applied when the wind speed is equal or below the rated speed of the WT by generating appropriate reference voltage for DC power bus voltage before the DC to AC converter associated with

the wind speed. WTs have to be designed to withstand extreme wind speeds that will naturally occur from time to time.

A WT can survive in a storm, but the blades do not turn and no electricity is generated. Indeed, if the wind speed exceeds the cut-out speed for the WT, brakes are applied to bring the WT blade rotation to a halt. Wind speed is measured with the anemometer located at the top of the WT nacelle. At wind speeds between the rated and cut-out speeds, two methods can be used to control the power. One is the active 'pitch controller' method and the other is the passive stall/'soft stall' method, also known as active stall. Figure 2.4 illustrates the power output for the two types of pitch control. The purple dashed line links the maximum power points for each speed.

Figure 2.4: Power control in different range of wind speed [7]

The presence of a pitch controller means that there is a control system that can vary the pitch angle of turbine blades so as to decrease the torque produced by the blades in a fixed-speed turbine or to decrease the rotational speed in variable-speed turbines. Power output can be kept at the rated power by adjusting the pitch angle of the blades [8]. When the wind speeds are above the rated speed (but below the cutout speed), the blades will rotate so that there is less lift and more drag due to increasing flow separation along the blade length. This will slow down the rotational speed or the torque transferred to the shaft so that the rotational speed or the torque is kept constant below a set threshold. A WT with a pitch controller increases its power output with increasing wind speed, up to the rated wind speed, then as the wind speed increases to the cut-out speed, the pitch is controlled and the power remains constant. The pitch controller communicates with the converter controller to monitor the generator speed and power output. A reference pitch angle is determined based on the generator speed and average wind speed. The output of the pitch angle controller is fed to a mechanical drive system to adjust the blade pitch angle through actuators.

A passive stall system is a control system where the blades are designed so that when wind speed is too high, the rotational torque is automatically reduced by aerodynamic effects. The power decreases with increasing wind speeds due to aerodynamic effects on the turbine blades (regions of the blade are stalled, transmitting from the hub and outwards with increasing wind speeds). Blades are designed so that they will perform with inferior quality (in terms of energy extraction) in higher wind speeds to protect the WT without requiring active controls [9]. Active stall/soft stall refers to when the rotor speed is actively regulated to ensure a reduction of the torque. Power electronic converters are used (where required) to connect power generated by the WT generator to the grid supply via a transformer. Power electronic converters have two stages with an intermediate DC-link [10]. A block diagram in Figure 2.5 shows a typical variable-speed WT. The two converters communicate with each other and with the grid to keep the DC-link voltage constant.

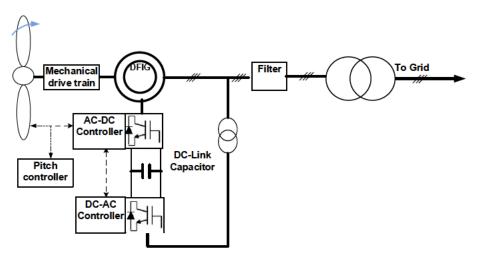

Figure 2.5: Simplified block diagram of variable speed WTs including back-back converter

Two important control functions are carried out by the AC to DC converter, and two others by the DC to AC converter. The DC to AC converter, the grid side converter, controls the DC-link voltage and the reactive power exchanged with the grid. The AC to DC converter, the rotor side converter, controls the torque and flux of the generator. DFIGs and PMSGs are used for variable-speed WTs [11]. Both DFIG and PMSG types are combined with power electronic converters to generate electrical power with a larger range of wind speeds than a fixed-speed WT. Power electronic converters also help to satisfy grid regulations (synchronous frequency and voltage regulation requirements) when integrating with the grid. DFIGs are more efficient for high, steady wind conditions, but have lower efficiency at low speeds as more current must be injected into the rotor [12]. A brief explanation of different types of WTs are given in the following subsections, including a discussion of their advantages and limitations.

# 2.4 DFIG type of wind turbine

DFIG is commonly found in variable speed WTs produced since the late 1990's. Currently, 57.5% of the variable WTs are equipped with DFIG [13]. Vesta V90, Gamesa G80 and GE1.5 models are examples of this type of WT [14]. DFIG is also extremely popular to use in medium power WTs, rated below 2 MW. The electric drive train of a WT with a DFIG is shown in Figure 2.6. A DFIG has a stator winding that is directly connected to the grid, while the rotor windings are supplied by a power converter. For this reason, this type of generator is called 'doubly-fed' because both stator and rotor

windings are energised. The "opti-slip" feature allows the generator to have a variable slip and to choose the optimum slip, reducing fluctuations of the torque and power output [15].

The rated power of the power electronic converter is smaller for this type of WT than that found in a PMSG or SCIG with similar power. The reason is that the converter is connected to the rotor which typically only sees 30% of the generator rated power [16]. When the stator excitation is applied, a voltage will be generated at the output terminals of the rotor circuit. The rotor-side converter (RSC) provides the excitation for the induction machine. With this converter it is possible to control the torque and hence the speed of the DFIG and also the power factor at the stator terminals. The rotor-side converter provides a varying excitation frequency depending on the wind speed. In a DFIG designed for high-speed, a slow-turning shaft from the rotor (10-20 rpm) drives a gearbox with its output shaft rotating up to 2000 rpm, and this drives the generator. This type of WT is equipped with a gearbox [17].

The gearbox is used to convert low speed rotations from the rotor shaft to the higher speed rotation that is required to generate initial torque for the induction generator. Generally, the DFIG requires a gearbox to adjust the generator speed so that tip speed ratio is kept constant at MPPT. Using a gearbox adds to the maintenance costs of the SCIG and DFIG WTs. These requirements and limitations mean turbine manufacturers have been recently looking to PMSG technology as the most promising type for medium and low power WTs [18].

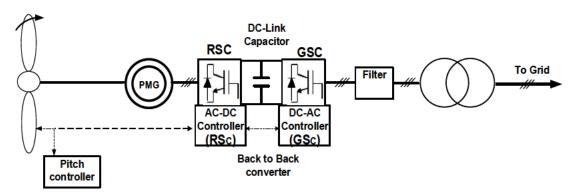

Figure 2.6: Diagram of a variable speed WT with a DFIG

## 2.5 PMSG type of wind turbine

PMSGs are becoming increasingly popular amongst manufacturers as they are looking to enhance the reliability and serviceability of WTs by avoiding the need for a gearbox. Currently almost 40% of WTs are equipped with PMSGs [19]. The largest manufacturer of this type of electrical drive train system are Enercon and Gold Wind [20]. For medium power WTs, (2-3 MW) direct drive using PMSGs is

extremely popular. However, they are less popular for larger WTs because of their requirements for large and expensive rare earth NdFeB magnets.

It should also be noted that the power efficiency and density of PMSGs are remarkably higher than those of SCIGs and DFIGs as there is no need for an excitation current. An electrical drive train system of this type is shown in Figure 2.7. The power electronic converter is connected to the stator winding and the electrical machine is excited by its rotor magnets.

Figure 2.7: Diagram of a variable speed WT with a PMSG

For a PMSG there is no need for any excitation current since the magnetic field is generated by rotor magnets. Comparing the DFIG type to a PMSG, the DFIG is more economical because of the smaller rated power of power electronic converters and the absence of permanent magnet materials. However, PMSGs can be controlled more easily to cope with a wide range of wind speeds while controlling reactive power. In fact, for a PMSG reactive power can be fully adjusted for all speeds, whereas the reactive power in a DFIG is determined by wind speed.

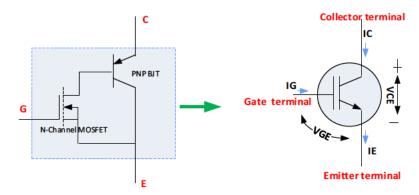

#### 2.6 IGBT module

All embedded controllers in the converters and pitch angle controllers are integrated through controlling pulse signals sent to active semiconductor devices, such as insulated gate bipolar transistors (IGBTs). These switches can be switched 'on' and 'off' to set the electric drive train systems output to the desired voltage and frequency. This section gives some details of the power semiconductors typically found in WT power converters. IGBTs are the semiconductor devices of choice for high voltage applications due to their low on-state losses [21]. For a gate voltage below the threshold value, (typically in a range of 8-10 V), IGBTs do not conduct any significant current and, hence, they are off. Above the threshold value, the control current varies based on the gate voltage. Rated current is conducted when the gate voltage reaches approximately 12-15 V. It takes some time for IGBTs to transition from off-to-on and on-to-off. Internal capacitances of IGBTs affect the 'turn-on' and 'off' times of the IGBTs. These transition times, called the turn-on and turn-off times, are important for power losses (see chapters 5

and 6). IGBTs have three terminals: the 'gate', 'collector' and 'emitter'. The equivalent circuit of an IGBT is shown in Figure 2.8 [22].

Figure 2.8: An N-channel IGBT equivalent circuit

#### 2.7 IGBT structure

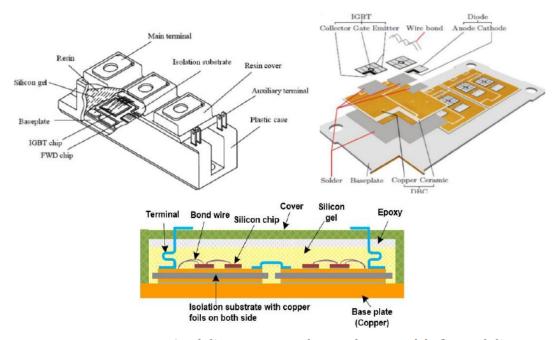

IGBTs are broadly used because of their efficient switching performance combined with relatively low conduction losses. IGBTs are made in different sizes, shapes and functionalities. IGBTs are becoming more compact, cost effective and reliable. The popularity of IGBTs in WTs as switching devices is due to higher efficiency and the capability for handling higher currents. Their multi-layer structure with several materials offers a higher mechanical stability, electrical insulation and adequate thermal conductivity [23]. Figure 2.9 shows 3D views of an IGBT module and its structure.

Figure 2.9: A 3-D view (top-left), cross section of a typical IGBT module (bottom-left) and IGBT layers (top-right) [24]

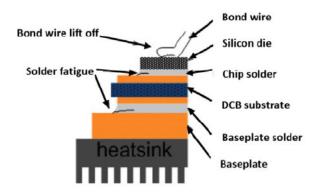

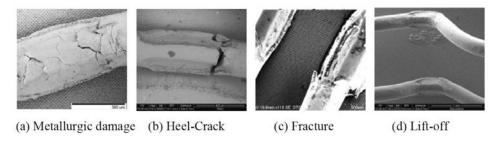

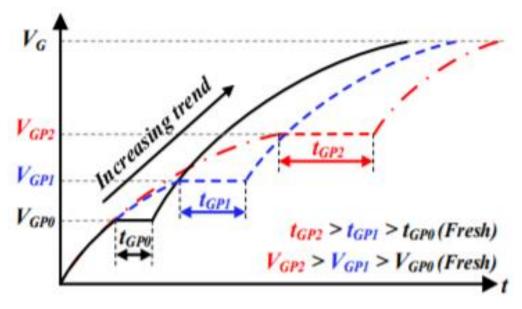

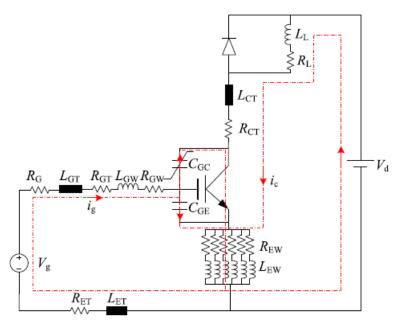

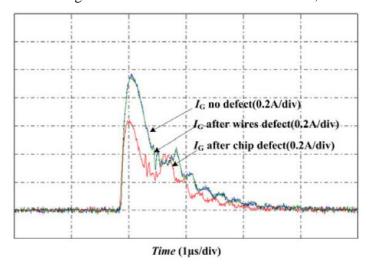

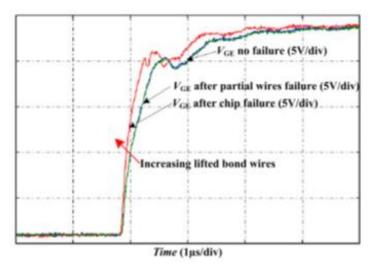

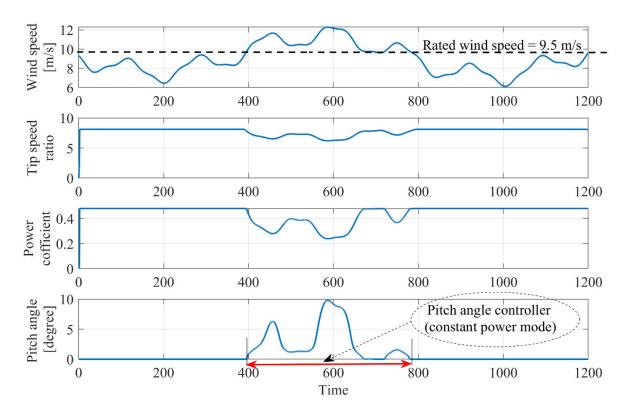

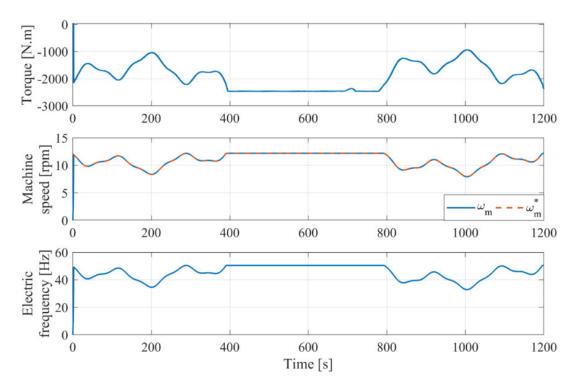

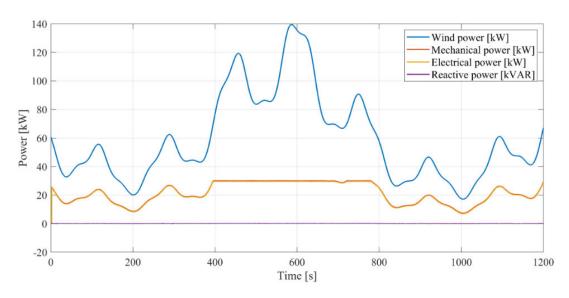

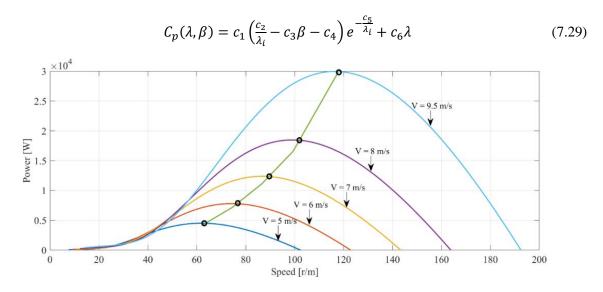

The structure consists of a plastic case connected to a baseplate. A direct copper bonded (DCB) ceramic substrate is soldered to the baseplate of the IGBT module and the IGBTs and diodes (fabricated on silicon chips) are soldered to the DCB. Aluminum bond wires are commonly used to connect the upper side of the silicon chips to the substrates as well connecting the substrates to the terminals. Table 2.1 lists the IGBT parts with their thermal expansion coefficients [25]. A description of three main different layers, i.e metallization and bond wires, DCB substrate, die-attached and solder joint are described below.